数字电路设计组合循环

问题

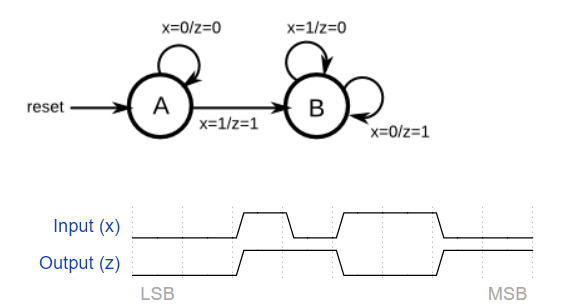

今天在做一个小设计的时候遇到一个问题,设计的目的是实现串行计算2的补码,用mealy型状态机实现:

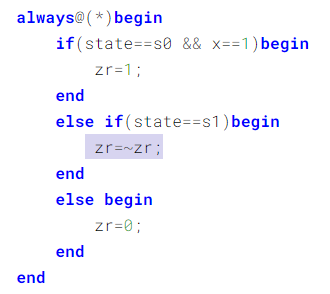

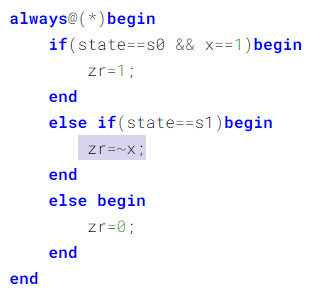

在rtl coding时如果组合逻辑输出用这样的写法,仿真就会报错

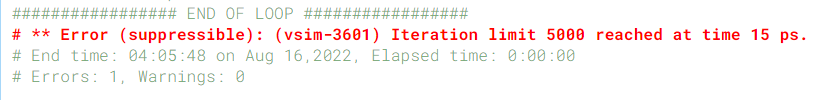

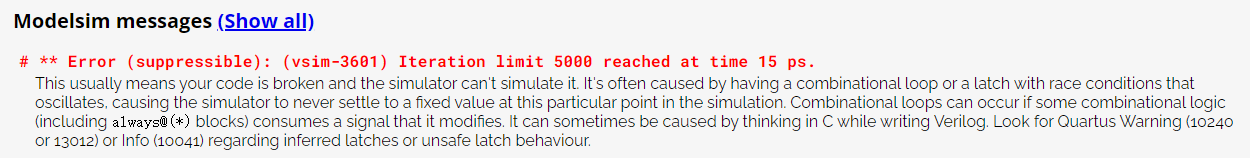

这里modelsim卡在循环了,看进一步的描述

这里解释了原因是产生了组合循环或者latch锁存器中有竞争条件,导致仿真器无法确定某一个仿真时刻的固定值,电路无法稳定到一个数值上。组合循环一般是由于某些组合逻辑使用了它修改的信号。

其实就是组合逻辑的输出(即门之间没有寄存器的逻辑部分)被反馈到该组合逻辑的输入而没有中间寄存器。这种设计需要避免,我的目的是对输入进行反转,因此不能像时序逻辑设计那样写代码。

解决方案

改变代码后便可以通过测试了

1 module top_module ( 2 input clk, 3 input areset, 4 input x, 5 output z 6 ); 7 reg state,nstate; 8 reg zr; 9 parameter s0=1'b0,s1=1'b1; 10 11 always@(posedge clk or posedge areset)begin 12 if(areset)begin 13 state <= s0; 14 end 15 else begin 16 state <= nstate; 17 end 18 end 19 20 always@(*)begin 21 case(state) 22 s0:nstate=x?s1:s0; 23 s1:nstate=s1; 24 default:nstate=s0; 25 endcase 26 end 27 28 always@(*)begin 29 if(state==s0 && x==1)begin 30 zr=1; 31 end 32 else if(state==s1)begin 33 zr=~x; 34 end 35 else begin 36 zr=0; 37 end 38 end 39 40 assign z= zr; 41 42 endmodule

这里仅仅改动了这一部分

参考资料

https://support.xilinx.com/s/question/0D52E00006hpWLASA2/what-is-combinational-loop-?language=en_US

https://blog.csdn.net/weixin_43755290/article/details/104656467