关于阻塞赋值综合的电路是怎样的

1. 仿真分析

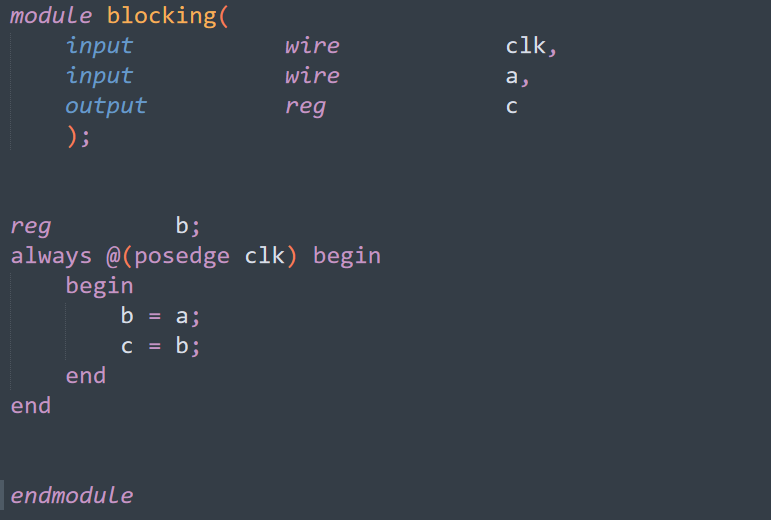

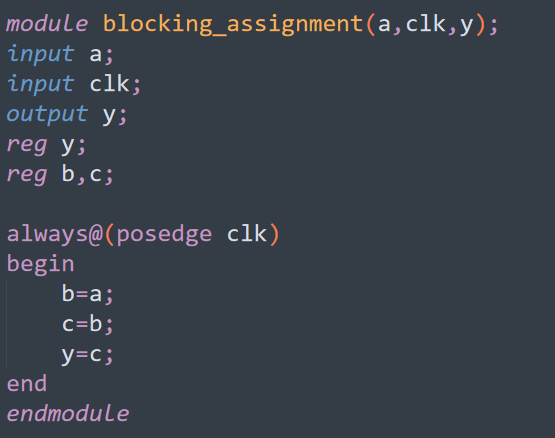

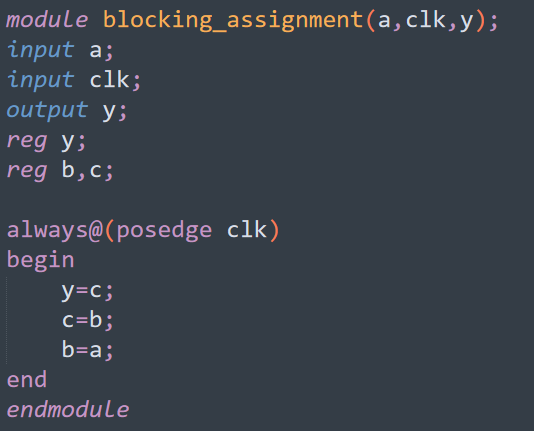

在时序逻辑中使用了阻塞赋值的代码,综合后的电路是怎样的呢?

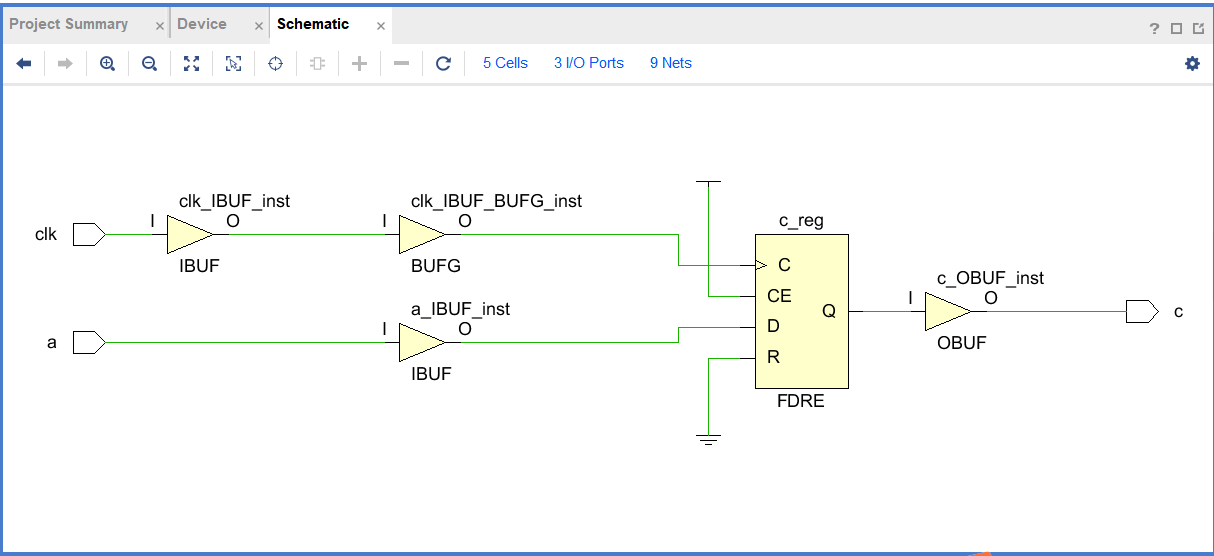

下面用vivado进行综合实现看看效果:

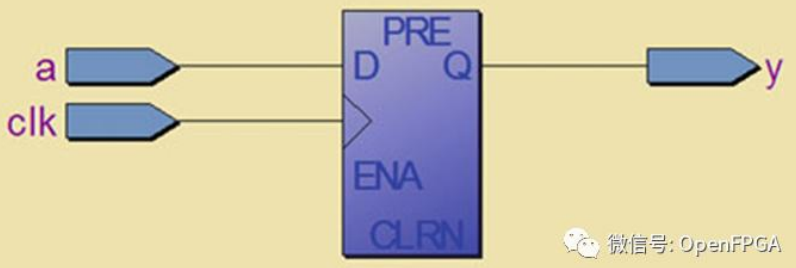

可以看出这里中间变量b被优化掉了,直接由寄存器c进行输出。但是还是要遵循代码规范,在时序逻辑建模中使用非阻塞赋值!

而modelsim进行功能仿真结果是怎样的呢?

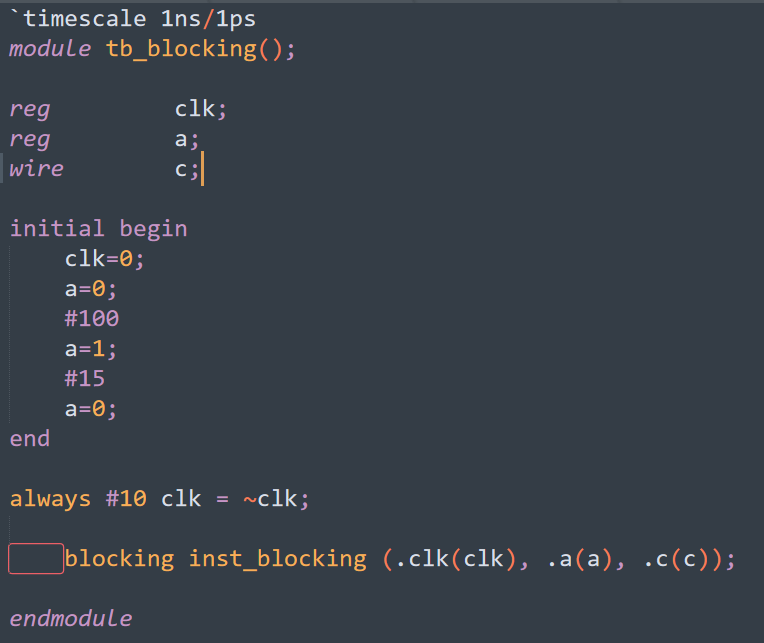

下面进行一个简单的测试:

简单的tb代码

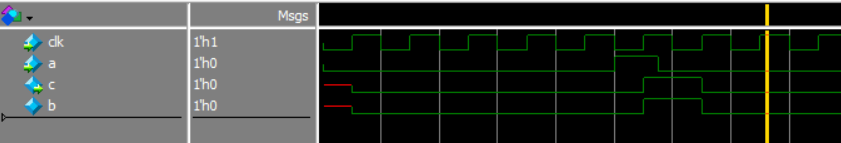

波形图如下:

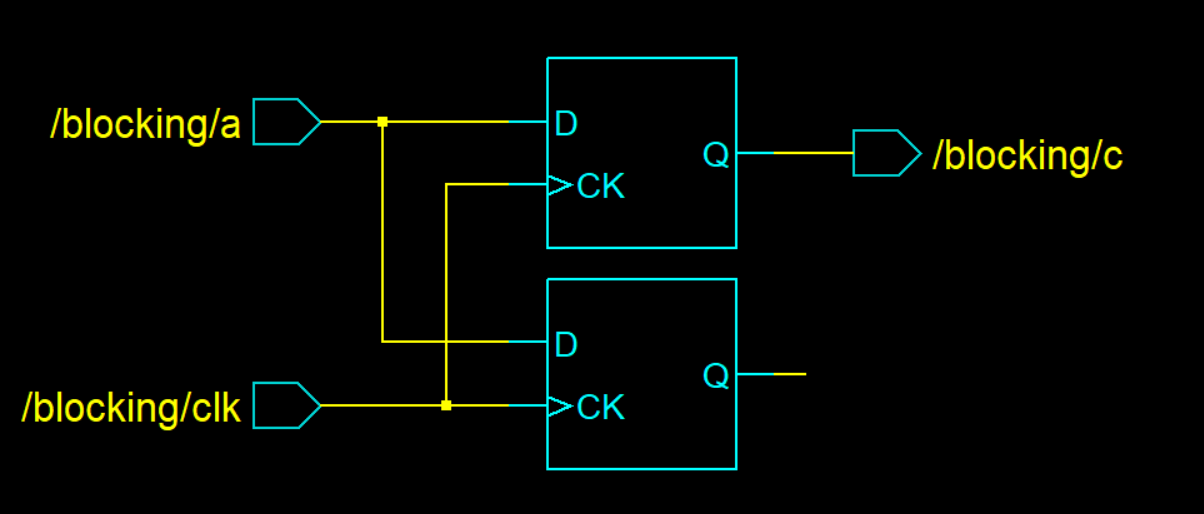

可以看出b在上升沿更新了,而c与b的结果一样,而modelsim中的电路图也是非常有意思:

可以看出直接是把b端的输出悬空了,a直接赋值给c

这里需要在modelsim中查看视图的话,可以从View的shcematic中查看。同时在命令行中输入 vsim -debugdb work.<程序名>

2. 理论分析

如果阻塞赋值用于描述时序逻辑,并且在同一“always”程序块中使用多个分配,则预期需求可能与综合逻辑匹配,也可能与综合逻辑不匹配。原因是,在阻塞分配中,所有后续语句(下一个立即数)都被阻塞,除非直到当前语句被执行。这将导致硬件截断,并可能推断出不需要的综合输出。

需要记住的重要一点是,程序“always”块中的阻塞赋值语句的顺序是综合中的决定性因素!!!

上面对应的代码综合后的电路如图,可以看出推断为一个寄存器:

而如果代码更改顺序后

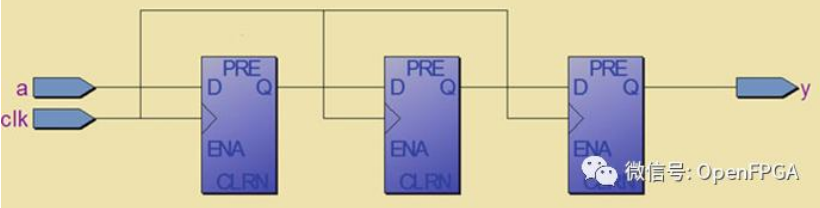

综合将推断出三个寄存器: