奇偶校验及verilog实现

引言

奇偶校验Parity Check,即判别一组二进制码中1的个数为奇数或偶数的校验方法。奇校验即1的个数为奇数,偶校验即1的个数为偶数。发送方在发送前需要事先规定好哪种形式的校验,便于接收方进行解校验。

接收端接到数据后再次进行校验,通过判断1的个数来确定传输是否正确。

以一个8bit传输为例,并规定奇校验,发送方8‘b00001111发送出去,1的个数为4,因此附加的校验位为1,这样1的总数就是5(奇数)了。最后发送的数据为9‘b000011111(最后一位为校验位)。

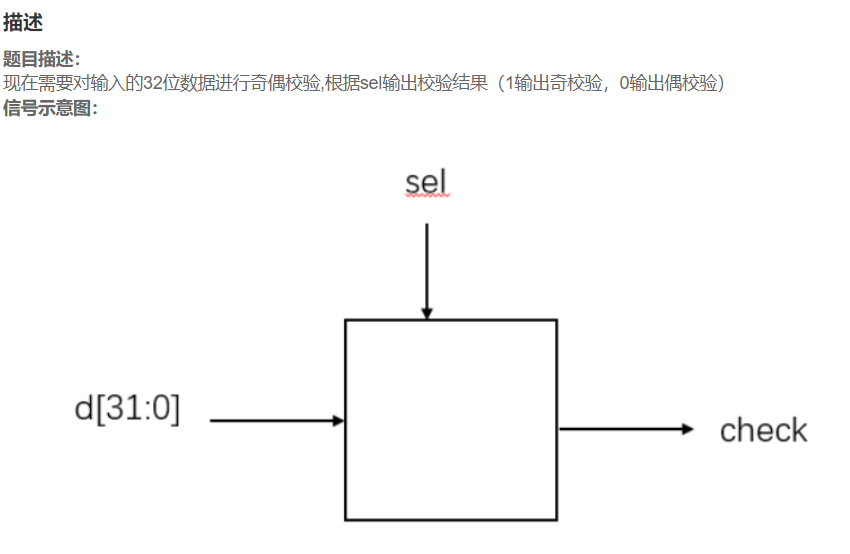

例题

这里以牛客网的一道例题来解释

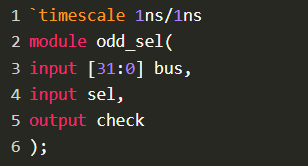

端口为

输出check为1代表校验正确(不过题目这里没提示,是我猜测的输出,验证是正确的)。

首先给出一个复杂的设计方法...

设计一,化简为繁

1 `timescale 1ns/1ns 2 module odd_sel( 3 input [31:0] bus, 4 input sel, 5 output check 6 ); 7 //*************code***********// 8 reg [5:0] one_num; 9 reg check_r; 10 integer i; 11 12 assign check = check_r; 13 14 always@(*)begin 15 one_num = 0; 16 for(i=0;i<=31;i=i+1)begin 17 if(bus[i]==1'b1)begin 18 one_num = one_num+1'b1; 19 end 20 end 21 end 22 23 always@(*)begin 24 if(sel==1'b1)begin 25 check_r = one_num[0]==1'b1 ? 1'b1 : 1'b0; 26 end 27 else if(sel==1'b0) begin 28 check_r = one_num[0]==1'b0 ? 1'b1 : 1'b0; 29 end 30 else begin 31 check_r = check_r; 32 end 33 end 34 35 //*************code***********// 36 endmodule

这里的思路是首先检测出输入数据中1的个数,然后根据计数值最低位为1或0表示1的个数为奇数或是偶数来判断输出。思路很简单,资源很要命!

不过这里用到了之前一篇文章介绍的办法用来计算输入数据中1的个数,算是个小应用吧。

设计二,真正的好办法

1 `timescale 1ns/1ns 2 module odd_sel( 3 input [31:0] bus, 4 input sel, 5 output check 6 ); 7 //*************code***********// 8 9 wire flag; 10 assign flag = ^bus; 11 12 assign check = sel ? flag : ~flag; 13 14 //*************code***********// 15 endmodule

这里的关键点是按位异或^bus,可以计算出输入数据中1是奇数(结果为1)还是偶数(结果为0),非常简单的描述。

另外按位与&bus可以判别输入数据中是否含有0,按位或|bus可以判别输入数据中是否含有1。都是非常有用的描述方式。

分类:

Verilog HDL

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 无需6万激活码!GitHub神秘组织3小时极速复刻Manus,手把手教你使用OpenManus搭建本

· Manus爆火,是硬核还是营销?

· 终于写完轮子一部分:tcp代理 了,记录一下

· 别再用vector<bool>了!Google高级工程师:这可能是STL最大的设计失误

· 单元测试从入门到精通