Verilog memory类型数据

引言

verilog中具有多种数据类型,当我们用reg类型元素构建一维数组时,这时候的变量也称之为memory。可以用于模拟只读存储器(ROMs)或随机存取存储器(RAMs)或者寄存器堆(regfiles)。

数组中的每个reg被称为元素或字,由单个数组索引来处理。

赋值等操作

一个n-bit的reg可以在单个分配中赋值,但完整的memory内存不能这样赋值。要对memory的字进行赋值,必须要指定一个索引。索引可以是一个表达式,这样有利于数据的访问。比如,计算机的程序计数器(program counter)的reg值可以作为索引去访问RAM。

在之前的文章同步FIFO中,对ram进行初始化就是使用for循环对位宽为8,深度为8的ram赋值0。这里的深度就是每次操作需要的索引。

数组声明

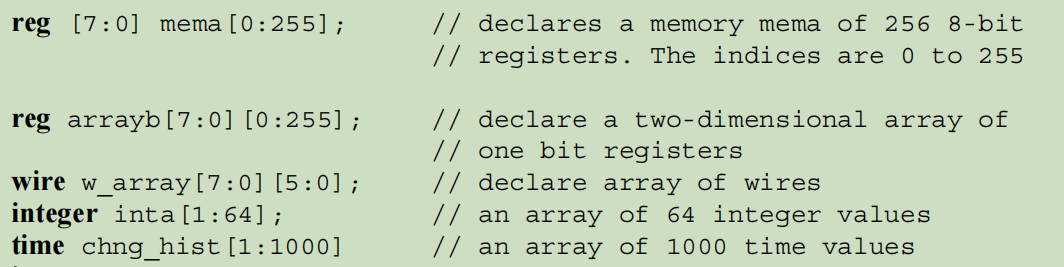

下图中第一个声明是表示一个memory,但是第二个数组arrayb是一个二维数组,位宽为1。这里需要区分。

第三个声明是线网变量的阵列。

声明的合法性

下图的声明是对上图声明变量的赋值,可以看出对memory进行整体赋值是非法的!

而第二个声明也是非法的,对于二维数组不可以只声明第一维度,第二维度也要表明。

第4,5条声明是正确的,可以与上面3条进行对照。

访问数组元素(system verilog扩展)

可以用数组索引引用未压缩数组的每个元素,多维数组需要多组方括号来选择数组中的单个元素:

logic [15:0] mem [0:4095];

data007 = mem[7];

real lookuptable [0:15] [0:15];

lookuptable [0] [15] = 2.15;

数组索引也可以是网络或变量的值:

always_ff @(posedge clk)

data <= mem[address];

数组元素的位选择和部分选择(system verilog扩展)

可以从数组元素中选择一位或一组位。但必须首先选择数组的单个元素,然后再进行位选择或部分选择。

logic [15:0] mem [0:4096];

logic [15:0] data;

logic [3:0] nibble;

logic lsb;

data = mem[5];

lsb = mem [5] [0];

nibble = mem [5] [11:8];