FPGA时序约束--Input Delay

输入延时定义

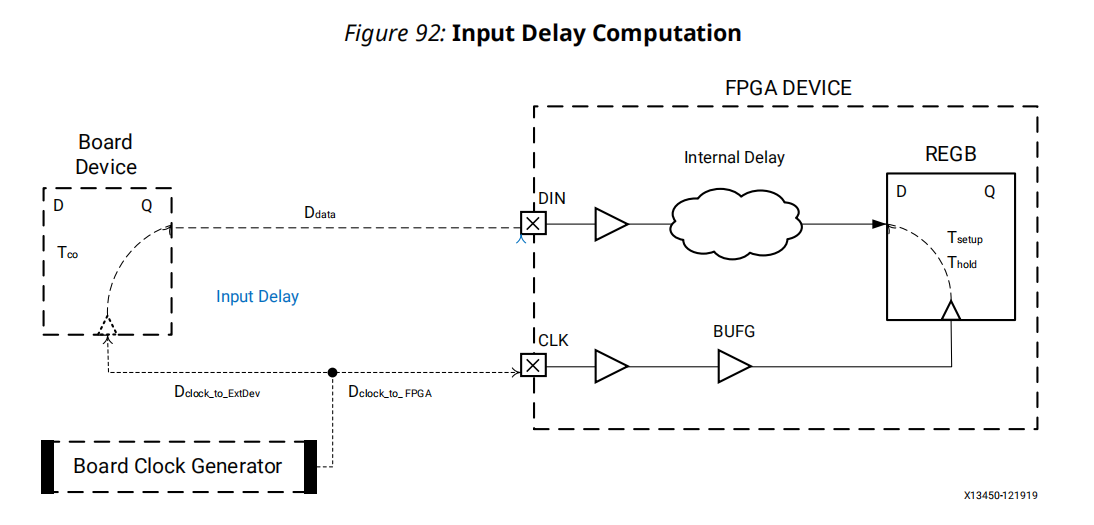

输入延时指的是数据相对于器件接口时钟的延时信息,对应于从时钟发射沿,经过时钟路径延时,外部器件延时和数据路径延时到达FPGA器件端口的时间关系。

结合下图来看

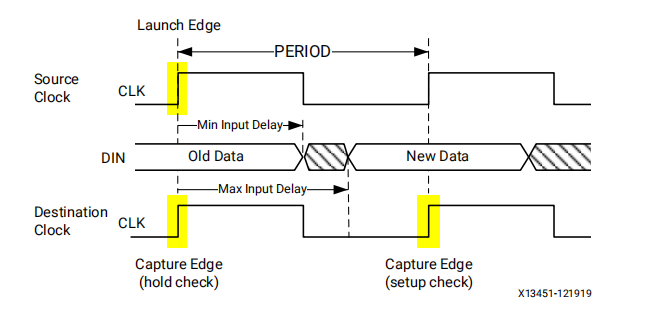

最大延时与最小延时分别为:(最大延时用于分析建立时间,最小延时用于分析保持时间)

![]()

输入延时 = 从时钟源出发经过时钟到外部器件延时Dclock_to_ExtDev + 板级器件的延时Tco + 数据延时Ddata - 时钟源到FPGA的延时Dclock_to_FPGA

约束、时序解释

![]()

这里的约束表明相对于系统时钟sysClk而言最大输入延时为5.4ns,最小输入延时为2.1ns

因此综合工具会根据约束对时序进行一定调整,使得进入FPGA器件的数据和时钟保持相对稳定的关系。

参考

Xilinx ug949-vivado-design-methodology

浙公网安备 33010602011771号

浙公网安备 33010602011771号