计算机组成与设计-除法器

引言

算术运算中的加减乘除,乘法和除法是比较难以实现的。乘法之前已有总结,这次学习的部分是除法器的设计和实现。同样,MIPS指令忽视了上溢的情况,因此软件需要检测商是否过大。另外不同于乘法的一点,对于除法运算软件还需要检测是否除以0,以避免产生错误的结果。

无符号除法器ver.1

除法运算中的关键表达式:被除数 = 除数 × 商 + 余数

首先用笔算的计算来推导硬件的设计思路:

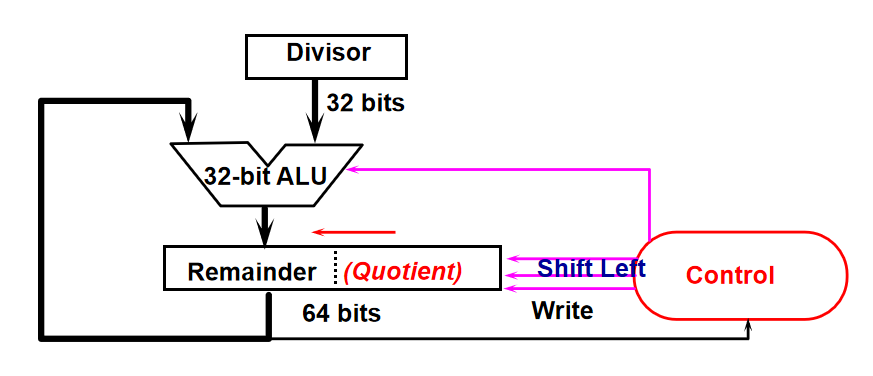

其硬件结构如图所示:

初始时商置为0,除数每次计算后右移一位以对准被除数,因此初始时位于64位移位寄存器的左端。余数寄存器初始为被除数。

这个版本的除法器ALU,除数移位寄存器和余数寄存器都是64位,只有商是32位。

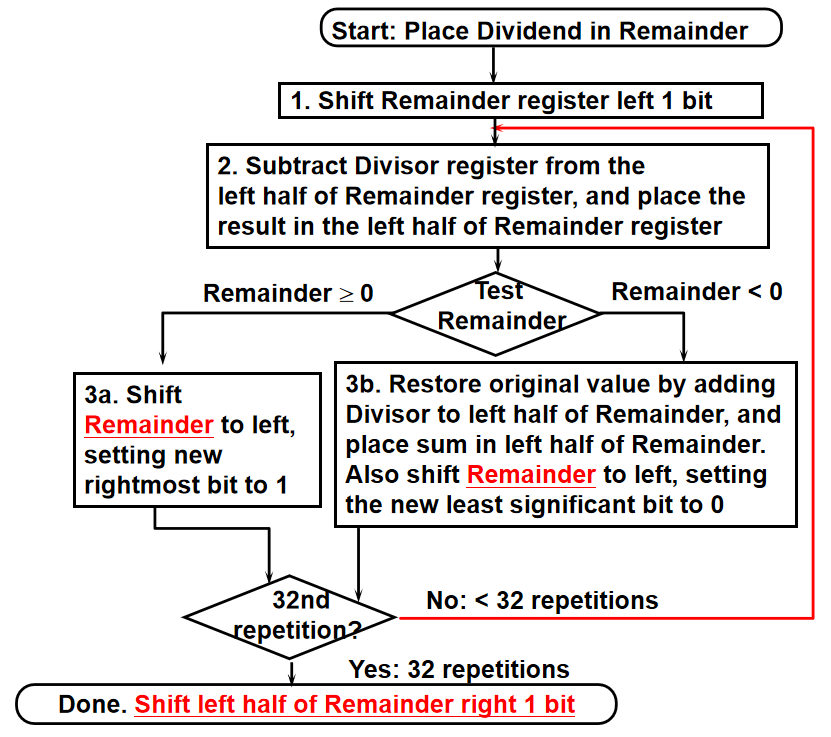

除法的算法流程如下:

除法的第一步是被除数高位减除数,但是这种除法器架构的特点在于计算机是不知道计算部分被除数是否比除数大的。因此第一个分支体现了计算过程,如果余数大于等于0,则被除数是大于等于除数的,因此商左移一位并且LSB置1;若余数是小于0的,则被除数小于除数,下一步操作是恢复原值,即将除数和余数相加并将和放回余数,商寄存器左移一位且LSB置0。这里判断余数是否大于0只需要判断余数的MSB是0还是1即可。

无符号除法器ver.2

因为一些移位占用的资源不会被使用,考虑改进上述结构以加速和节约资源,改进后的结构如下:

改进后被除数和ALU寄存器都是32位,减少了一半空间。余数寄存器和商整合为一体,计算过程共同左移。

这种结构除法器的计算流程如图,可以看出与版本一的差别。优化版本的除法器第一步先进行余数寄存器的左移,再将余数寄存器左半边减去除数进行判断。这样只需判断32次,进行32次循环计算。

但是计算初始余数寄存器进行了一次左移操作,因此计算结束时余数寄存器的左半边也就是余数部分需要右移一位。

有符号除法器

在有符号数计算中,关键在于满足除法运算中的关键表达式:被除数 = 除数 × 商 + 余数

因此四种情况可以分别列出,正 ÷ 正,正 ÷ 负,负 ÷ 正,负 ÷ 负。

只要被除数与除数符号不一致,则商为负号。反之若两操作数符号一致,则商为正号。余数保持与被除数的符号一致。

总结

由乘法器和除法器的学习可以看出,两种设计都需要ALU和一些移位寄存器,而MIPS型CPU中的Hi和Lo寄存器组合起来,在乘法运算和除法运算中作为64位移位寄存器。

32位的乘法/除法硬件如下所示:可以看出关键在于控制逻辑来决定移位寄存器的左移或右移来进行除法或乘法操作。