异步复位问题中关键的异步复位,同步释放

引言

在电路设计中使用异步复位具有一些独到的优势(相较于同步复位),比如说:

- 大多数vendor library中的触发器是内置有异步复位输入的,因此省去了同步复位触发器设计中的组合逻辑电路,节省了大量逻辑资源,使得data path更为简洁。

- 可以在没有时钟的情况下进行复位

但是考虑到异步复位不仅仅复位是异步的,其复位信号撤去也是异步进行的。因此若在触发器的有效时钟沿附近撤去,就可能造成触发器输出亚稳态,从而导致ASIC不能回到初始确定状态。另一个问题就是若输入源存在毛刺,那么噪声或者毛刺就会造成“虚假”的复位信号,影响到整个系统。

考虑到上述缺陷,在每个异步复位设计中都应该包含一个同步复位电路!

异步复位,同步释放原理

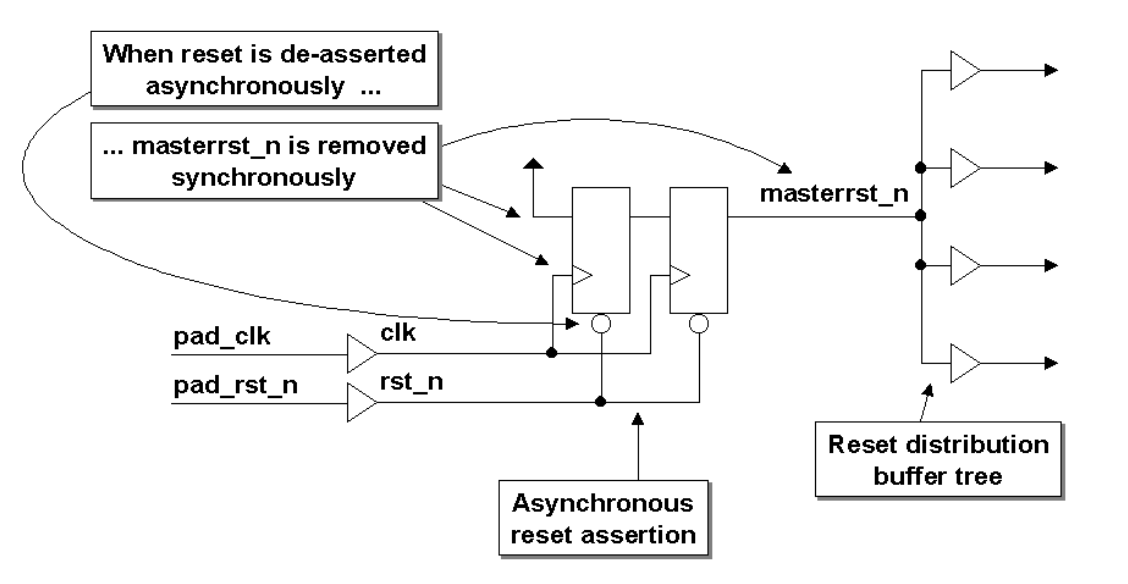

该电路构造如下:

该电路的异步复位是即时输出的,而复位释放需要2个上升沿后输出到reset buffer tree中。第二个触发器消去了异步复位或者太过于靠近时钟边沿造成的亚稳态问题。

设计代码

参考文献

Cummings C E , Mills D . Synchronous Resets? Asynchronous Resets? I am so confused! How will I ever know which to use?[J]. Snug San Jose User Papers, 2002.