verilog中initial块里的阻塞与非阻塞赋值问题

问题描述:

单bit信号跨时钟域,使用握手通信法进行同步处理,在仿真时出现的问题。

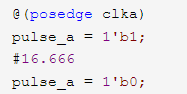

构建testbench时,使用了非阻塞赋值。

`timescale 1ns/1ps module tb_cdc_1bit_f2s_reqack(); reg clka; reg src_rst_n; reg pulse_a; reg clkb; reg dst_rst_n; wire pulse_b; initial begin clka = 1'b1; src_rst_n = 1'b0; pulse_a = 1'b0; clkb = 1'b1; dst_rst_n = 1'b0; #20 src_rst_n = 1'b1; dst_rst_n = 1'b1; #20 @(posedge clka) pulse_a = 1'b1; #16.666 pulse_a = 1'b0; end always #8.333 clka = ~clka; always #25 clkb = ~clkb; cdc_1bit_f2s_reqack inst_cdc_1bit_f2s_reqack ( .clka (clka), .src_rst_n (src_rst_n), .pulse_a (pulse_a), .pulse_b (pulse_b), .clkb (clkb), .dst_rst_n (dst_rst_n) ); endmodule

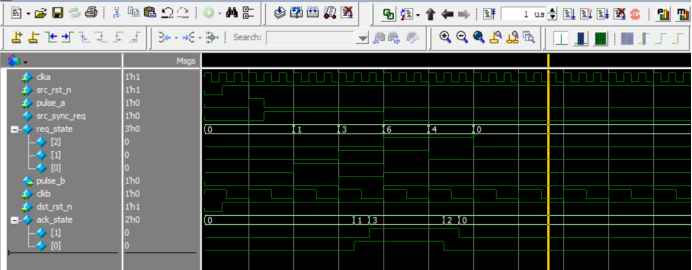

modelsim波形图如下所示,src_sync_req是在clka时钟域对pulse_a的展宽,作为请求信号传送到时钟域clkb,可以看到无法采样到pulse_a。

解决方案:

这篇博文清晰得讲解了阻塞与非阻塞的使用情况:https://www.cnblogs.com/lyc-seu/p/12562107.html

因而可以看出,initial块中的

用法不正确,在这里应该采用阻塞赋值,等待时钟上升沿来后再进行赋值即可。

修改后的仿真波形即可正确地描绘单bit跨时钟域的处理情况。