基于ISE的不同复位方式触发器电路

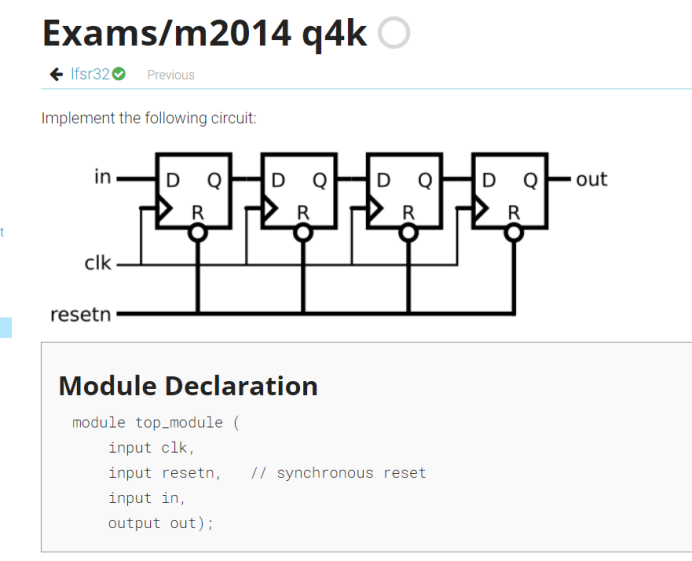

今天在做HDLbits时这道题引起了注意:

设计要求使用同步复位来实现。但是实际上真正使用同步复位的移位寄存器是这样的电路结构吗?

于是在ISE中进行综合检验:

本题的RTL代码如下:

1 module top_module (

2 input clk,

3 input resetn, // synchronous reset

4 input in,

5 output out);

6

7 reg shift_reg01,shift_reg02,shift_reg03,shift_reg04;

8 always@(posedge clk)begin

9 if(!resetn)begin

10 shift_reg01<=0;

11 shift_reg02<=0;

12 shift_reg03<=0;

13 shift_reg04<=0;

14 end

15 else begin

16 {shift_reg04,shift_reg03,shift_reg02,shift_reg01}<={shift_reg03,shift_reg02,shift_reg01,in};

17 end

18 end

19 assign out = shift_reg04;

20 Endmodule

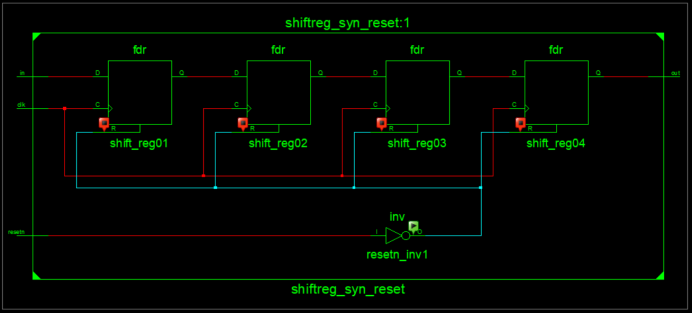

综合后的电路图如下所示:

可以看到综合生成的触发器自身复位是高有效,输入为低的resetn经过经反相器后变为高输入到触发器中实现复位。

后续对不同复位方式的单个触发器进行综合查看其RTL视图

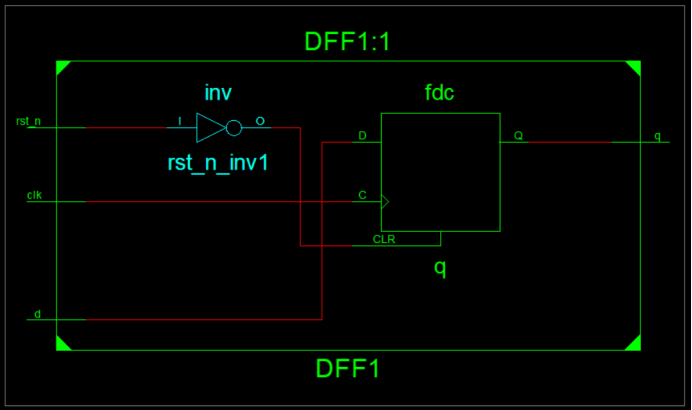

1.异步复位的DFF

RTL代码如下:

1 module DFF1( 2 input clk, 3 input rst_n, 4 input d, 5 output reg q 6 ); 7 8 always@(posedge clk or negedge rst_n) 9 if(!rst_n) 10 q <= 0; 11 else 12 q <= d; 13 14 endmodule

综合后的电路如下所示:

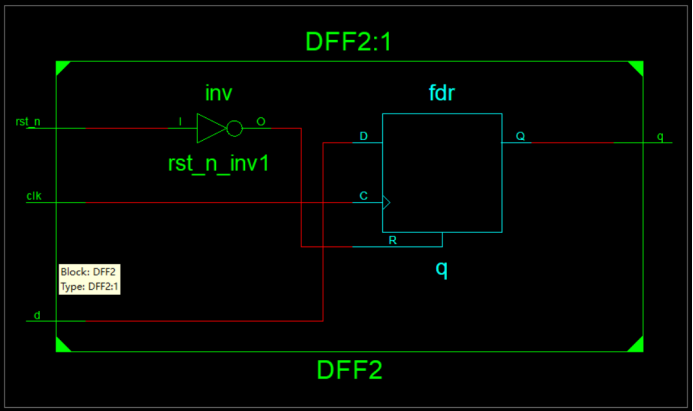

2.同步复位的DFF

RTL代码如下:

1 module DFF2( 2 input clk, 3 input rst_n, 4 input d, 5 output reg q 6 ); 7 8 always@(posedge clk ) 9 if(!rst_n) 10 q <= 0; 11 else 12 q <= d; 13 14 endmodule

综合后的电路如下所示:

SUM:

同步复位触发器与异步复位触发器的区别在于触发器的复位管脚名称不同,同步复位是R,而异步复位是CLR。然而ISE对于综合出的触发器都是高电平复位,这里我的想法因为是Xilinx建议的复位方式是高电平复位,与ASIC设计中建议的低电平复位不同,因此软件的综合效果都是按高电平复位来进行生成触发器。