什么是DPT中的Odd Cycle问题?它会有什么问题?该如何解决?

什么是DPT中的Odd Cycle问题?它会有什么问题?该如何解决?

本文选自知识星球中的ICC2教程,更多IC干货见星球,

同时星球QQ群还有分享高达40多万字的个人数字后端设计笔记,欢迎加入,星球二维码见文末。

星球在2022年,不考虑更新的长文的话就更新了48万字,

更新的主题数大概是8篇/天,考虑长文的话会更多。

问题:什么是DPT中的Odd Cycle问题?它会有什么问题?该如何解决?

参考答案:

前面解释了什么是DPT技术:

星球链接:https://t.zsxq.com/04RRVnu3j

一层Metal由两层Mask来成型,每一层Mask上相邻Shape的最小间距即为DPT Spacing。

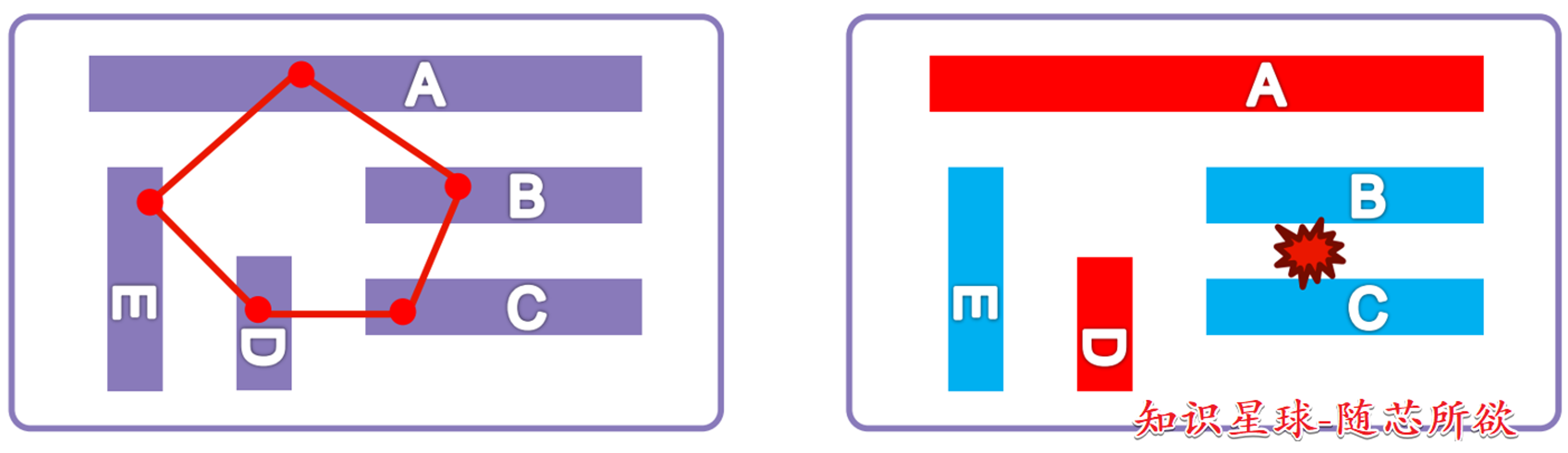

如果在一个版图上存在着奇数个Shape围成的圈,且相邻的Shape之间的距离小于DPT Spacing(这就意味着它们需要涂上不同的Color),那么就会形成DPT Odd Cycle问题。

这种问题会造成它们无法被合理涂上两种颜色,也就是没办法分到两个Mask上而不引起DRC。右下角是一种涂色方案,可以看到,Shape B和C的颜色相同,但是它们的距离小于DPT Spacing的要求,因此不能被分配到相同的Mask上。由于存在奇数个Shape,因此无论怎么去涂色,在不改变Layout的情况下,总会存在冲突的地方。

解决方案:

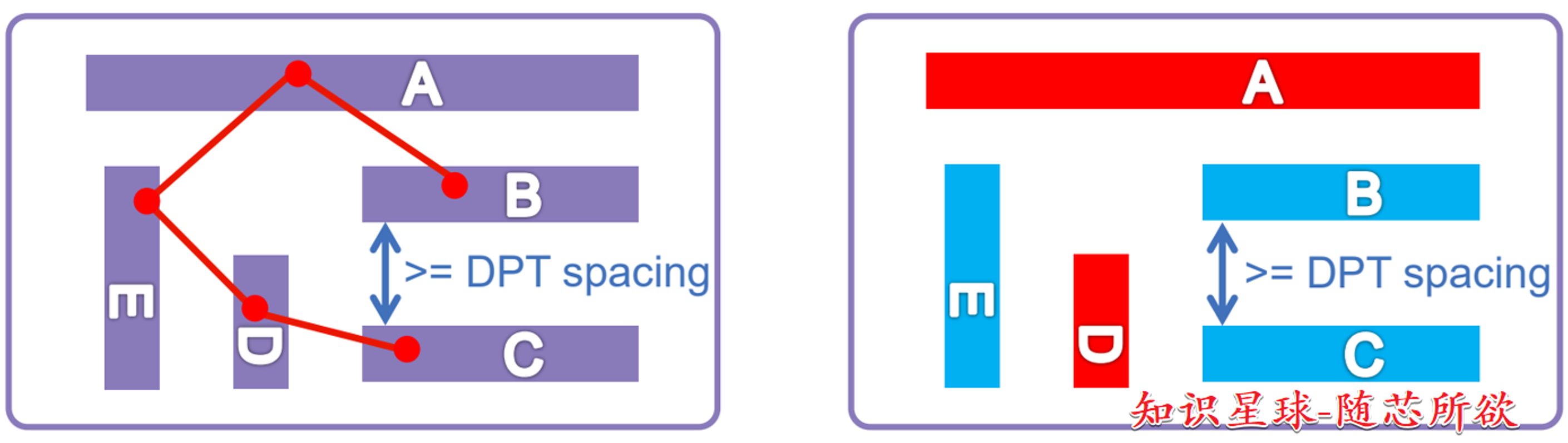

在任何一个地方,将两个相邻的Shape距离增大到DPT Spacing(或者更大)就可以修复这种问题,因为这样原来没办法分到两个Mask上的Shape(比如上图中的B和C)就可以被分到两个Mask上了。如下图所示:

对于DPT工艺的绕线,允许多个Shape彼此之间的距离小于DPT Spacing的要求,只要它们没有产生Odd Cycle问题就可以了,这个是与普通工艺的绕线的一个很大的不同之处。

Poly Space Effect (PSE)效应 应变硅工艺 eSiGe CESL LOD OSE EndCap相关

长文--IC后端物理效应--LOD Effect(扩散区长度效应) LOD与OSE的关系

MOS管的米勒效应-讲的很详细

min vt width/spacing/area - 多阈值库在布局时如何满足它们的要求

DPT/double pattern什么意思,先进工艺下为什么引入double pattern?

什么是DPT中的Odd Cycle问题?它会有什么问题?该如何解决?

FinFET结构、优缺点以及相应的原因

MOS结构的演变,GAA以及MBCFET的结构与特点

~~ 知识星球 ~~

知识星球创建了一个专属QQ交流群,上传了积累多年(应该有8年了)的IC后端笔记(都是一个字一个字打的),同时也会不定时发一些红包(2022年已经累计发放2210元红包),感兴趣的可以加入。目前已上传的笔记有:

- 低功耗设计技术总结-3万字,129页

- IR drop的分析与修复总结-4.3千字,20页

- 数字后端理论及实践-ICC干货笔记-11万字,423页

- 数字后端理论及实践-Innouvs教程(第4版)-5.7万字,316页

- ICC2教程-星球精编版-2万字,125页最新上线:

- 数字后端理论及实践-Innouvs教程(第5版)-11.8万字,635页

- 面试笔试题整理 面试笔试经验分享(第1版)-1.6万字,48页

- 面试笔试题整理 面试笔试经验分享(第2版)-2.3万字,87页

- ICC2 ICC与Innovus的命令对照(第1版)

- Tcl与DesignCompiler教程(第1版)-6.1万字,183页

- DRC规则讲解、DRC的检查与修复(第1版)- 7.3千字,26页

- 更多教程、笔记持续更新中。

浙公网安备 33010602011771号

浙公网安备 33010602011771号