IR-drop问题的分析与修复(三):add checkerboard placement blockage in narrow channel

本文转自:自己的微信公众号《集成电路设计及EDA教程》

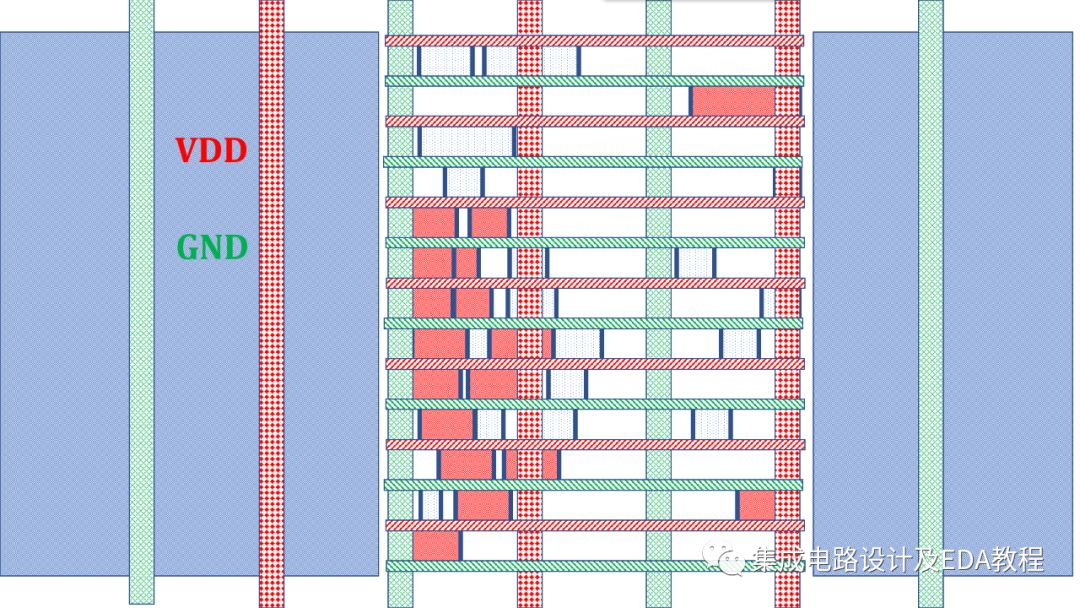

前面讲解了调整Floorplan使得Narrow Channel里面形成偶数个PG来修复IR-drop的方法。可是我们可能还会看到下面的情形:Narrow Channel里面已经是Even PG了,但是还是有一些标准单元有IR-drop(已经用红色标出):

注:图中Narrow Channel里面的Endcap、Decap和Filler为了简化起见都没有画出来。

基本上它们都有这样的特点:

· 有IR-drop的那些Cell基本都靠近Macro的Boundary;

· IR-drop比较严重的是那些Cell都是聚集在一起的,局部的Density比较严重的区域。

上篇推文我们讲了Narrow Channel出现IR-drop的几种解决方法:

1、调整Floorplan让Channel形成偶数个PG(Even PG);

2、在Narrow Channel区域加Checkerboard的Placement Blockage;

3、给Narrow Channel里面的标准单元加Cell padding(keepout margin);

4、在Narrow Channel区域加Extra pg;

5、给Macro(本图中是RAM)加keepout margin。

这里讲其中的第二种:加Checkerboard的Placement Blockage。

分析:首先看些这些Cell的类型,一般我们不希望在Narrow Channel里面有Function的Cell,只希望是一些简单的Buffer。如果是比较宽的Channel,那倒是可以放Function Cell的,不过我们也要保证它们的密度不能太高,否则也会导致IR-drop,限制密度的方法是打Partial Blockage。

因此对于Narrow Channel,我们一般设置成Buffer only的Blockage,如果里面出现了上面所示的IR-drop问题,这些Cell根据连接关系可能有几种:

一种可能是下面的情况,Macro的Pin朝向这里,要从这里出Pin,在Macro比较长的情况下,为了满足Setup和Transition的要求,需要就近放一些Buffer:

这种情况我们可以看下这个Macro的Connection关系,如果是连到左边的Logic,那么我们可以将它左右Flip一下,这样右边Channel里面的Cell就会少了。

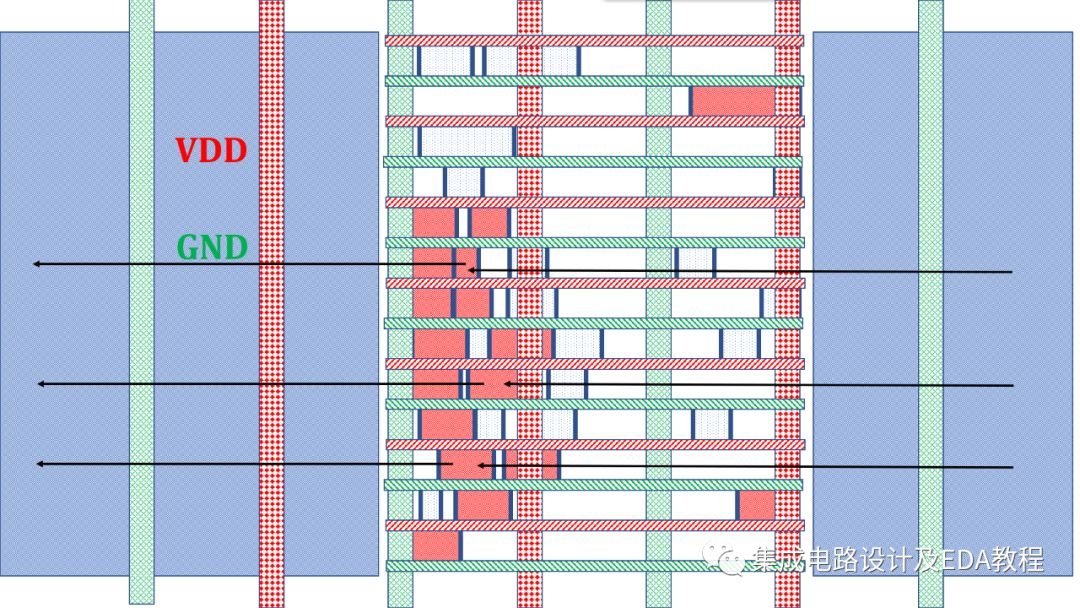

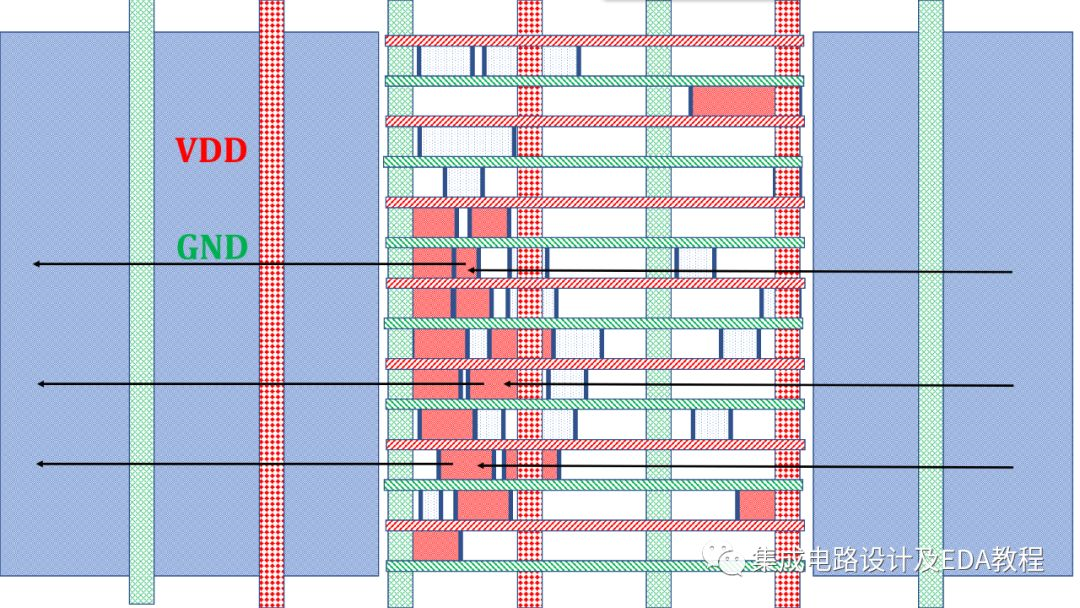

还有可能是一些信号从上往下/从下往上传,或者从左往右/从右往左传,由于Macro尺寸比较大,为了满足Transition的要求,要在这个Channel里面插入一些Buffer:

其实可以观察,这个Channel里面的Cell数目不是很多,如果将所有的Cell分散开也是放得下的,可是Cell却堆在了一起,且堆在了离RAM比较近的地方。同样,我们多半也会在RAM四周看到这种很多Cell贴者RAM摆放的情况,如下图所示:

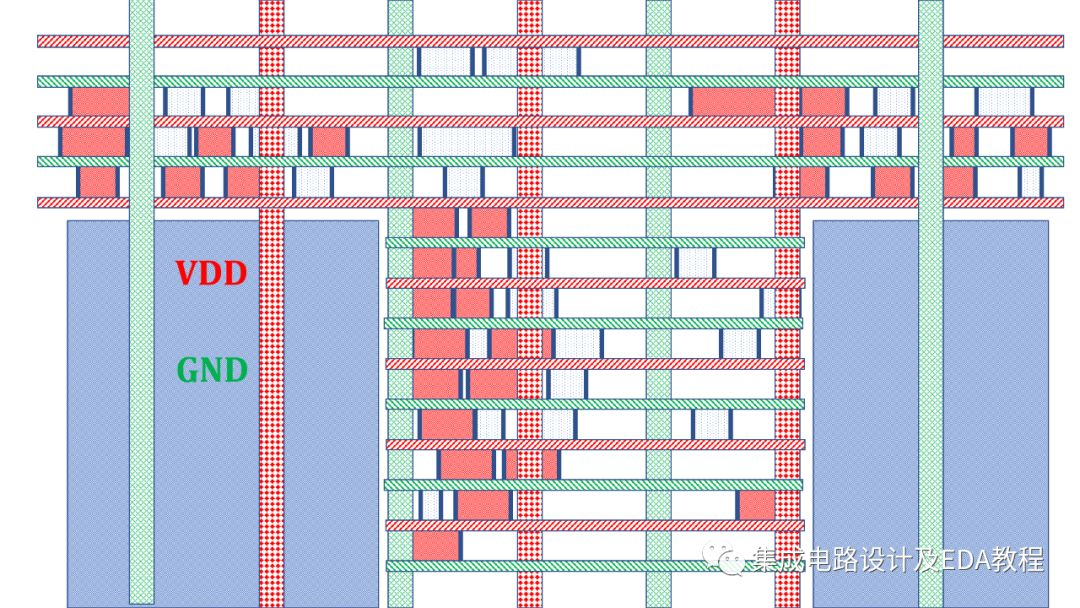

对于这些情形,我们可以通过在Narrow Channel里面以及Macro周围打一些分散的成棋盘(Checkerboard)分布的Hard Placement Blockage。一方面可以防止太多的Cell被摆到这个Channel里面,来限制Cell的Density,另一方面也可以强制Channel里面的Cell分散摆放。加入Checkerboard的Hard Placement Blockage效果如下图所示:

友情提示:在每个阶段的优化期间(Place、CTS、Route)可能工具都会加入一些优化的Cell,为了防止这些区域又加一堆的Cell,我们可以保持这些Blockage,直到最后加Filler之前将它们Remove掉。

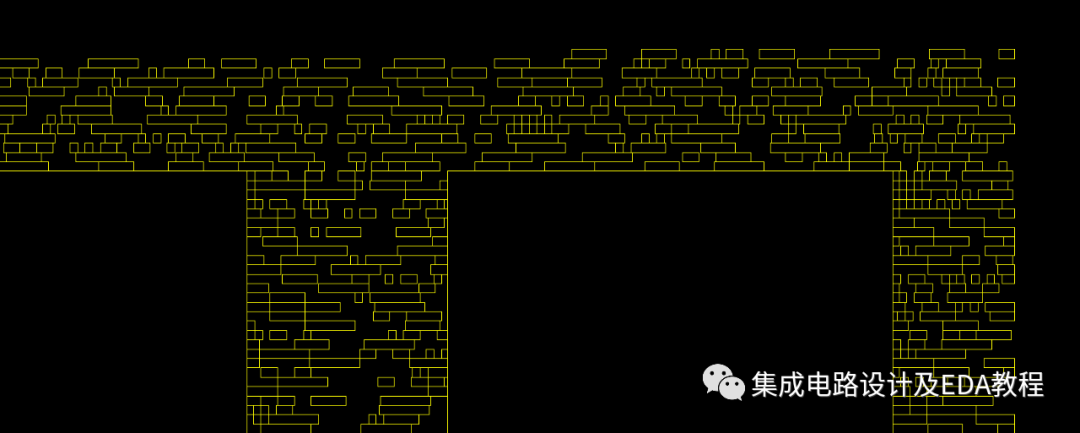

下面是加了Checkerboard之后Cell的摆放效果,可以看到Cell的密度大大降低了,且分布相对较为分散:

用这种方式可以降低Narrow Channel及Macro周围发生IR-drop的几率。

本推文就讲到这里,以后的推文陆续讲解其他的解决方案。

相关推文

IR-drop问题的分析与修复(含脚本分享)(一):Partition boundary cells clustering

IR-drop问题的分析与修复(二):odd pg in Narrow Channel

浙公网安备 33010602011771号

浙公网安备 33010602011771号