数字后端低功耗 - 多种低功耗技术及其在IC后端布局中的应用

本文转自:自己的微信公众号《集成电路设计及EDA教程》

推文主要内容:

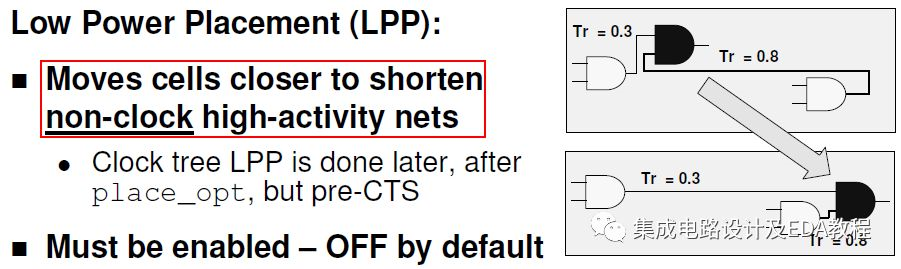

- LPP: Low Power Placement

- GLPO: Gate-level power opt

低功耗技术:

- Buffer Insertion

- Cell Sizing

- Pin Swapping

- Phase Assignment

- Technology Mapping

- Factoring

有哪些低功耗策略可以应用到芯片物理布局阶段从而降低芯片的功耗呢?

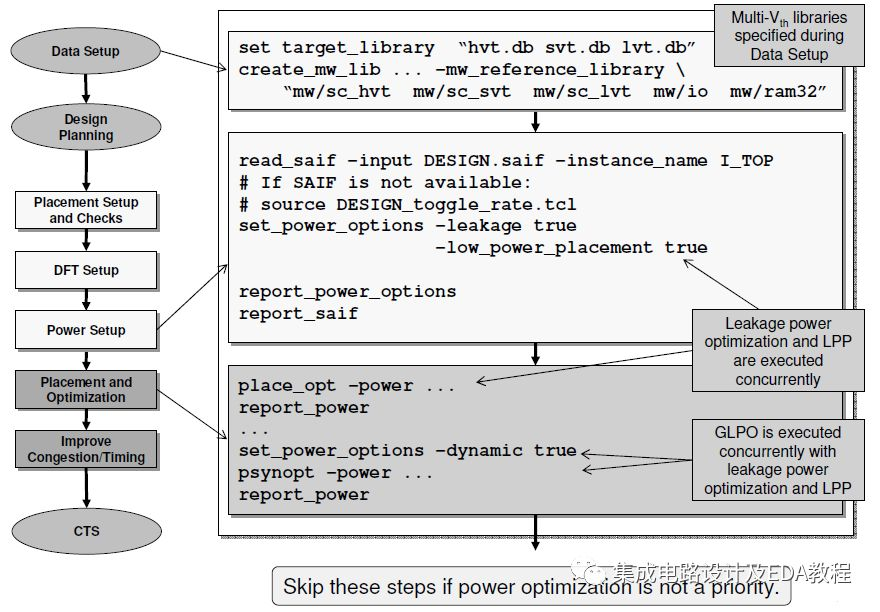

执行静态功耗优化的一些设置:

1. 对于MCMM的设计而言,我们也需要在创建scenario的时候指定哪些scenario可以被用来进行静态功耗的优化,一般选择那些静态功耗非常大的scenario,所用命令为:set_scenario_options -leakage_power true

2. 指定多阈值电压约束,命令为:set_multi_vth_constraint

执行动态功耗优化的流程:执行LPP降低动态功耗的流程如下:

1. 对于MCMM的设计而言,我们首先需要在创建scenario的时候指定哪些scenario可以被用来进行动态功耗的优化,所用命令为:set_scenario_options -dynamic_power true

2. 在布局之前,读入网表动态仿真得到的saif文件,它记录了Cell和Net的Swithing Activity。所用命令为:read_saif。之后使能ICC中的LPP功能,这样ICC在布局阶段会自动挪动一些Cell,缩短高翻转的Net长度,降低这些Net上的电容,从而降低与之相连的Cell的动态功耗。如果没有saif文件的话,需要在布局之前在设计的输入端口设置Toggle Rate并让其往后传递,如果知道某些中间节点的Toggle Rate也可以设置,这样功耗分析会更加精确。

该选项默认是关闭的,需要在布局之前开启。

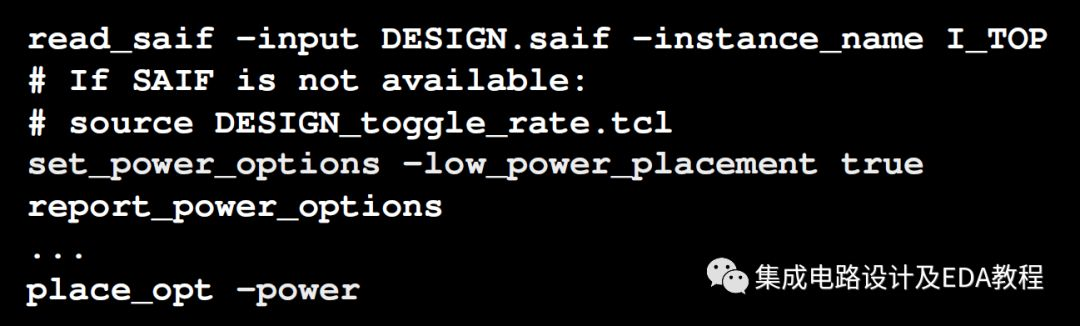

旧版的ICC中是通过下面的方式开启的:set_power_options -low_power_placement true

Flow如下:

注意:在新版的ICC中,set_power_options命令已经被废除;如果是新版的软件可以用下面的命令:set_optimize_pre_cts_power_options -low_power_placement true

执行GLPO降低动态功耗的流程如下: 在布局的时候我们也可以通过门级功耗优化(Gate-level power optimization, GLPO)来优化逻辑从而降低功耗。

门级功耗优化的技术:

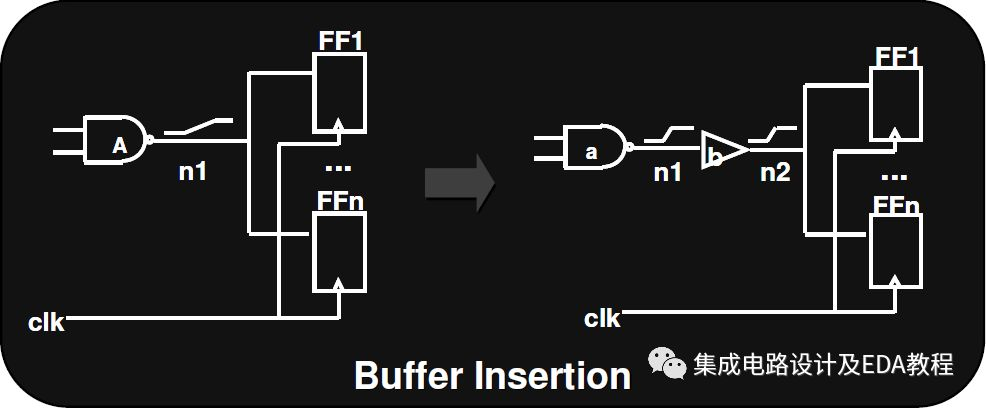

1. Buffer Insertion:插入Buffer以降低负载电容,并缩短输入Transition时间,从而降低动态功耗。

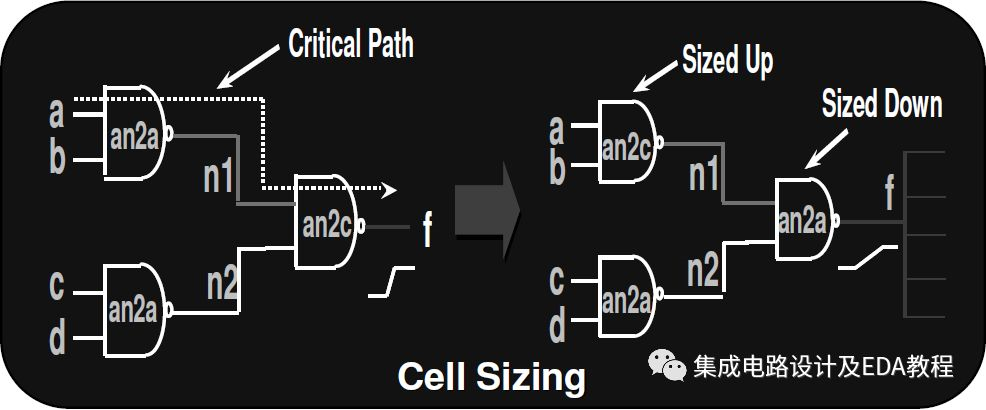

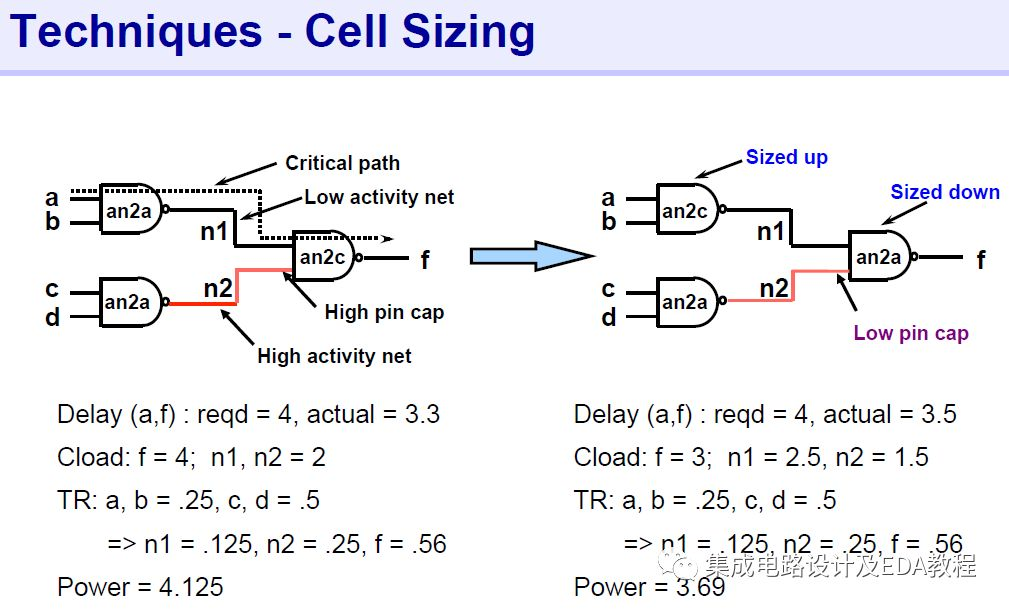

2. Cell Sizing:降低High Switching Activity网络上的电容,缩短Transition时间以降低Inernal Power。

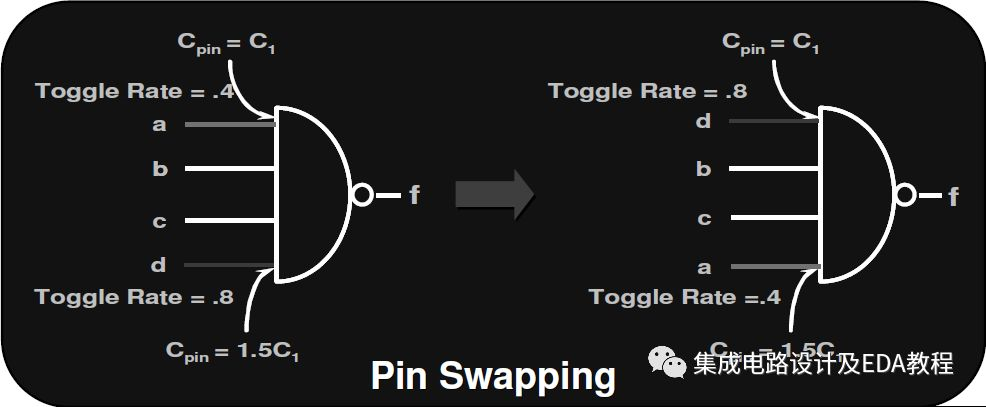

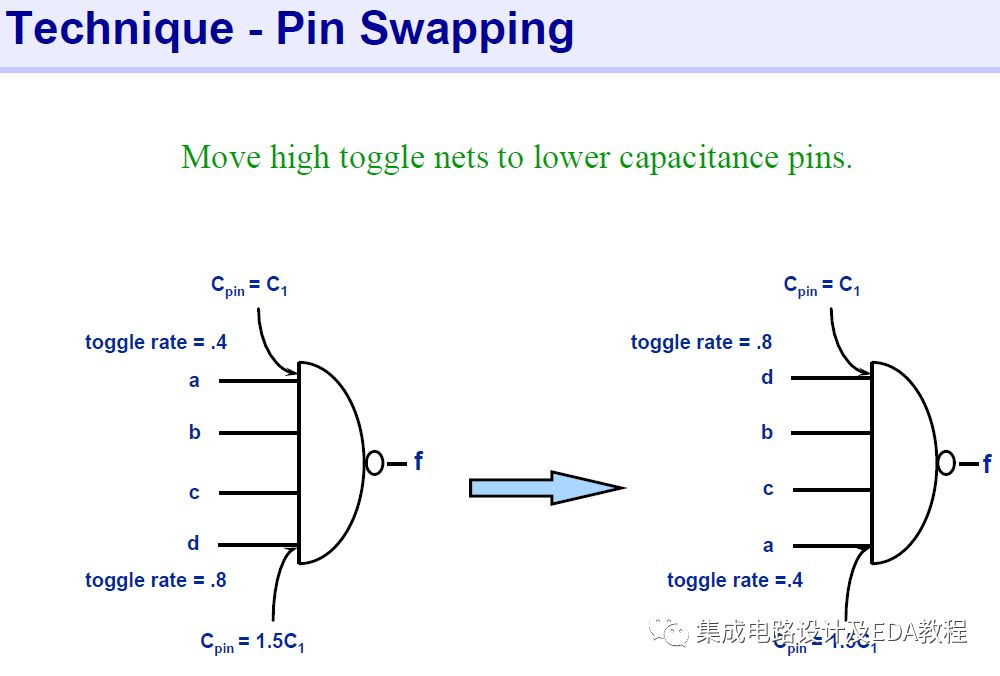

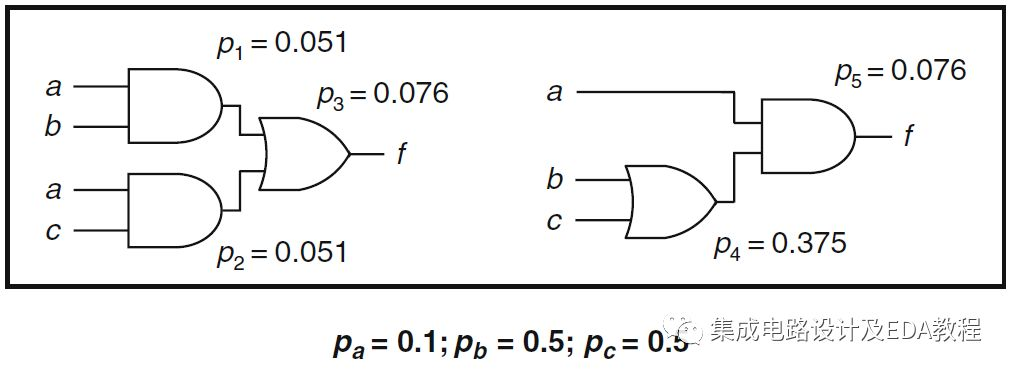

3. 交换引脚(Pin Swapping):将高翻转的Net连接到Cell的低电容引脚上。

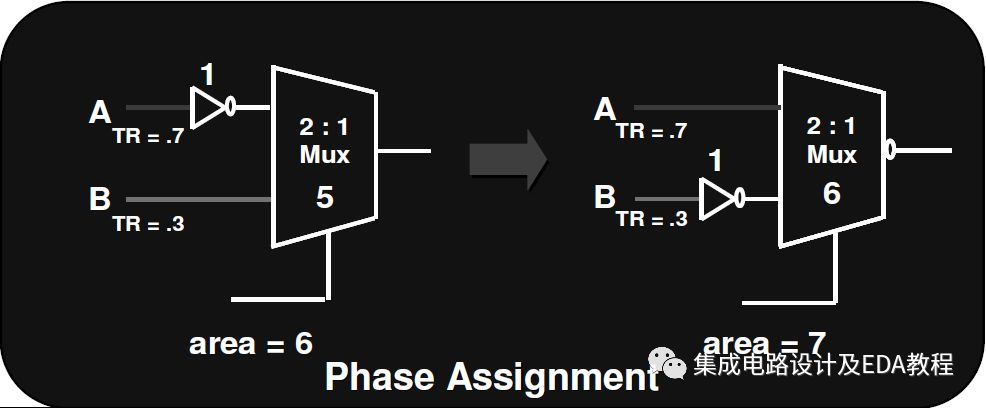

4. 相位分配(Phase Assignment):进行相位翻转来移除高翻转的反相器

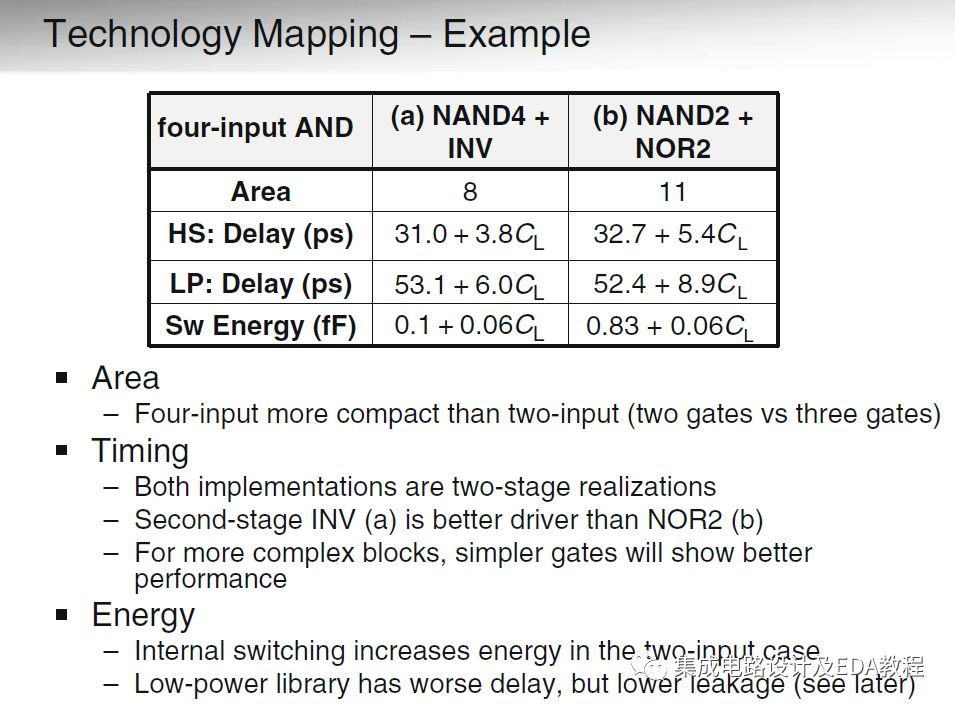

5. 工艺映射(Technology Mapping):隐藏Cell内的高翻转网络比如4输入的AND门,我们可以用AND4+INV的方案实现,也能通过NAND2+NOR2的方案实现,两种方案在Area和Delay、Energy方面的对比如下:

PPA的对比:

面积:方案(a)结构更加紧凑,因此面积更小;

速度:两种方案都是双级结构,方案(a)比(b)速度更快,或者至少一样快;

能量:方案(a)内部高翻转网络被隐藏,因此消耗的能量更少,且效果非常明显。

6. 代数变换分解(Algebraic Transformations Factoring):修改网络结构,降低电容,但可能会增加活动性。

注意:可以在place_opt期间同时执行GLPO,LPP和泄漏功耗优化,也可以在place_opt之后,在psynopt期间单独执行GLPO,可以获得类似的结果,并可能会降低整体运行时间。

旧版ICC整体Flow如下:

在新版ICC里面,set_power_options命令被废除,同样通过set_scenario_options -dynamic_power true选取进行动态功耗优化的scenario,之后用place_opt -power来进行GLPO。

网易云课堂

视频课程

Calibredrv教程-提高流程自动化

浙公网安备 33010602011771号

浙公网安备 33010602011771号