数字IC前后端设计中Setup违反的修复方法

本文转自:自己的微信公众号《集成电路设计及EDA教程》

数字IC设计中Setup的分析与优化贯穿前后端设计中,最好在开始后端设计之前就获得一个没有Setup违反的网表,下面按照从前到后的流程逐一讲解每个阶段如果出现Setup违反该如何解决。下面用到的命令,主要针对的是Synopsys公司的综合工具DC以及布局布线工具ICC。还有需要注意的是,Setup的修复和之后要讲解的Hold的修复有很大的不同,Setup的违反随着布局到布线阶段的推进,它是越来越恶化的,不像Hold,线延迟会有益于Hold的修复的,因此存在少量的违反是没有问题的。因此,在开始下一阶段的Setup修复之前,最好将本阶段的Setup违反都清掉。如果是需要用CCD来修复的Setup违反,那么在CTS之前,这些违反可以不用考虑。 1、逻辑综合阶段就有Setup违反:1.1 在DC中用重定时(Retiming)或者Pipeline修复;例如:

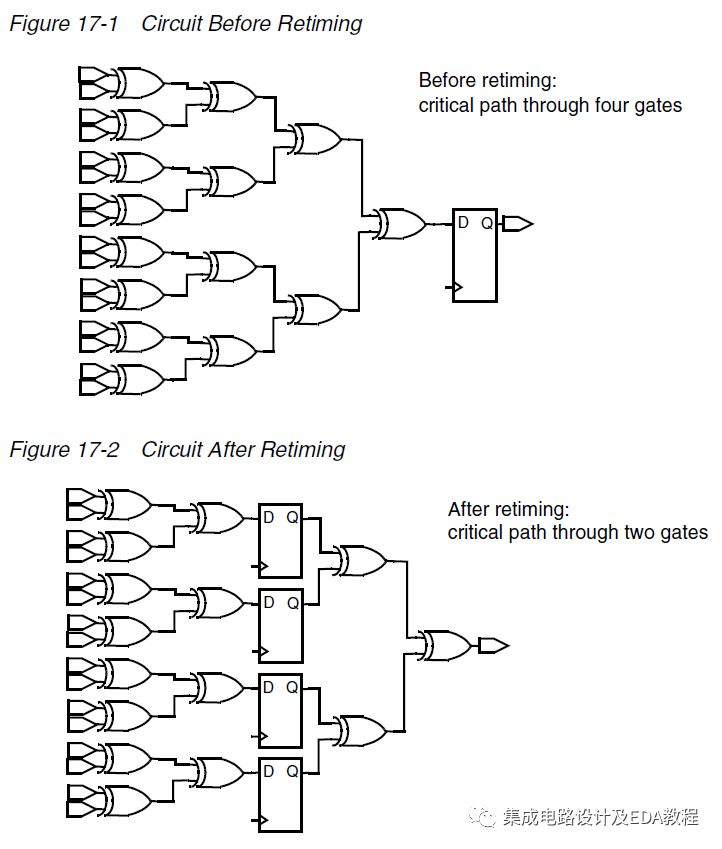

在本例中,在采用寄存器Retiming之前,有四级组合逻辑,并且在关键路径的endpoint处只有一个寄存器。采用Retiming技术后,已被四个寄存器取代的那一个寄存器已经被反向移动了两级组合逻辑,且关键路径现在包含两级/部分。每级/部分的关键路径延迟小于初始单级设计中的关键路径延迟。如在本例中,通过Retiming来减少延迟通常会导致设计中寄存器数量的增加,但通常这种增加很小。

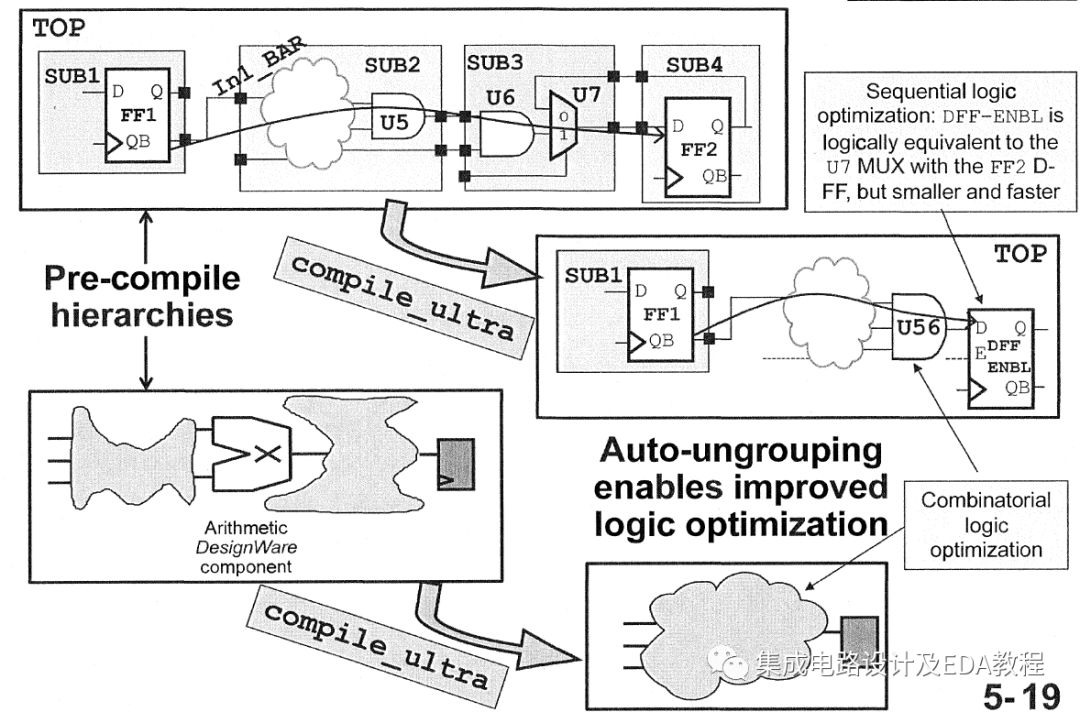

1.2 在DC中通过group ungroup的方法来对critical的模块进行优化;将那些critical的模块group到一起,然后ungroup,让DC对其进行充分的优化,不会因为在不同的group内而优化受到限制。另外,如果License支持的话,可以用Compile_ultra,它会自动做auto-ungrouping的操作,如下图所示:

FF1和FF2之间的好多级组合逻辑经过compile_ultra编译优化之后,可以打破hier的限制,在时序方面可以优化的更好。

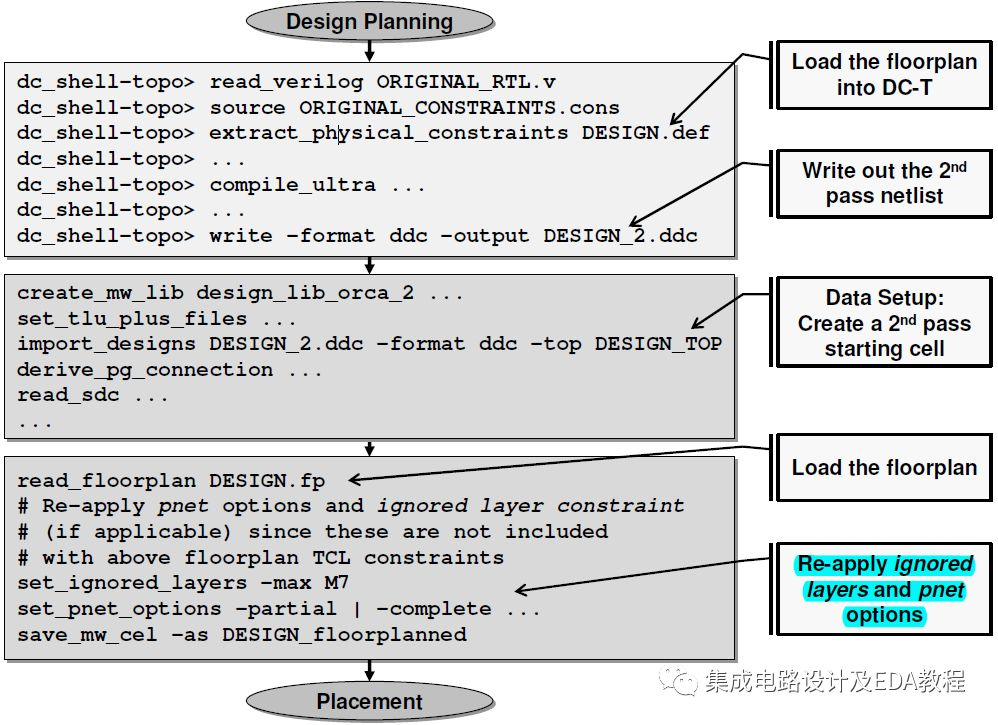

1.3看违反是否很少,并向前向后查看路径的时序,判断在后端中用CCD是否有可能修复;如果该路径的前后时序非常宽裕,那么在后端中用CCD来修复也是可以的。 1.4 用DCT进行增量编译由于DC进行综合时一般用Wire Load Model分析时序,所以不是很准确,并且分析时也没有标准单元或者Macro的具体物理位置,所以分析优化过程不是很贴近物理实际。为了解决这个问题,可以用DCT来解决(结合MCMM)。具体步骤为:ICC导出Floorplan的DEF给DCT,然后用Compile_ultra进行再次综合。详细流程如下:

1.5 修改电路结构/算法

如果上述方法都不行,那么需要查找设计中的Setup违反是什么样的情况,是很多路径都有一些小的违反还是说这些违反都集中在一个模块上,且违反很大。如果是前者则可以通过DCT再次编译来解决,如果是后者,需要分析在后端中用CCD是否有可能解决,如果不行的话,便只能通过修改电路结构或者更改电路的算法来进行修复了,在系统级或者算法级来解决这种问题也是最有效、程度最好的方法了,不过可能会比较耗时。我曾遇到过这种情况,某个DSP模块的时序非常差,基本上通过软件修复是不可能的,后来换了种算法,在精度、面积、时序上都有了很大的提升,设计的Setup违反也不存在了。 2、布局之后CTS之前有Setup违反:2.1 用DCT进行增量编译首先用零互连延迟模式报告一下,看设计中是否有setup的违反,如果没有的话,那么应该是线延迟太大使得严重偏离了之前的理想情况,这个可以用DCT来进行再次综合。在DCT中将所有的scenario都读入进去,并读入ICC导出的DEF文件,然后进行增量编译;

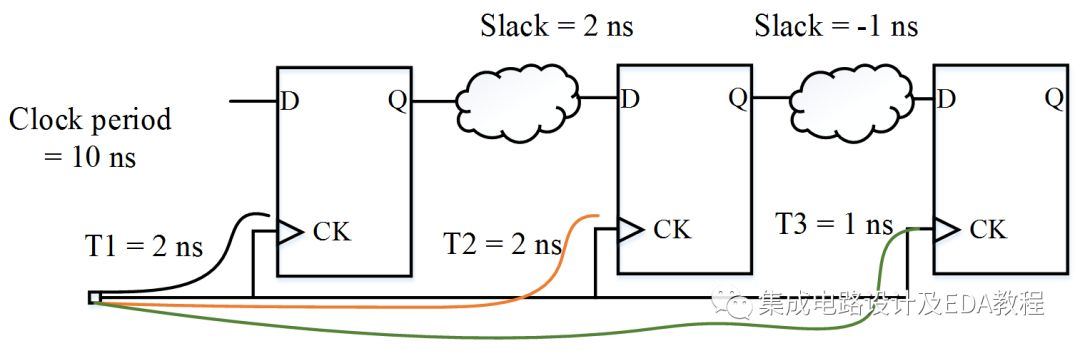

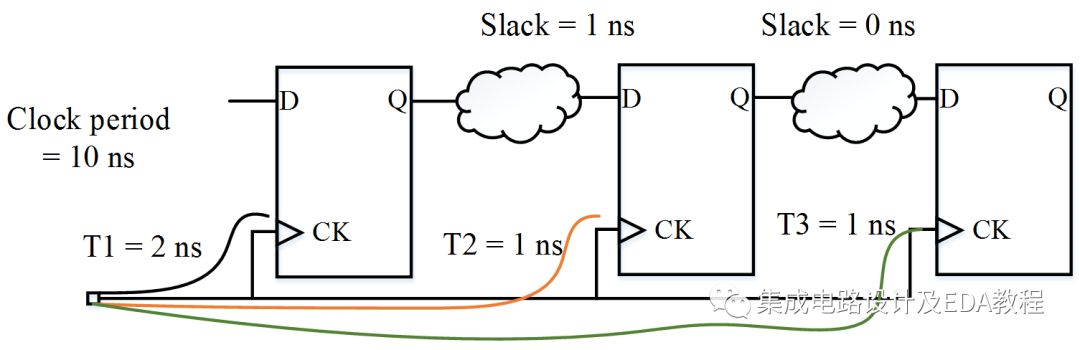

2.2 在ICC中将timing critical的单元靠近放置如果是规模太大使得线延迟太大导致的,在后端设计中也可以将一些critical的单元靠近放置,如果在同一个模块内部,可以创建plan_group;此外还可以对某些具体的net设置netweight来使得这些critical path上的单元靠近放置。 3、CTS之后有违反:看做完CTS之后的Skew+jitter+margin和之前设置的setup uncertainty是否相差较大,如果是这样,说明uncertainty值设置的有问题,无法较贴切的模拟做完CTS之后的时序效果。需要调整之前的setup uncertainty值,然后去看setup是否能够meet。 如果有少量的path由于datapath延迟过长导致setup timing很难meet,可以在CTS过程中采用CCD用useful skew来向前向后借timing,命令为:>clock_opt -concurrent_clock_and_data 当然,也可以有针对性的手动进行操作,在前后级有margin的情况下(大前提),可以对launchpath进行early,或者对capturepath进行late。下面举个例子。 如下图所示,时钟周期为10 ns,图中标明了各时钟路径的延迟。可以看到有一条路径的slack为-1ns,说明这条路径违规。可以看到与这条路径相关的skew是T3 - T2= -1ns。

在用UsefulSkew之前,设计中存在Setup的违反下面我们利用useful skew向前面一个slack比较充裕的路径(slack=2 ns)借点time,来修正现在这条路径,即对T2所在的launch path进行early操作:

在采用Useful Skew之后,设计中不存在Setup的违反

4、布线完成后有少量违反:4.1 可以用ICC中的CCD来修复,>set_concurrent_clock_and_data_strategy>route_opt -concurrent_clock_and_data 4.2 在先进工艺节点下,连线延迟占了很大的比重,这主要是由于net和via上的电阻太大导致的,我们可以控制在route的时候来优化这些高阻抗网络,具体方法:在用route_opt绕线之前,我们可以在set_optimization_strategy命令后边将-high_resistance选项设置为true来启用该功能。当使能高阻抗优化时,时序驱动的布线引擎在插入过孔时会考虑导线电阻,以减小导线电阻,同时保持可布线性。

5、chipfinish阶段有少量违反:可以用ICC中的CCD来修,>focal_opt -concurrent_clock_and_data-setup_endpoints all 6、布局布线中的任何一个阶段其实在ICC中布局布线的任何一个阶段都是可以用PT进行ECO来修复Setup违反。

网易云课堂

课程

《Calibredrv教程-提高流程自动化》

浙公网安备 33010602011771号

浙公网安备 33010602011771号