高速缓冲存储器

cache由SRAM组成,通常直接集成在CPU中,cache可以起到作用是因为程序具有时间局部性和空间局部性

cache工作的基本原理

为便于 Cache 与主存交换信息,Cache和主存都被划分为大小相等的块,Cache块也称Cache行,每块由若干字节组成,块的长度称为块长(也称行长)。因为Cache 的容量远小于主存的容量,所以Cache中的块数要远少于主存中的块数,Cache 中仅保存主存中最活跃的若干块的副本。因此,可按照某种策略预测CPU 在未来一段时间内欲访存的数据,将其装入 Cache。图 3.17 所示为 Cache 的基本结构。

从上面的图片中我们可以看到,cache行和cache块其实并不是完全相同的概念,cache块是一个主存中的数据副本,而cache行除了包含cache块之外,还包括cache标记、有效位等信息。可以类比map中的键和值

某些计算机中也采用同时访问cache和主存的方式,如果cache命中,则终止访存

cache命中率的计算

如果采用先访问cache再访问主存的方式,则\(T_a = Ht_c + (1 - H)(t_c + t_m)\)

cache和主存的映射方式

cache和主存的映射方式有全相联映射、组相联映射和直接映射

| - | 优点 | 缺点 | 组成 |

|---|---|---|---|

| 全相联映射 | 1. cache块冲突的概率低,只要有空闲cache行,就不会发生冲突2. 空间利用率高3.命中率高 | 1. 标记的比较速度比较慢2. 实现的成本比较高,通常需要采用按内容寻址的相联存储器 | 标记-块内地址 |

| 组相联映射 | 结合了全相联映射和直接映射的优点,即组间采用直接映射,而组内采用全相联映射 | 标记-组号-块内地址 | |

| 直接映射 | 实现简单,查找时较快 | 不够灵活,即使cache的其他许多地址空着也不能占用,这使得直接映射的冲突概率最高,空间利用率低 | 标记-行号-块内地址 |

不同映射方式相关标记位及总容量的分析

- 经过计算,主存地址有28位(256MB = 2^{28}B),其中6位为块内地址,3位为行号,剩余19位为标记字段,所以cache的总容量为\(8 \times (1+19+512) = 4256\)位 (有效位 + 标记位 + cache块)

从这里我们可以看出,行号、组号是隐含的,不会真的存储在cache中,所以直接映射占用的额外空间是最小的,组相联映射次之,全相联映射占用的额外空间最大

- 直接相联映射方式中,主存按照块的大小划分,主存地址3200对应的字块号为\(3200 / 64 = 50\),而cache有8行,则\(50 \mod 8 = 2\),因此对应的cache行号为2,若采用组相联映射,组号为\(50 \mod 4 = 2\),对应的cache行号为4或者5

做这道题的时候忘了给内存分块了,直接算\(3200 \mod 8\)导致出错

相联存储器

相联存储器是一种支持通过内容访问的存储器,cache和TLB都是一种相联存储器,cache中的每一个cache行、TLB中的每一条记录,都设置了一个比较器,相联存储器的硬件实现可以抽象为下图

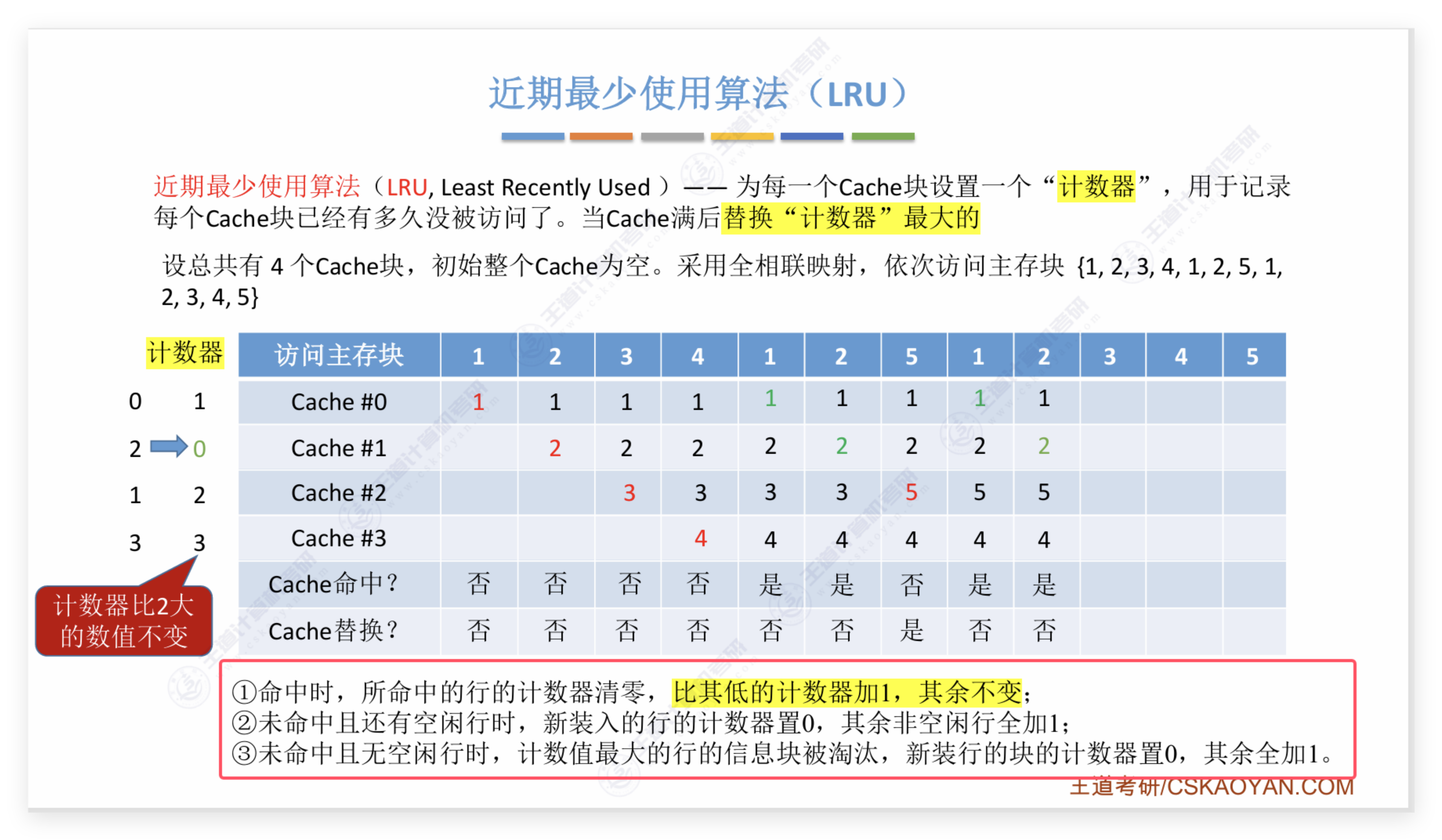

cache替换算法

在最不经常使用算法中,如果两个cache行的标记相同,则按照先进先出淘汰

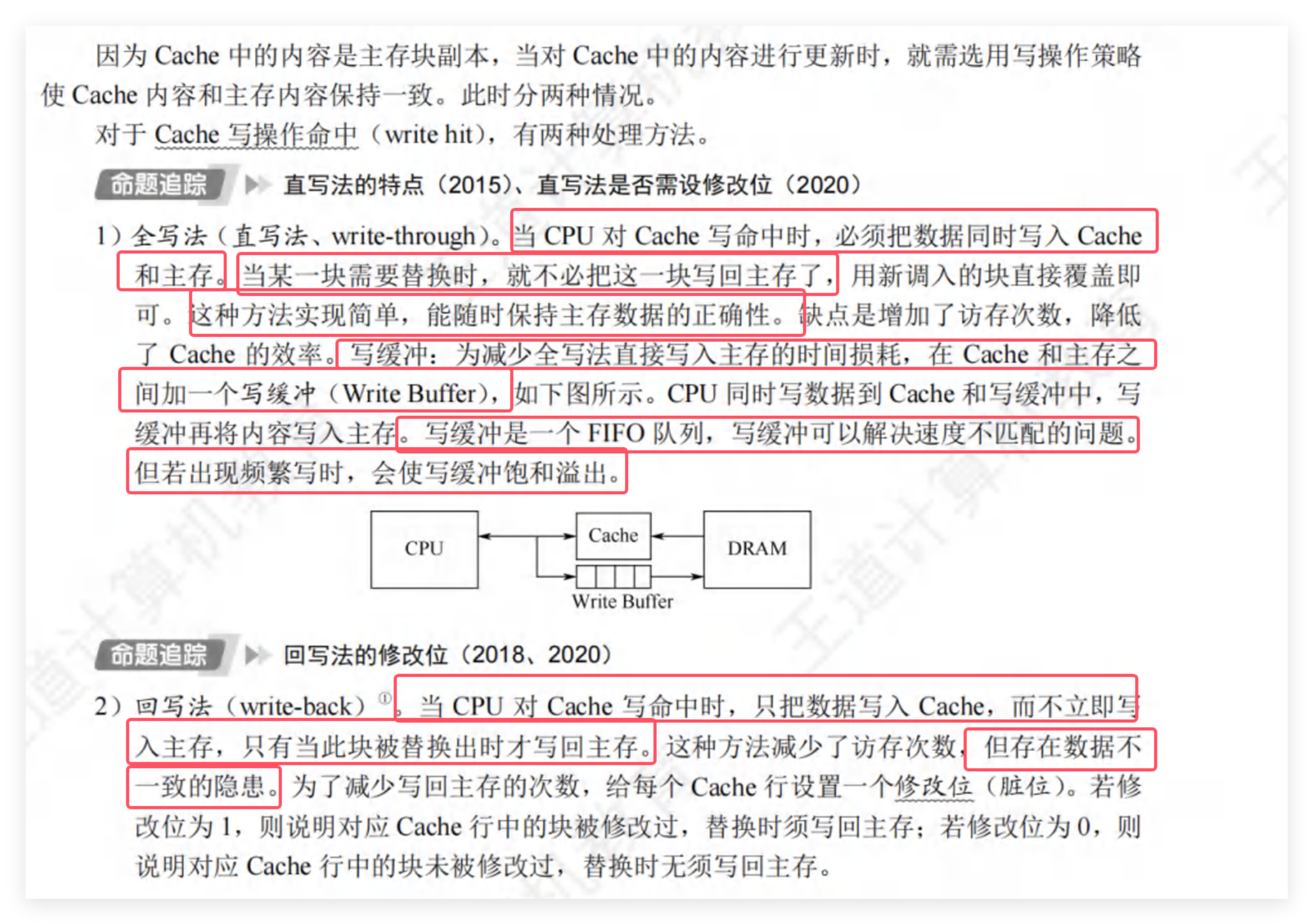

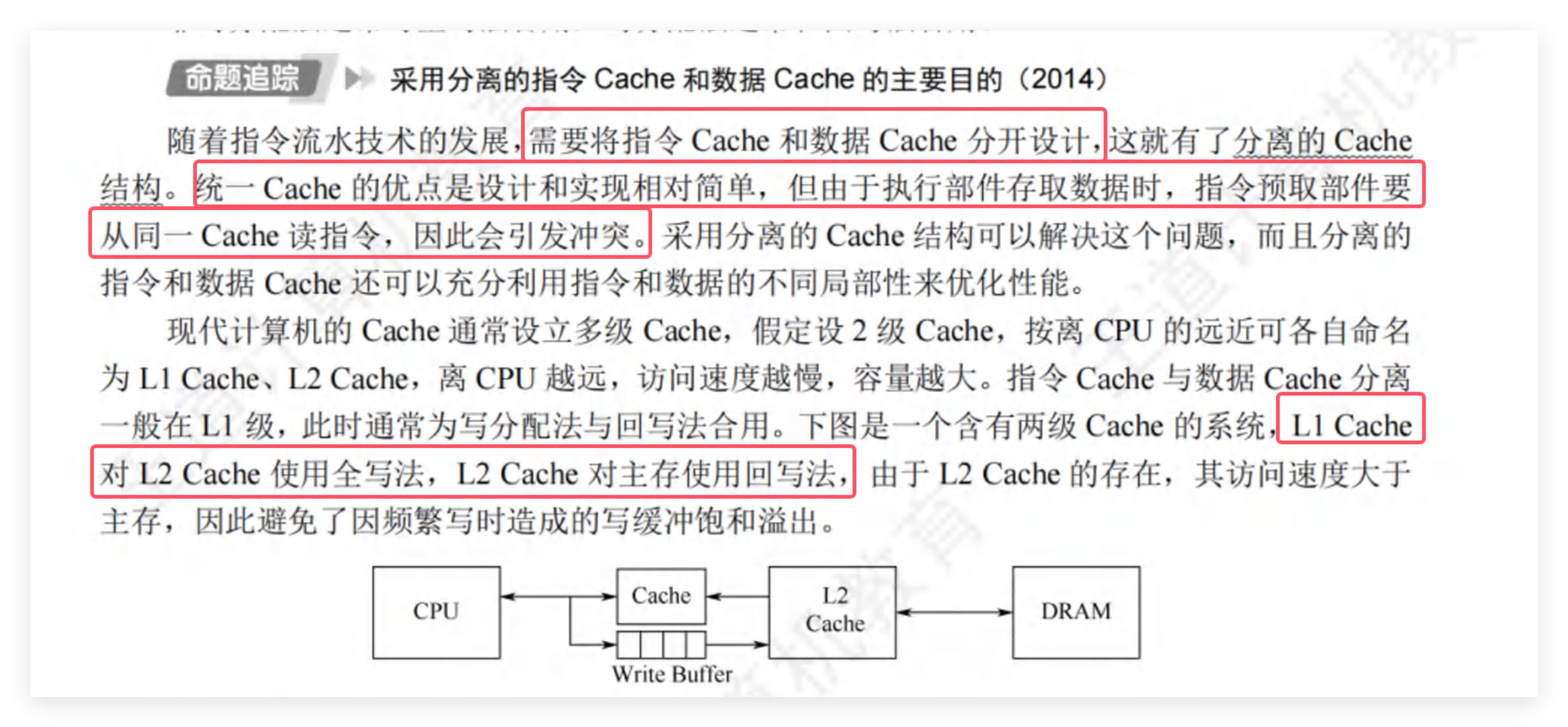

cache一致性问题

为什么回写法存在数据不一致的隐患呢,因为在多处理器的环境中,每个CPU都有自己的cache,如果只修改cache中的数据就有可能造成数据的不一致

浙公网安备 33010602011771号

浙公网安备 33010602011771号