PCB模块化布局系列之时钟电路设计(晶振、晶体)

PCB模块化布局系列之时钟电路设计(晶振、晶体)

一、晶体

在一个电路系统中, 时钟是必不可少的一部分。如人的心脏的作用,如果电路系统的时钟出错了,系统就会发生紊乱,因此在PCB 中设计,一个好的时钟电路是非常必要的。我们常用的时钟电路有:晶体、晶振、分配器。有些IC 用的时钟可能是由主芯片产生的,但追根溯源, 还是由上述三者之一产生的。

1,引脚尽量与芯片距离近,防止受到其他信号干扰。当然也防止它干扰别的线路,因为它是信号源。

2,尽量选择铁壳晶振,其抗干扰能力强些。

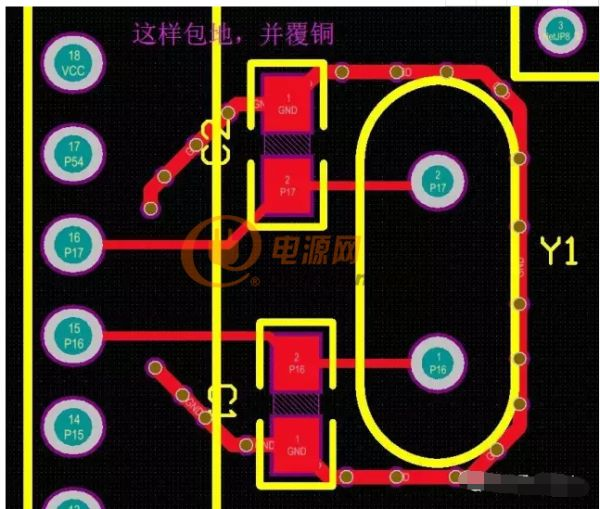

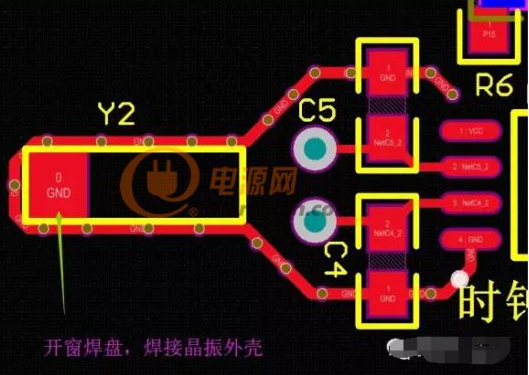

3,晶振下面所有层不能走线,并铺GND铜皮。

4,晶振附近也不要有太近的数字信号线。

5,其负载电容的回流地一定要短。

6,对晶振进行GND包围。部分地方开窗漏GND铜,把晶振外壳焊接到开窗漏GND铜的地方。

7,布局时先经过电容后经过晶振

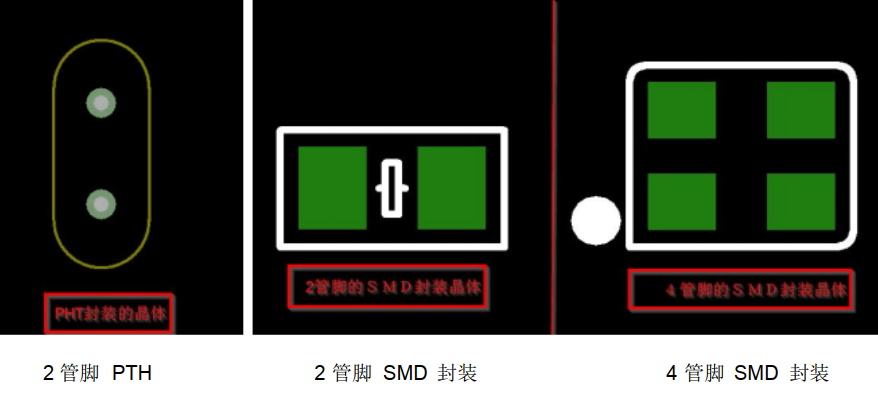

PCB 中常用的晶体封装有: 2 管脚的插件封装,SMD 封装、 4 管脚的 SMD 封装

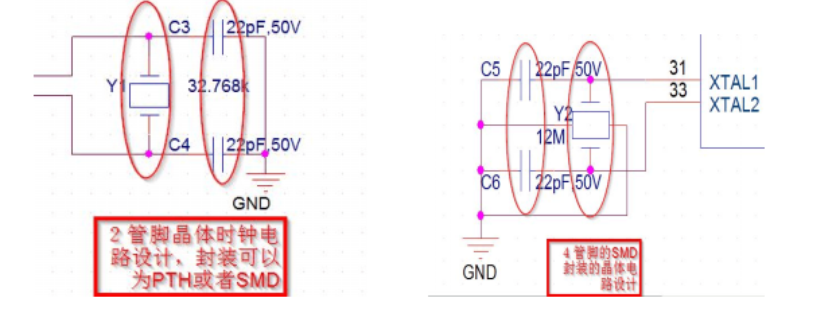

尽管晶体有不同的规格,但它们的基本电路设计是一致的,因此 PCB 的布局、布线规

则也是通用的。基本的电路设计如下图:

从电路原理图中可以看出,电路由晶体 +2 个电容组成,这两个电容分别为增益电容和相位电容。

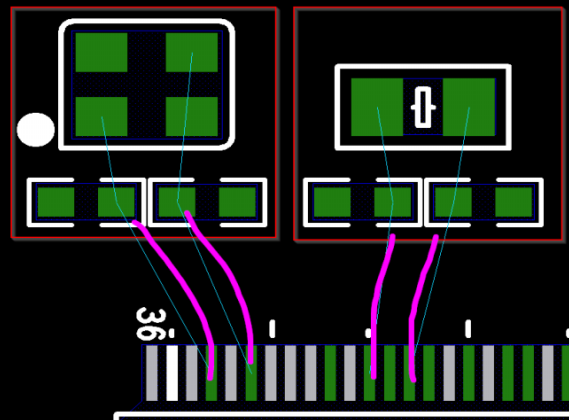

二、晶体电路布局时,两个电容靠近晶体放置 ,布局效果图如下:

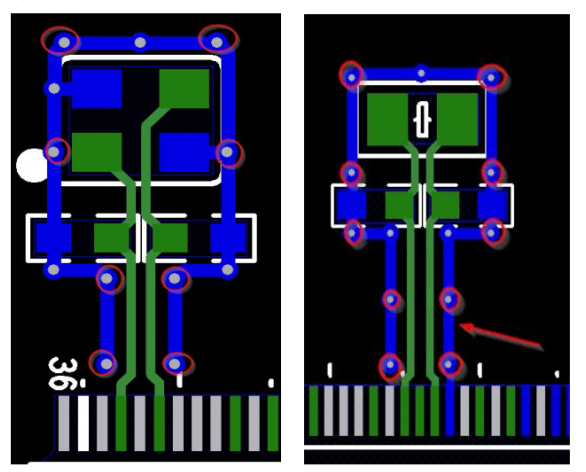

布线时,晶体的一对线要走成 类差分 的形式, 线尽量短 、且要 加粗 并进行 包地处理 , 效

果如下图:

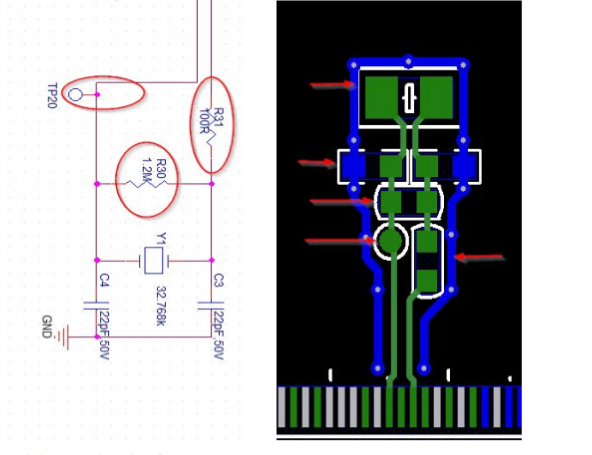

三、上述的是最基本和最常见的晶体电路设计,也有一些变形设计,如加串阻、测试点等,

如下图 ,设计思路还是一致的:

结合上述,布局应注意:

1. 和 IC 布在同一层面,这样可以少打孔;

2. 布局要紧凑,电容位于晶体和 IC 之间,且靠近晶体放置,使时钟线到 IC 尽量

短;

3. 对于有测试点的情况,尽量避免 stub 或者是使 stub 尽量短;

4. 附近不要摆放大功率器件、如电源芯片、 MOS 管、电感等发热量大的器件;

布线应注意:

1. 和 IC 同层布局,同层走线,尽量少打孔,如果打孔,需要在附近加回流地孔;

2. 类差分走线;

3. 走线要加粗,通常 8~12mil; 由于晶体时钟波形为正弦波,所以此处按模拟设计

思路处理;

4. 信号线包地处理,且包地线或者铜皮要打屏蔽地孔;

5. 晶体电路模块区域相当于模拟区域,尽量不要有其他信号穿过;

PCB 模块化布局系列之时钟电路设计 Edited by Kevin

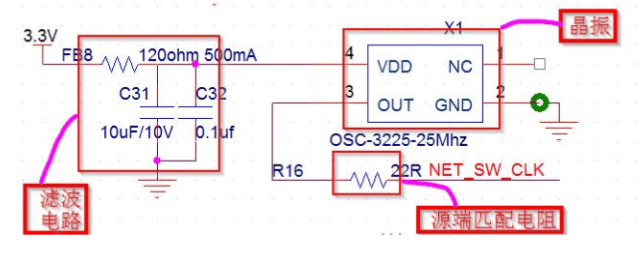

四、晶振

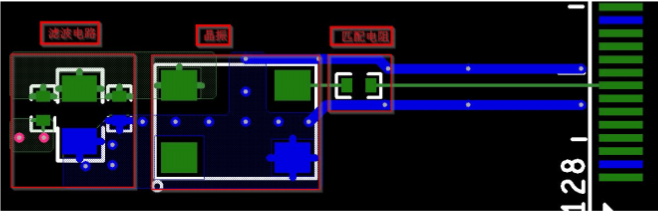

相比于晶体电路,晶振是有源电路,主要由三部分组成:晶振 +电源滤波电路 +源端匹

配电阻:常见电路设计如下图:

布局布线效果图如下:

布局、布线总结:1. 滤波电容靠近电源管脚,遵循先大后小原则摆放,小电容靠得最近;

2. 匹配电阻靠近晶振摆放;如果原理图中没有这个电阻,可建议加上;

3. 附近不要摆放大功率器件、如电源芯片、 MOS 管、电感等发热量大的器件;

4. 时钟线按 50 欧姆阻抗线来走;如果时钟线过长,可以走在内层,打孔换层处加回

流地孔;

5. 其他信号与时钟信号保持 4W 间距;

6. 包地处理,并加屏蔽地孔;

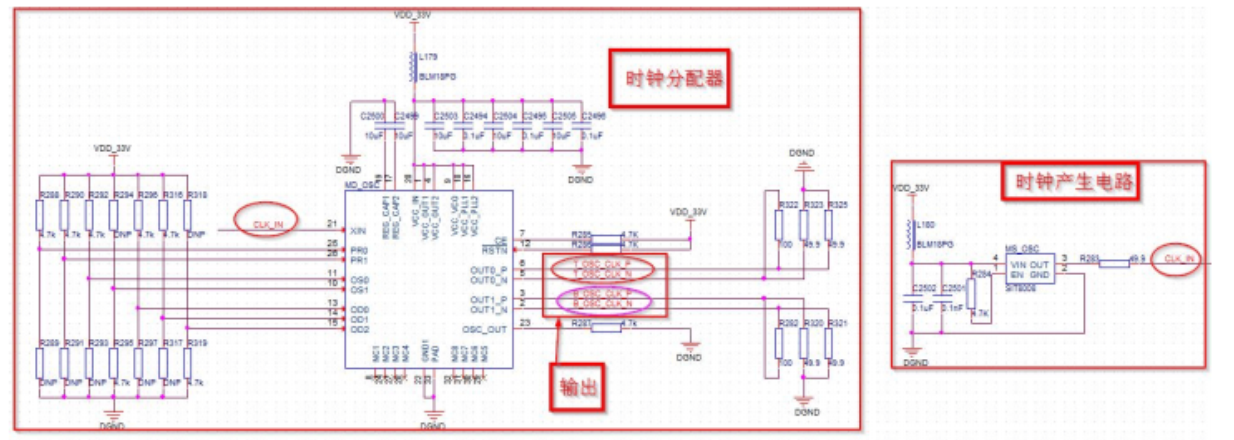

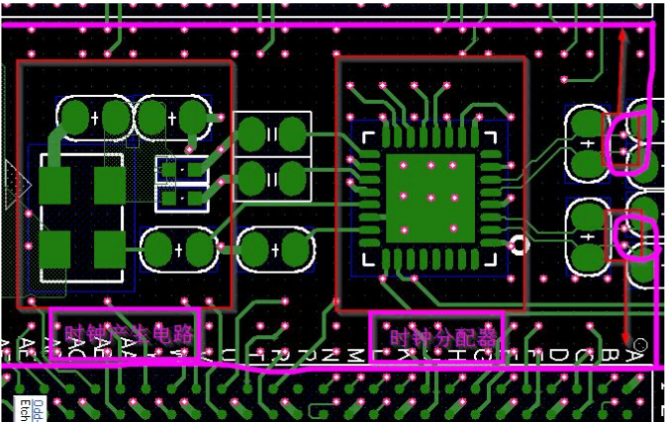

五、时钟分配器

时钟分配器种类比较多,在设计时保证时钟分配器到各个 IC 的距离尽量短,通常放在

对称的位置,例如:

时钟分配器电路:

PCB 设计如下图:

布局、布线总结:

1. 时钟发生电路要靠近时钟分配器,常见的时钟发生电路是晶体、晶振电路;

2. 时钟分配电路放置在对称位置,保证到各个 IC 的时钟信号线路尽量短;

3. 附近不要摆放大功率器件、如电源芯片、 MOS 管、电感等发热量大的器件;

4. 时钟信号线过长时,可以走在内层,换层孔的 200mil 范围内要有回流地过孔;

原文地址:https://wenku.baidu.com/view/51b7dc8126fff705cc170ae0.html