VScode开发STM32/GD32单片机-启动文件分析

用CubeMX软件生成一个makfile工程

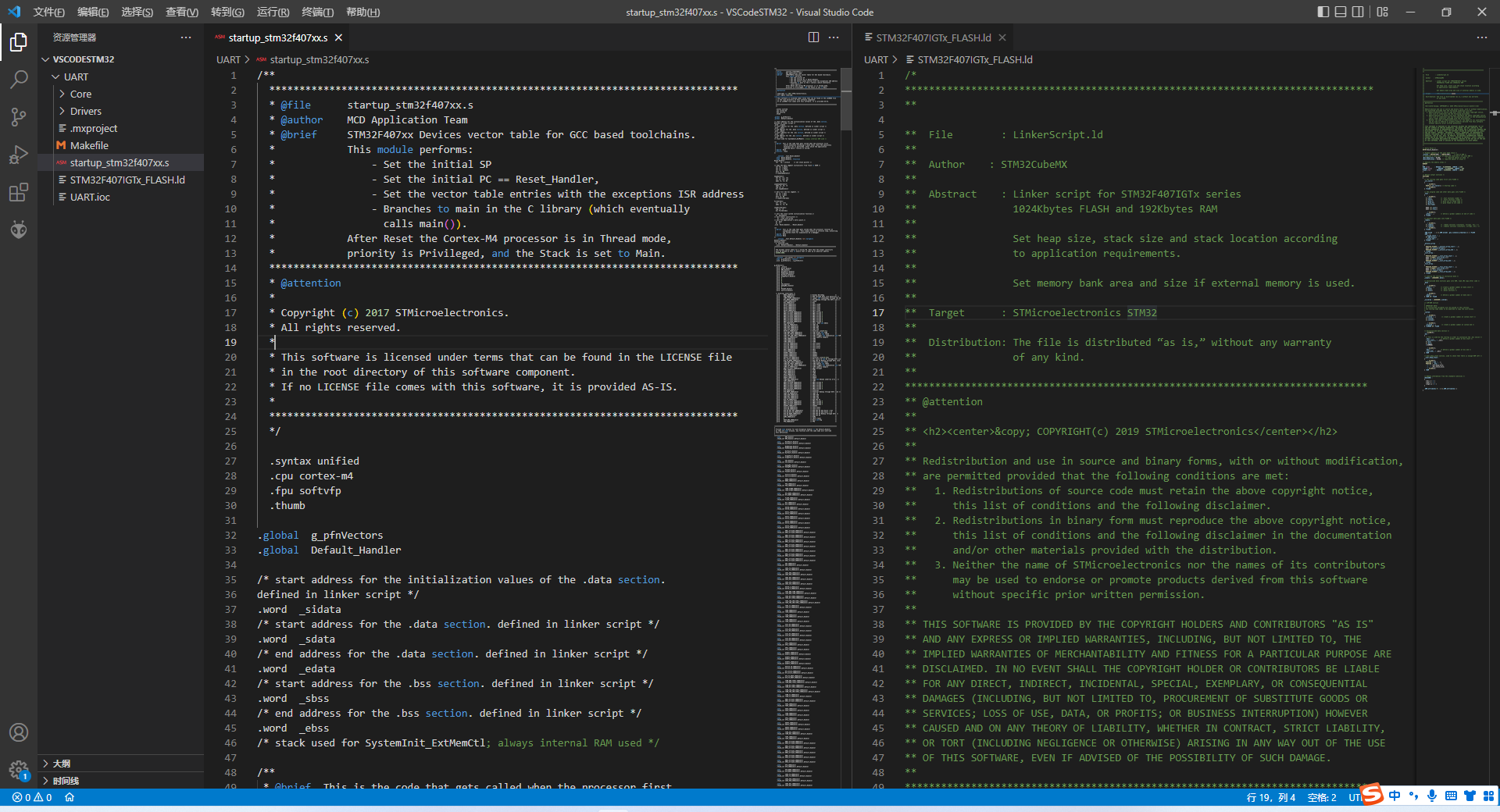

拷贝启动文件代码,一点一点分析

1 /** 2 ****************************************************************************** 3 * @file startup_stm32f407xx.s 4 * @author MCD Application Team 5 * @brief STM32F407xx Devices vector table for GCC based toolchains. 6 * This module performs: 7 * - Set the initial SP 8 * - Set the initial PC == Reset_Handler, 9 * - Set the vector table entries with the exceptions ISR address 10 * - Branches to main in the C library (which eventually 11 * calls main()). 12 * After Reset the Cortex-M4 processor is in Thread mode, 13 * priority is Privileged, and the Stack is set to Main. 14 ****************************************************************************** 15 * @attention 16 * 17 * Copyright (c) 2017 STMicroelectronics. 18 * All rights reserved. 19 * 20 * This software is licensed under terms that can be found in the LICENSE file 21 * in the root directory of this software component. 22 * If no LICENSE file comes with this software, it is provided AS-IS. 23 * 24 ****************************************************************************** 25 */ 26 27 .syntax unified 28 .cpu cortex-m4 29 .fpu softvfp 30 .thumb 31 32 .global g_pfnVectors 33 .global Default_Handler 34 35 /* start address for the initialization values of the .data section. 36 defined in linker script */ 37 .word _sidata 38 /* start address for the .data section. defined in linker script */ 39 .word _sdata 40 /* end address for the .data section. defined in linker script */ 41 .word _edata 42 /* start address for the .bss section. defined in linker script */ 43 .word _sbss 44 /* end address for the .bss section. defined in linker script */ 45 .word _ebss 46 /* stack used for SystemInit_ExtMemCtl; always internal RAM used */ 47 48 /** 49 * @brief This is the code that gets called when the processor first 50 * starts execution following a reset event. Only the absolutely 51 * necessary set is performed, after which the application 52 * supplied main() routine is called. 53 * @param None 54 * @retval : None 55 */ 56 57 .section .text.Reset_Handler 58 .weak Reset_Handler 59 .type Reset_Handler, %function 60 Reset_Handler: 61 ldr sp, =_estack /* set stack pointer */ 62 63 /* Copy the data segment initializers from flash to SRAM */ 64 ldr r0, =_sdata 65 ldr r1, =_edata 66 ldr r2, =_sidata 67 movs r3, #0 68 b LoopCopyDataInit 69 70 CopyDataInit: 71 ldr r4, [r2, r3] 72 str r4, [r0, r3] 73 adds r3, r3, #4 74 75 LoopCopyDataInit: 76 adds r4, r0, r3 77 cmp r4, r1 78 bcc CopyDataInit 79 80 /* Zero fill the bss segment. */ 81 ldr r2, =_sbss 82 ldr r4, =_ebss 83 movs r3, #0 84 b LoopFillZerobss 85 86 FillZerobss: 87 str r3, [r2] 88 adds r2, r2, #4 89 90 LoopFillZerobss: 91 cmp r2, r4 92 bcc FillZerobss 93 94 /* Call the clock system initialization function.*/ 95 bl SystemInit 96 /* Call static constructors */ 97 bl __libc_init_array 98 /* Call the application's entry point.*/ 99 bl main 100 bx lr 101 .size Reset_Handler, .-Reset_Handler 102 103 /** 104 * @brief This is the code that gets called when the processor receives an 105 * unexpected interrupt. This simply enters an infinite loop, preserving 106 * the system state for examination by a debugger. 107 * @param None 108 * @retval None 109 */ 110 .section .text.Default_Handler,"ax",%progbits 111 Default_Handler: 112 Infinite_Loop: 113 b Infinite_Loop 114 .size Default_Handler, .-Default_Handler 115 /****************************************************************************** 116 * 117 * The minimal vector table for a Cortex M3. Note that the proper constructs 118 * must be placed on this to ensure that it ends up at physical address 119 * 0x0000.0000. 120 * 121 *******************************************************************************/ 122 .section .isr_vector,"a",%progbits 123 .type g_pfnVectors, %object 124 .size g_pfnVectors, .-g_pfnVectors 125 126 127 g_pfnVectors: 128 .word _estack 129 .word Reset_Handler 130 .word NMI_Handler 131 .word HardFault_Handler 132 .word MemManage_Handler 133 .word BusFault_Handler 134 .word UsageFault_Handler 135 .word 0 136 .word 0 137 .word 0 138 .word 0 139 .word SVC_Handler 140 .word DebugMon_Handler 141 .word 0 142 .word PendSV_Handler 143 .word SysTick_Handler 144 145 /* External Interrupts */ 146 .word WWDG_IRQHandler /* Window WatchDog */ 147 .word PVD_IRQHandler /* PVD through EXTI Line detection */ 148 .word TAMP_STAMP_IRQHandler /* Tamper and TimeStamps through the EXTI line */ 149 .word RTC_WKUP_IRQHandler /* RTC Wakeup through the EXTI line */ 150 .word FLASH_IRQHandler /* FLASH */ 151 .word RCC_IRQHandler /* RCC */ 152 .word EXTI0_IRQHandler /* EXTI Line0 */ 153 .word EXTI1_IRQHandler /* EXTI Line1 */ 154 .word EXTI2_IRQHandler /* EXTI Line2 */ 155 .word EXTI3_IRQHandler /* EXTI Line3 */ 156 .word EXTI4_IRQHandler /* EXTI Line4 */ 157 .word DMA1_Stream0_IRQHandler /* DMA1 Stream 0 */ 158 .word DMA1_Stream1_IRQHandler /* DMA1 Stream 1 */ 159 .word DMA1_Stream2_IRQHandler /* DMA1 Stream 2 */ 160 .word DMA1_Stream3_IRQHandler /* DMA1 Stream 3 */ 161 .word DMA1_Stream4_IRQHandler /* DMA1 Stream 4 */ 162 .word DMA1_Stream5_IRQHandler /* DMA1 Stream 5 */ 163 .word DMA1_Stream6_IRQHandler /* DMA1 Stream 6 */ 164 .word ADC_IRQHandler /* ADC1, ADC2 and ADC3s */ 165 .word CAN1_TX_IRQHandler /* CAN1 TX */ 166 .word CAN1_RX0_IRQHandler /* CAN1 RX0 */ 167 .word CAN1_RX1_IRQHandler /* CAN1 RX1 */ 168 .word CAN1_SCE_IRQHandler /* CAN1 SCE */ 169 .word EXTI9_5_IRQHandler /* External Line[9:5]s */ 170 .word TIM1_BRK_TIM9_IRQHandler /* TIM1 Break and TIM9 */ 171 .word TIM1_UP_TIM10_IRQHandler /* TIM1 Update and TIM10 */ 172 .word TIM1_TRG_COM_TIM11_IRQHandler /* TIM1 Trigger and Commutation and TIM11 */ 173 .word TIM1_CC_IRQHandler /* TIM1 Capture Compare */ 174 .word TIM2_IRQHandler /* TIM2 */ 175 .word TIM3_IRQHandler /* TIM3 */ 176 .word TIM4_IRQHandler /* TIM4 */ 177 .word I2C1_EV_IRQHandler /* I2C1 Event */ 178 .word I2C1_ER_IRQHandler /* I2C1 Error */ 179 .word I2C2_EV_IRQHandler /* I2C2 Event */ 180 .word I2C2_ER_IRQHandler /* I2C2 Error */ 181 .word SPI1_IRQHandler /* SPI1 */ 182 .word SPI2_IRQHandler /* SPI2 */ 183 .word USART1_IRQHandler /* USART1 */ 184 .word USART2_IRQHandler /* USART2 */ 185 .word USART3_IRQHandler /* USART3 */ 186 .word EXTI15_10_IRQHandler /* External Line[15:10]s */ 187 .word RTC_Alarm_IRQHandler /* RTC Alarm (A and B) through EXTI Line */ 188 .word OTG_FS_WKUP_IRQHandler /* USB OTG FS Wakeup through EXTI line */ 189 .word TIM8_BRK_TIM12_IRQHandler /* TIM8 Break and TIM12 */ 190 .word TIM8_UP_TIM13_IRQHandler /* TIM8 Update and TIM13 */ 191 .word TIM8_TRG_COM_TIM14_IRQHandler /* TIM8 Trigger and Commutation and TIM14 */ 192 .word TIM8_CC_IRQHandler /* TIM8 Capture Compare */ 193 .word DMA1_Stream7_IRQHandler /* DMA1 Stream7 */ 194 .word FSMC_IRQHandler /* FSMC */ 195 .word SDIO_IRQHandler /* SDIO */ 196 .word TIM5_IRQHandler /* TIM5 */ 197 .word SPI3_IRQHandler /* SPI3 */ 198 .word UART4_IRQHandler /* UART4 */ 199 .word UART5_IRQHandler /* UART5 */ 200 .word TIM6_DAC_IRQHandler /* TIM6 and DAC1&2 underrun errors */ 201 .word TIM7_IRQHandler /* TIM7 */ 202 .word DMA2_Stream0_IRQHandler /* DMA2 Stream 0 */ 203 .word DMA2_Stream1_IRQHandler /* DMA2 Stream 1 */ 204 .word DMA2_Stream2_IRQHandler /* DMA2 Stream 2 */ 205 .word DMA2_Stream3_IRQHandler /* DMA2 Stream 3 */ 206 .word DMA2_Stream4_IRQHandler /* DMA2 Stream 4 */ 207 .word ETH_IRQHandler /* Ethernet */ 208 .word ETH_WKUP_IRQHandler /* Ethernet Wakeup through EXTI line */ 209 .word CAN2_TX_IRQHandler /* CAN2 TX */ 210 .word CAN2_RX0_IRQHandler /* CAN2 RX0 */ 211 .word CAN2_RX1_IRQHandler /* CAN2 RX1 */ 212 .word CAN2_SCE_IRQHandler /* CAN2 SCE */ 213 .word OTG_FS_IRQHandler /* USB OTG FS */ 214 .word DMA2_Stream5_IRQHandler /* DMA2 Stream 5 */ 215 .word DMA2_Stream6_IRQHandler /* DMA2 Stream 6 */ 216 .word DMA2_Stream7_IRQHandler /* DMA2 Stream 7 */ 217 .word USART6_IRQHandler /* USART6 */ 218 .word I2C3_EV_IRQHandler /* I2C3 event */ 219 .word I2C3_ER_IRQHandler /* I2C3 error */ 220 .word OTG_HS_EP1_OUT_IRQHandler /* USB OTG HS End Point 1 Out */ 221 .word OTG_HS_EP1_IN_IRQHandler /* USB OTG HS End Point 1 In */ 222 .word OTG_HS_WKUP_IRQHandler /* USB OTG HS Wakeup through EXTI */ 223 .word OTG_HS_IRQHandler /* USB OTG HS */ 224 .word DCMI_IRQHandler /* DCMI */ 225 .word 0 /* CRYP crypto */ 226 .word HASH_RNG_IRQHandler /* Hash and Rng */ 227 .word FPU_IRQHandler /* FPU */ 228 229 230 /******************************************************************************* 231 * 232 * Provide weak aliases for each Exception handler to the Default_Handler. 233 * As they are weak aliases, any function with the same name will override 234 * this definition. 235 * 236 *******************************************************************************/ 237 .weak NMI_Handler 238 .thumb_set NMI_Handler,Default_Handler 239 240 .weak HardFault_Handler 241 .thumb_set HardFault_Handler,Default_Handler 242 243 .weak MemManage_Handler 244 .thumb_set MemManage_Handler,Default_Handler 245 246 .weak BusFault_Handler 247 .thumb_set BusFault_Handler,Default_Handler 248 249 .weak UsageFault_Handler 250 .thumb_set UsageFault_Handler,Default_Handler 251 252 .weak SVC_Handler 253 .thumb_set SVC_Handler,Default_Handler 254 255 .weak DebugMon_Handler 256 .thumb_set DebugMon_Handler,Default_Handler 257 258 .weak PendSV_Handler 259 .thumb_set PendSV_Handler,Default_Handler 260 261 .weak SysTick_Handler 262 .thumb_set SysTick_Handler,Default_Handler 263 264 .weak WWDG_IRQHandler 265 .thumb_set WWDG_IRQHandler,Default_Handler 266 267 .weak PVD_IRQHandler 268 .thumb_set PVD_IRQHandler,Default_Handler 269 270 .weak TAMP_STAMP_IRQHandler 271 .thumb_set TAMP_STAMP_IRQHandler,Default_Handler 272 273 .weak RTC_WKUP_IRQHandler 274 .thumb_set RTC_WKUP_IRQHandler,Default_Handler 275 276 .weak FLASH_IRQHandler 277 .thumb_set FLASH_IRQHandler,Default_Handler 278 279 .weak RCC_IRQHandler 280 .thumb_set RCC_IRQHandler,Default_Handler 281 282 .weak EXTI0_IRQHandler 283 .thumb_set EXTI0_IRQHandler,Default_Handler 284 285 .weak EXTI1_IRQHandler 286 .thumb_set EXTI1_IRQHandler,Default_Handler 287 288 .weak EXTI2_IRQHandler 289 .thumb_set EXTI2_IRQHandler,Default_Handler 290 291 .weak EXTI3_IRQHandler 292 .thumb_set EXTI3_IRQHandler,Default_Handler 293 294 .weak EXTI4_IRQHandler 295 .thumb_set EXTI4_IRQHandler,Default_Handler 296 297 .weak DMA1_Stream0_IRQHandler 298 .thumb_set DMA1_Stream0_IRQHandler,Default_Handler 299 300 .weak DMA1_Stream1_IRQHandler 301 .thumb_set DMA1_Stream1_IRQHandler,Default_Handler 302 303 .weak DMA1_Stream2_IRQHandler 304 .thumb_set DMA1_Stream2_IRQHandler,Default_Handler 305 306 .weak DMA1_Stream3_IRQHandler 307 .thumb_set DMA1_Stream3_IRQHandler,Default_Handler 308 309 .weak DMA1_Stream4_IRQHandler 310 .thumb_set DMA1_Stream4_IRQHandler,Default_Handler 311 312 .weak DMA1_Stream5_IRQHandler 313 .thumb_set DMA1_Stream5_IRQHandler,Default_Handler 314 315 .weak DMA1_Stream6_IRQHandler 316 .thumb_set DMA1_Stream6_IRQHandler,Default_Handler 317 318 .weak ADC_IRQHandler 319 .thumb_set ADC_IRQHandler,Default_Handler 320 321 .weak CAN1_TX_IRQHandler 322 .thumb_set CAN1_TX_IRQHandler,Default_Handler 323 324 .weak CAN1_RX0_IRQHandler 325 .thumb_set CAN1_RX0_IRQHandler,Default_Handler 326 327 .weak CAN1_RX1_IRQHandler 328 .thumb_set CAN1_RX1_IRQHandler,Default_Handler 329 330 .weak CAN1_SCE_IRQHandler 331 .thumb_set CAN1_SCE_IRQHandler,Default_Handler 332 333 .weak EXTI9_5_IRQHandler 334 .thumb_set EXTI9_5_IRQHandler,Default_Handler 335 336 .weak TIM1_BRK_TIM9_IRQHandler 337 .thumb_set TIM1_BRK_TIM9_IRQHandler,Default_Handler 338 339 .weak TIM1_UP_TIM10_IRQHandler 340 .thumb_set TIM1_UP_TIM10_IRQHandler,Default_Handler 341 342 .weak TIM1_TRG_COM_TIM11_IRQHandler 343 .thumb_set TIM1_TRG_COM_TIM11_IRQHandler,Default_Handler 344 345 .weak TIM1_CC_IRQHandler 346 .thumb_set TIM1_CC_IRQHandler,Default_Handler 347 348 .weak TIM2_IRQHandler 349 .thumb_set TIM2_IRQHandler,Default_Handler 350 351 .weak TIM3_IRQHandler 352 .thumb_set TIM3_IRQHandler,Default_Handler 353 354 .weak TIM4_IRQHandler 355 .thumb_set TIM4_IRQHandler,Default_Handler 356 357 .weak I2C1_EV_IRQHandler 358 .thumb_set I2C1_EV_IRQHandler,Default_Handler 359 360 .weak I2C1_ER_IRQHandler 361 .thumb_set I2C1_ER_IRQHandler,Default_Handler 362 363 .weak I2C2_EV_IRQHandler 364 .thumb_set I2C2_EV_IRQHandler,Default_Handler 365 366 .weak I2C2_ER_IRQHandler 367 .thumb_set I2C2_ER_IRQHandler,Default_Handler 368 369 .weak SPI1_IRQHandler 370 .thumb_set SPI1_IRQHandler,Default_Handler 371 372 .weak SPI2_IRQHandler 373 .thumb_set SPI2_IRQHandler,Default_Handler 374 375 .weak USART1_IRQHandler 376 .thumb_set USART1_IRQHandler,Default_Handler 377 378 .weak USART2_IRQHandler 379 .thumb_set USART2_IRQHandler,Default_Handler 380 381 .weak USART3_IRQHandler 382 .thumb_set USART3_IRQHandler,Default_Handler 383 384 .weak EXTI15_10_IRQHandler 385 .thumb_set EXTI15_10_IRQHandler,Default_Handler 386 387 .weak RTC_Alarm_IRQHandler 388 .thumb_set RTC_Alarm_IRQHandler,Default_Handler 389 390 .weak OTG_FS_WKUP_IRQHandler 391 .thumb_set OTG_FS_WKUP_IRQHandler,Default_Handler 392 393 .weak TIM8_BRK_TIM12_IRQHandler 394 .thumb_set TIM8_BRK_TIM12_IRQHandler,Default_Handler 395 396 .weak TIM8_UP_TIM13_IRQHandler 397 .thumb_set TIM8_UP_TIM13_IRQHandler,Default_Handler 398 399 .weak TIM8_TRG_COM_TIM14_IRQHandler 400 .thumb_set TIM8_TRG_COM_TIM14_IRQHandler,Default_Handler 401 402 .weak TIM8_CC_IRQHandler 403 .thumb_set TIM8_CC_IRQHandler,Default_Handler 404 405 .weak DMA1_Stream7_IRQHandler 406 .thumb_set DMA1_Stream7_IRQHandler,Default_Handler 407 408 .weak FSMC_IRQHandler 409 .thumb_set FSMC_IRQHandler,Default_Handler 410 411 .weak SDIO_IRQHandler 412 .thumb_set SDIO_IRQHandler,Default_Handler 413 414 .weak TIM5_IRQHandler 415 .thumb_set TIM5_IRQHandler,Default_Handler 416 417 .weak SPI3_IRQHandler 418 .thumb_set SPI3_IRQHandler,Default_Handler 419 420 .weak UART4_IRQHandler 421 .thumb_set UART4_IRQHandler,Default_Handler 422 423 .weak UART5_IRQHandler 424 .thumb_set UART5_IRQHandler,Default_Handler 425 426 .weak TIM6_DAC_IRQHandler 427 .thumb_set TIM6_DAC_IRQHandler,Default_Handler 428 429 .weak TIM7_IRQHandler 430 .thumb_set TIM7_IRQHandler,Default_Handler 431 432 .weak DMA2_Stream0_IRQHandler 433 .thumb_set DMA2_Stream0_IRQHandler,Default_Handler 434 435 .weak DMA2_Stream1_IRQHandler 436 .thumb_set DMA2_Stream1_IRQHandler,Default_Handler 437 438 .weak DMA2_Stream2_IRQHandler 439 .thumb_set DMA2_Stream2_IRQHandler,Default_Handler 440 441 .weak DMA2_Stream3_IRQHandler 442 .thumb_set DMA2_Stream3_IRQHandler,Default_Handler 443 444 .weak DMA2_Stream4_IRQHandler 445 .thumb_set DMA2_Stream4_IRQHandler,Default_Handler 446 447 .weak ETH_IRQHandler 448 .thumb_set ETH_IRQHandler,Default_Handler 449 450 .weak ETH_WKUP_IRQHandler 451 .thumb_set ETH_WKUP_IRQHandler,Default_Handler 452 453 .weak CAN2_TX_IRQHandler 454 .thumb_set CAN2_TX_IRQHandler,Default_Handler 455 456 .weak CAN2_RX0_IRQHandler 457 .thumb_set CAN2_RX0_IRQHandler,Default_Handler 458 459 .weak CAN2_RX1_IRQHandler 460 .thumb_set CAN2_RX1_IRQHandler,Default_Handler 461 462 .weak CAN2_SCE_IRQHandler 463 .thumb_set CAN2_SCE_IRQHandler,Default_Handler 464 465 .weak OTG_FS_IRQHandler 466 .thumb_set OTG_FS_IRQHandler,Default_Handler 467 468 .weak DMA2_Stream5_IRQHandler 469 .thumb_set DMA2_Stream5_IRQHandler,Default_Handler 470 471 .weak DMA2_Stream6_IRQHandler 472 .thumb_set DMA2_Stream6_IRQHandler,Default_Handler 473 474 .weak DMA2_Stream7_IRQHandler 475 .thumb_set DMA2_Stream7_IRQHandler,Default_Handler 476 477 .weak USART6_IRQHandler 478 .thumb_set USART6_IRQHandler,Default_Handler 479 480 .weak I2C3_EV_IRQHandler 481 .thumb_set I2C3_EV_IRQHandler,Default_Handler 482 483 .weak I2C3_ER_IRQHandler 484 .thumb_set I2C3_ER_IRQHandler,Default_Handler 485 486 .weak OTG_HS_EP1_OUT_IRQHandler 487 .thumb_set OTG_HS_EP1_OUT_IRQHandler,Default_Handler 488 489 .weak OTG_HS_EP1_IN_IRQHandler 490 .thumb_set OTG_HS_EP1_IN_IRQHandler,Default_Handler 491 492 .weak OTG_HS_WKUP_IRQHandler 493 .thumb_set OTG_HS_WKUP_IRQHandler,Default_Handler 494 495 .weak OTG_HS_IRQHandler 496 .thumb_set OTG_HS_IRQHandler,Default_Handler 497 498 .weak DCMI_IRQHandler 499 .thumb_set DCMI_IRQHandler,Default_Handler 500 501 .weak HASH_RNG_IRQHandler 502 .thumb_set HASH_RNG_IRQHandler,Default_Handler 503 504 .weak FPU_IRQHandler 505 .thumb_set FPU_IRQHandler,Default_Handler

27 .syntax unified 28 .cpu cortex-m4 29 .fpu softvfp 30 .thumb

.syntax unified 是一个指示,默认值divided(分裂的) 旧样式。unified (统一的)新样式,下面的指令使用ARM和THUMB通用格式。

.cpu 是指后边用到的CPU平台cortex-m4

.fup 表示后面使用的是软浮点,软浮点即Soft-float,浮点单元即VFP

.thumb 使用thumb模式等价于 .code 16;gcc -mthumb

.global 定义了全局符号 使得该符号对 .ld 链接文件可见。

g_pfnVectors 既中断向量表

Default_Handler 错误中断

35 /* start address for the initialization values of the .data section. 36 defined in linker script */ 37 .word _sidata 38 /* start address for the .data section. defined in linker script */ 39 .word _sdata 40 /* end address for the .data section. defined in linker script */ 41 .word _edata 42 /* start address for the .bss section. defined in linker script */ 43 .word _sbss 44 /* end address for the .bss section. defined in linker script */ 45 .word _ebss 46 /* stack used for SystemInit_ExtMemCtl; always internal RAM used */

.word 表示当前位置放一个Word型的值 这个变量同样对链接文件可见

定义的变量分为:_sidata 带初始化值得.data段起始地址

_sdata:.data段起始地址

_edata:.data段结束地址

_sbss:.data段起始地址

_ebss:.data段结束地址

注释中的SystemInit_ExtMemCtl表示配置外部RAM

57 .section .text.Reset_Handler 58 .weak Reset_Handler 59 .type Reset_Handler, %function 60 Reset_Handler: 61 ldr sp, =_estack /* set stack pointer */ 62 63 /* Copy the data segment initializers from flash to SRAM */ 64 ldr r0, =_sdata 65 ldr r1, =_edata 66 ldr r2, =_sidata 67 movs r3, #0 68 b LoopCopyDataInit 69 70 CopyDataInit: 71 ldr r4, [r2, r3] 72 str r4, [r0, r3] 73 adds r3, r3, #4 74 75 LoopCopyDataInit: 76 adds r4, r0, r3 77 cmp r4, r1 78 bcc CopyDataInit 79 80 /* Zero fill the bss segment. */ 81 ldr r2, =_sbss 82 ldr r4, =_ebss 83 movs r3, #0 84 b LoopFillZerobss 85 86 FillZerobss: 87 str r3, [r2] 88 adds r2, r2, #4 89 90 LoopFillZerobss: 91 cmp r2, r4 92 bcc FillZerobss 93 94 /* Call the clock system initialization function.*/ 95 bl SystemInit 96 /* Call static constructors */ 97 bl __libc_init_array 98 /* Call the application's entry point.*/ 99 bl main 100 bx lr 101 .size Reset_Handler, .-Reset_Handler

以上代码是在芯片第一次启动或者复位后,执行一些必要的操作,此后再启动main函数执行。

.weak Reset_Handler是指弱定义,当我们定义一个Reset_Handler函数时候,这部分将不起作用。

.type Reset_Handler, %function 表示设置的符号是函数名称

后边是函数的定义

110 .section .text.Default_Handler,"ax",%progbits 111 Default_Handler: 112 Infinite_Loop: 113 b Infinite_Loop 114 .size Default_Handler, .-Default_Handler

上边的代码表示如果遇到一个未知的中断,将进入到如下这个死循环中也就是进入Defult_Handler

122 .section .isr_vector,"a",%progbits 123 .type g_pfnVectors, %object 124 .size g_pfnVectors, .-g_pfnVectors 125 126 127 g_pfnVectors: 128 .word _estack 129 .word Reset_Handler 130 .word NMI_Handler 中间省略 225 .word 0 /* CRYP crypto */ 226 .word HASH_RNG_IRQHandler /* Hash and Rng */ 227 .word FPU_IRQHandler /* FPU */ 228 229 230 /******************************************************************************* 231 * 232 * Provide weak aliases for each Exception handler to the Default_Handler. 233 * As they are weak aliases, any function with the same name will override 234 * this definition. 235 * 236 *******************************************************************************/ 237 .weak NMI_Handler 238 .thumb_set NMI_Handler,Default_Handler 中间省略 504 .weak FPU_IRQHandler 505 .thumb_set FPU_IRQHandler,Default_Handler

.section .isr_vector. "a", %progbits :定义中断向量和它的类型,a表示可分配,%progbits表示段内包含数据。

.type g_pfnVectors, %object 段符号名字为g_pfnVectors,%object表示符号为数据对象

.size g_pfnVectors,.-g_pfnVectors表示大小是从当前位置到定义位置

.word _estack表示在当前位置放置一个Word型的值,这个值是 _estack,其它同理

.thumb_set NMI_Handler,Default_Handler 等效于.set指令。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 【译】Visual Studio 中新的强大生产力特性

· 10年+ .NET Coder 心语 ── 封装的思维:从隐藏、稳定开始理解其本质意义

· 【设计模式】告别冗长if-else语句:使用策略模式优化代码结构