Verilog中的real类型及注意事项

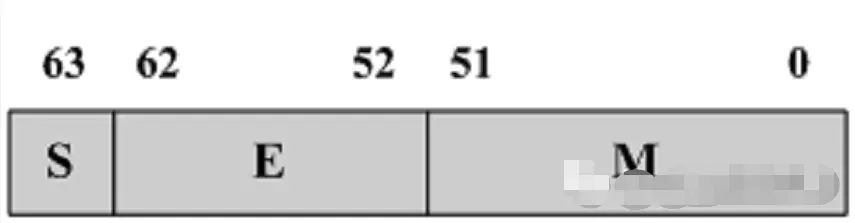

Verilog中的real类型变量为双精度浮点数,且符合IEEE Std754-1985对双精度浮点数的规定,即双精度浮点数为64位,其中1位符号位,11位指数位,53位尾数(其中包含1位隐含位).在IEEE Std 754-1985中一般用{S、E、M}对双精度浮点数进行描述,一个64位双精度浮点数的表示格式如下:

其中S为符号位占1位,E为指数位占11位,M为尾数位占52位,这里需要注意的是尾数位还有一个隐含位(具体取值可参考IEEE Std 754-1985).在具体仿真过程中观测到的数据需要通过相应的运算转换后可以得到对应IEEE Std 754-1985标准中指定的数据格式.但是在具体仿真的时候如果没有对浮点数进行合理的处理和使用将会引起不仿真结果可能与预期不符,那么进行浮点数算术计算时需要注意哪些问题呢?本文将以具体示例进行说明.

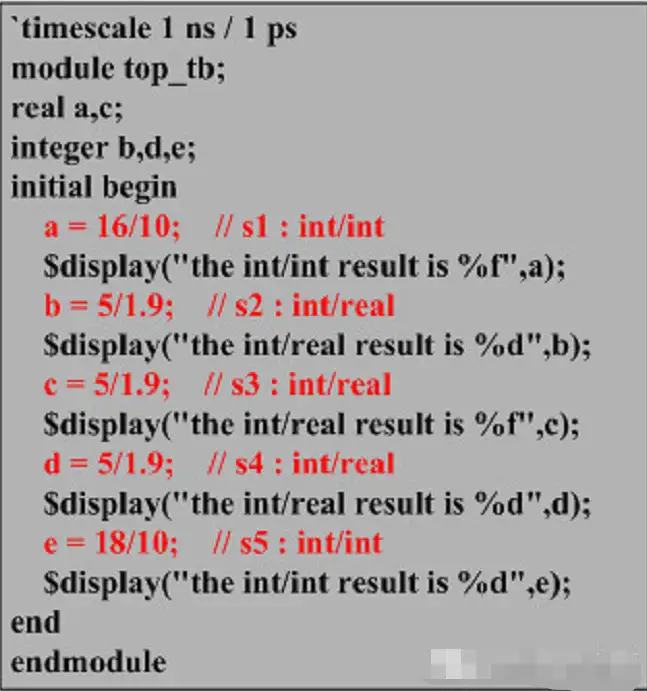

【示例】

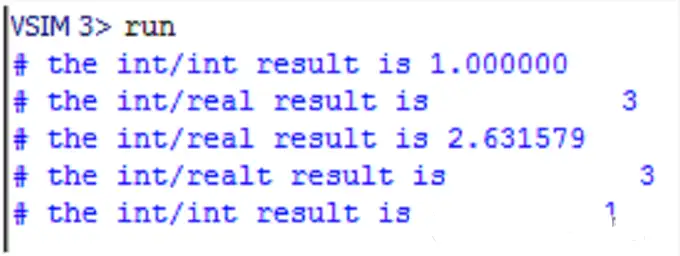

仿真结果如下:

s1中两个操作数为整数,相除的结果虽然为浮点数,但是按照Verilog中整数除法的约定,两个整数相除的结果仍为整数,如果结果不能除尽,那么将会对小数部分进行截位操作,即相除的结果为1,最终浮点类型变量a的值为1.000000;s2~s4中进行除法操作的操作数一个为浮点类型,一个为整型,在进行运算之前两个操作数会转换为同一种数据类型(本例中为浮点类型,具体转换规则可参考C语言中关于类型运算转换的描述),然后进行除法操作,除法操作的结果为浮点数,在s2中,该浮点数结果将被赋值给一个整型变量,所以在具体赋值前将会将运算得到的浮点数按照"就近原则"转换为整数型数据(注意不是四舍五入),当结果小数部分小于等于0.5时,将会被截除,大于0.5时将会进位为"1";s3中,因为c本身为real类型,所以运算结果不需要转换处理即可输出;s4同s2;s5计算结果同s1,运算结果赋值给整型变量,所以除法操作后的结果不需要经过处理.

可见,在除法算术运算时需要合理使用相关的操作数.在Verilog中,如果两个操作数都为整型数据,那么计算结果将按照整型数据处理;如果两个操作数中有整型也有浮点类型,那么在进行运算前会将整型数据转换为对应的浮点类型数据后再进行计算,同时对计算结果按照浮点数运算规则进行处理.为此在具体使用real时需要注意以下几点:

1.不能在posedge和negedge中使用实型变量;

2.不能在矢量的位选中使用实型变量;

3.不能将要进行位选操作的变量声明为实型;

4.实型变量在声明的时候不能指定数据范围;

5.实型变量的初始默认值为0;

6.将real变量赋值给整型变量,real将按照"就近原则"处理后赋值给整型变量;

7.如果两个整型变量进行除法操作,操作后的结果存在小数部分,那么小数部分将会被截除转换为对应的整型数据;

8.Verilog中并不是所有的运算符都支持操作数为实型变量,具体支持情况如下表:

【支持实型数据的运算如下表】

虽然注意,虽然实型数据可以使用关系运算符和逻辑运算符,但是计算结果只能是1位标量,用以表示结果真假.

【支持实型数据的运算如下表】

浙公网安备 33010602011771号

浙公网安备 33010602011771号