基于FPGA的简易乘法器设计

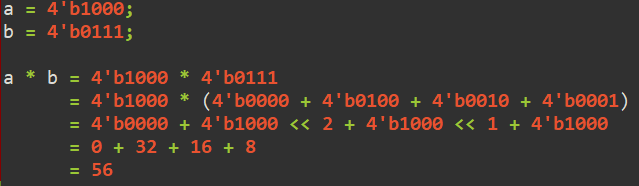

核心思想是进行因式分解,因式分解之后移位运算,最后再作加法运算,如下所示:

code:

1 module cheng_fa( 2 input clk , 3 input rst_n , 4 5 input [ 7:0] data_1 , // 8'b0000_0111; 6 input [ 7:0] data_2 , // 8'b0000_1000; 7 8 output [15:0] Multip 9 ); 10 11 //========================================================================\ 12 // =========== Define Parameter and Internal signals =========== 13 //========================================================================/ 14 15 integer i ; 16 reg [15:0] x1 ; 17 reg [15:0] x2 ; 18 reg [15:0] x3 ; 19 reg [15:0] x4 ; 20 reg [15:0] x5 ; 21 reg [15:0] x6 ; 22 reg [15:0] x7 ; 23 reg [15:0] x8 ; 24 25 //============================================================================= 26 //**************************** Main Code ******************************* 27 //============================================================================= 28 29 always @(*) begin 30 if(!rst_n) begin 31 x1 = 16'd0; 32 x2 = 16'd0; 33 x3 = 16'd0; 34 x4 = 16'd0; 35 x5 = 16'd0; 36 x6 = 16'd0; 37 x7 = 16'd0; 38 x8 = 16'd0; 39 end 40 else begin 41 for(i=1; i<=8; i=i+1) begin 42 case(i) 43 1: x1 = (data_1[i-1] == 1'b1) ? data_2 : 0; 44 2: x2 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 45 3: x3 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 46 4: x4 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 47 5: x5 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 48 6: x6 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 49 7: x7 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 50 8: x8 = (data_1[i-1] == 1'b1) ? data_2 << (i-1) : 0; 51 default:; 52 endcase 53 end 54 end 55 end 56 57 assign Multip = x1 + x2 + x3 + x4 + x5 + x6 + x7 + x8; 58 59 endmodule

testbench code:

1 `timescale 1ns/1ps 2 3 module cheng_fa_tb; 4 reg clk ; 5 reg rst_n ; 6 7 reg [ 7:0] data_1 ; // 8'b0000_0111; 8 reg [ 7:0] data_2 ; // 8'b0000_1000; 9 10 wire [15:0] Multip ; 11 12 cheng_fa cheng_fa_inst( 13 .clk ( clk ), 14 .rst_n ( rst_n ), 15 .data_1 ( data_1 ), 16 .data_2 ( data_2 ), 17 .Multip ( Multip ) 18 ); 19 20 /* 21 initial 22 begin 23 $dumpfile("wave.vcd"); 24 $dumpvars(0,cheng_fa_tb); 25 end 26 */ 27 28 initial 29 clk = 1'b0; 30 always #10 clk = ~clk; 31 32 initial 33 begin 34 #1; 35 rst_n = 1'b0; 36 data_1 = 8'd0; 37 data_2 = 8'd0; 38 #21; 39 rst_n = 1'b1; 40 #25; 41 42 data_1 = 8'd7; 43 data_2 = 8'd8; 44 45 #1000; 46 47 data_1 = 8'd12; 48 data_2 = 8'd30; 49 #1000; 50 51 $stop; 52 end 53 54 endmodule

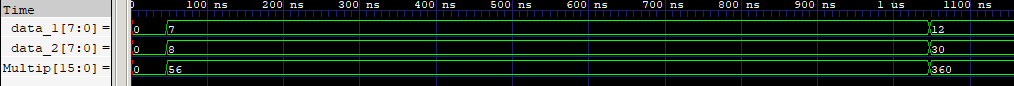

仿真: