二进制转格雷码

一、前言

格雷码计数器可以运用于FIFO中。格雷码计数器的优势在于其相邻两个数值之间只有一位发生变化,提高了系统的抗干扰能力,而且在计数时,各个输出的门电路翻转次数要远远小于二进制计数器,从而可以大幅度的降低系统的功耗。

二、二进制转格雷码的原理

由表可知,格雷码相邻两个数之间只有一位会改变。

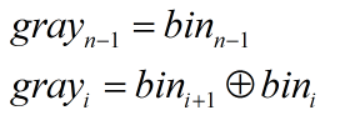

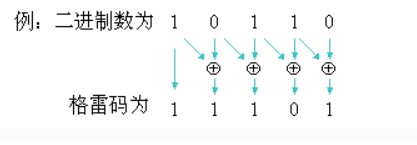

数学原理:

格雷码的最高位和二进制的最高位保持不变,然后二进制的最高位和次高位相异或得到格雷码的次高位,其他各位依次类推。

三、代码实现

1 // ********************************************************************************* 2 // Project Name : bin_gray 3 // Email : 4 // Create Time : 2020/07/22 10:46 5 // Module Name : bin_gray 6 // editor : L 7 // Version : Rev1.0.0 8 // ********************************************************************************* 9 10 module bin_gray( 11 input sclk, 12 input s_rst_n, 13 input en, 14 output reg [7:0] gray_out 15 ); 16 17 reg [7:0] cnt; 18 19 always @(posedge sclk or negedge s_rst_n) begin 20 if(!s_rst_n) begin 21 cnt <= 0; 22 end 23 else if(en) begin 24 cnt <= cnt + 1'b1; 25 end 26 else begin 27 cnt <= cnt; 28 end 29 end 30 31 always @ (posedge sclk or negedge s_rst_n) begin 32 if(s_rst_n == 1'b0) 33 gray_out <= 0; 34 else 35 gray_out <= cnt ^ (cnt >> 1); 36 end 37 38 endmodule

testbench:

1 // ********************************************************************************* 2 // Project Name : bin2gray 3 // Email : 4 // Create Time : 2020/07/24 9:25 5 // Module Name : bin2gray_tb 6 // editor : L 7 // Version : Rev1.0.0 8 // ********************************************************************************* 9 10 module bin2gray_tb; 11 reg sclk ; 12 reg s_rst_n ; 13 reg en ; 14 wire [7:0] gray_out ; 15 16 bin_gray bin2gray_inst( 17 .sclk (sclk ), 18 .s_rst_n (s_rst_n ), 19 .en (en ), 20 .gray_out (gray_out ) 21 ); 22 23 initial 24 sclk = 1'b0; 25 always #10 sclk = ~sclk; 26 27 initial 28 begin 29 #1; 30 en = 1'b0; 31 s_rst_n = 1'b0; 32 #21; 33 s_rst_n = 1'b1; 34 #21; 35 en = 1'b1; 36 #500 37 en = 1'b0; 38 end 39 40 endmodule

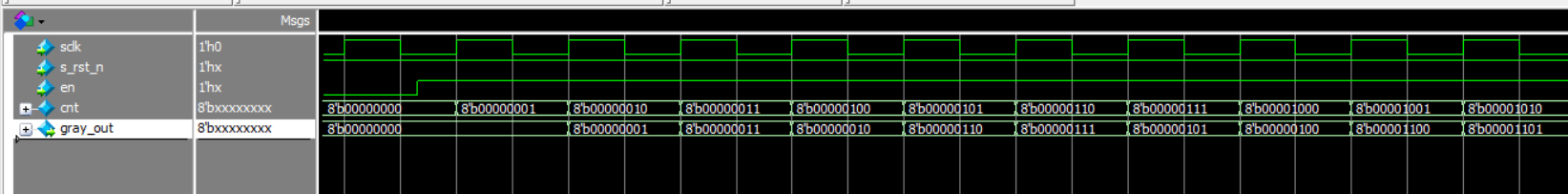

Modelsim仿真: