20145314郑凯杰《信息安全系统设计基础》第7周学习总结 part A

# 20145314郑凯杰《信息安全系统设计基础》第7周学习总结 part A

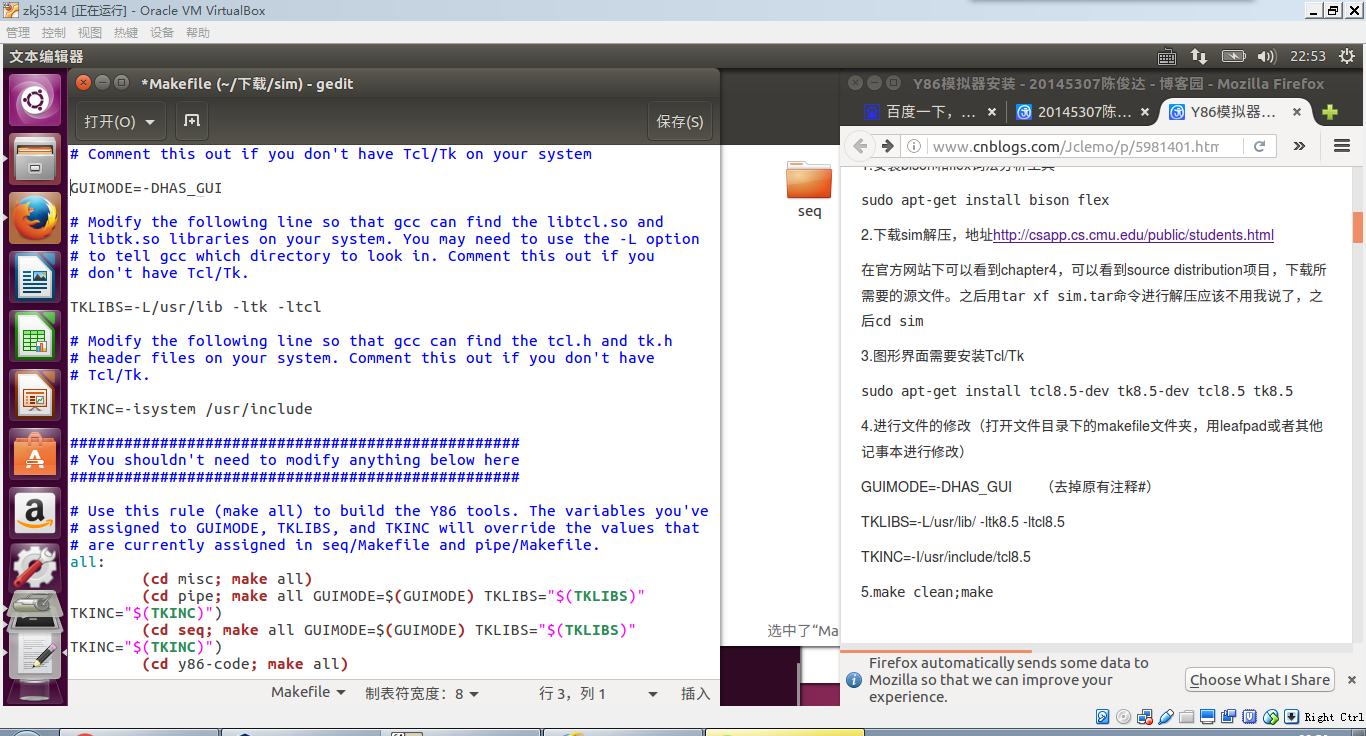

首先我放上上一周Y86模拟器安装截图:

其次 GIT的情况也向您做个汇报:

##教材学习内容总结

# 6.1 存储技术 #

存储器系统,包括存储设备以及它们的组织结构。

存储设备包括:cache,内存,硬盘,磁带....

组织结构:层次结构。

以CPU为记,越靠近CPU的存储,越快速,越小,成本越高。

----------

- 6.1.1 随机访问存储器(内存)

分两种SRAM和DRAM。即静态的和动态的。

- i)静态RAM

每个数据位存储于一个“双稳态的存储单元”。

特点是:只要有电,就永远保存它的值,比较抗干扰。

- ii)动态RAM

“每个位存储为对电容的充电”,即电容里有电就是1,没电就是0。

电容会漏电,因此必须周期性的用读出然后写回的方式刷新存储器每个位。

一个DRAM芯片中所有单元(一个单元是一位),被分成d个超单元,每个超单元由w个单元构成。

因此一个DRAM芯片能存储d*w位。 这d个超单元组织成一个r行c列的矩阵。

因此每个超单元有一个地址(i,j),i是行号,j是列号。CPU访问存储器中超单元(i,j)的方式:

先将地址i通过存储控制器发送到DRAM,DRAM取出第i行超单元内容,放入内部行缓冲区。再将地址j通过存储控制器发送到DRAM。第j个超单元,通过数据总线将数据返回。

----------

- 6.1.2 存储器模块

多个DRAM芯片包装在存储器模块中,然后插到主板的扩展槽里。有DIMM和SIMM接口。

内存条的两面都有金手指,也称为pin,如果它们传输的是相同的信号,则是SIMM接口,如果传输的是不同的信号则是DIMM。

一个64MB的内存,有8个64Mbit的DRAM芯片,每个DRAM芯片由8M*8构成。八个芯片编号为0-7. 每个超单元存储一个字节。

CPU访问主存的过程:首先通过CPU内部的总线接口,经过系统总线,到达I/O桥接器,通过存储总线到达内存。 I/O桥接器上又接上其他I/O总线。

关于总线,我总不明白它们是个什么东西? 我猜想它们就是一些导线,用来传输信号的。传地址的就是地址总线,传数据就是数据总线。

但为什么又有这么多不同的名称? 与之相关的南北桥是什么作用? 这里面有相应的标准规范吗?

----------

- 磁盘

磁盘由一些盘片构成,盘片的正反面都能存储数据,每个盘片分成许多的磁道,每个磁道分成一些扇区。

磁盘的容量 = 盘片数量 * 2 * 磁道数 * 每磁道扇区数 * 每扇区大小。

通常一个扇区为512B。

对扇区的访问时间包括:寻道时间,旋转时间和传送时间

寻道时间:即将读写磁头放在包含要访问的扇区的磁道上。T(seek),取决于磁头以前的位置和传动臂移动的速度。通常为6-9ms。

旋转时间:定位到磁道后,转动盘片,直到指定的扇区到达磁头下。取决与盘片的转速。最大旋转时间就是盘片转一圈的时间了。平均旋转时间通常为最大旋转时间的一半。

----------

- 6.2 局部性

随着CPU的发展,CPU与内存和磁盘的差距迅速拉大,为充分利用CPU性能,人们才采用了层次的存储结构。

而采用层次存储结构能提升性能的原因是:局部性,包括时间局部性和空间局部性。

(本以为局部性是程序局部性和数据局部性,仔细看书,原来是时间局部性和空间局部性)

时间局部性:被引用过的存储器位置,不久的将来很可能还会被引用。

空间局部性:一个存储器位置被引用了,那相邻的位置可能也会被很快被引用到。

----------

- 缓存的管理

i)相关假定

1. 假定存储器的地址有m位,便有M=2m 不同地址。

1. 一个缓存被分成S=2s个的高速缓存组(cache set),

1. 每个组包含 E 个高速缓存行。

1. 每个缓存行由一个B=2b字节的数据块,一个有效位,t=m-(b+s)个标记位组成。

1. 一个高速缓冲区的大小C = S * E * B。

ii)如何访问缓存

1. 当要访问存储器中的一个字节时,给出的访问地址的m位中,前t位表示标记位,中间s位为组索引,最后b位为块偏移。

1. 因此对这个访问地址,首先利用中间的s位组索引找到相应的组,

1. 对组中的每一个缓存行,将缓存行的t位标记与访问地址中的前t位进行比较,若相等,则找到字节所在的块。若没找到,缓存不命中。

1. 如果有效位为1,则利用b位块偏移,在缓存行中取出要访问的字节。

1. 若有效位为0,则缓存不命中。

iii)缓存不命中时

1. 当缓存不命中时,则若需要将存储器中的块放入缓存对应的组中。

1. 若组中的行都有数据,则需要进行替换,替换策略是:LFU或LRU

iv)三种缓存方式的划分

1. 分为直接映射高速缓存,组相联高速缓存,全相联高速缓存

1. 若指定了S,E,B的值,则缓存的划分方式就已经确定了。

1. 缓存块与存储块之间也就建立了一种映射关系。

1. 当E = 1时, 一个组中只有一个行,明显这个时候不需要使用替换策略,比较简单。查找块也很块,但容易发生冲突不命中。

1. 当E < C/B时,一个组中有多个行,这时需要考虑使用什么替换策略了。而且在查找块时,需要将地址中的标记与组中全部缓存行的标记进行比较。

1. 当E=C/B时,仅有一个组,这时不会出现冲突不命中的情况,但容易发生容量不命中。而且查找块时,需要比较全部缓存行中的标记。

## 书上示例:

int sumvec(int v[N])

{

int i, sum = 0;

for (i = 0; i < N; i++)

sum += v[i];

return sum;

}

- 由于sum会被多次引用,因此具有时间局部性。

- 由于数组v的被顺序访问,因此具有空间局部性。

- 这里是连续访问v的元素,称这种访问方式为具有步长为1的引用模式。

对于具有步长为k的引用模式,k越大,空间局部性越低,k越小,空间局部性越高。 可以将步长看成是衡量空间局部性的一个因素。

## 学习进度条

| | 代码行数(新增/累积)| 博客量(新增/累积)|学习时间(新增/累积)|重要成长|

| -------- | :----------------:|:----------------:|:---------------: |:-----:|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第一周 | 0/50 | 1/2 | 20/20 | |

| 第二周 | 176/600 | 2/4 |38/38 | |

| 第三周 | /1100 | /7 | /60 | |

| 第四周 | /1350 | /9 | /90 | |

posted on 2016-10-27 22:30 20145314郑凯杰 阅读(159) 评论(2) 编辑 收藏 举报