基于FPGA的16QAM基带通信系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不同SNR

1.算法仿真效果

本程序工程在我以前写的《m基于FPGA的16QAM调制解调通信系统verilog实现,包含testbench,不包含载波同步》基础上增加了信道模块,误码率统计模块,可以设置不同的SNR,仿真测试该FPGA系统的误码性能。

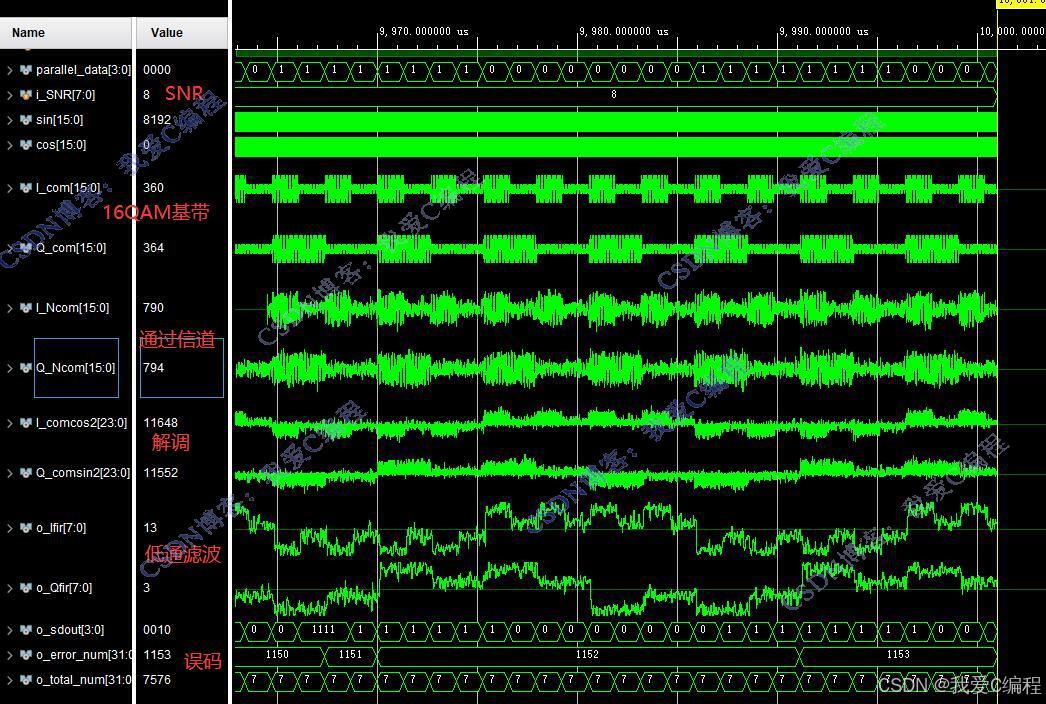

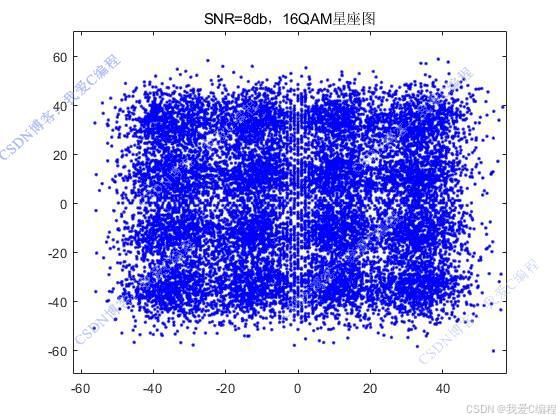

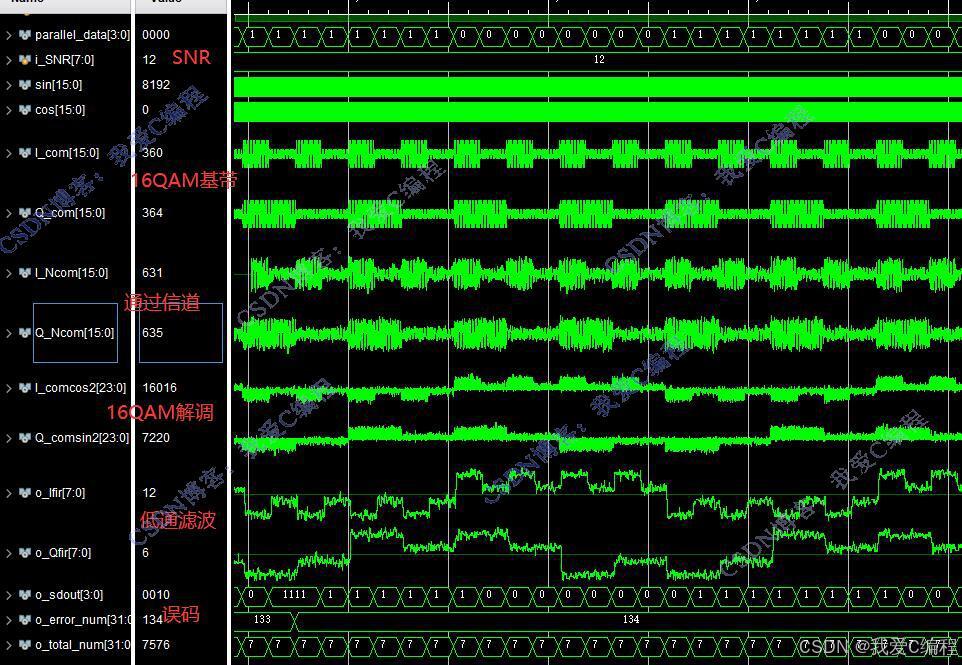

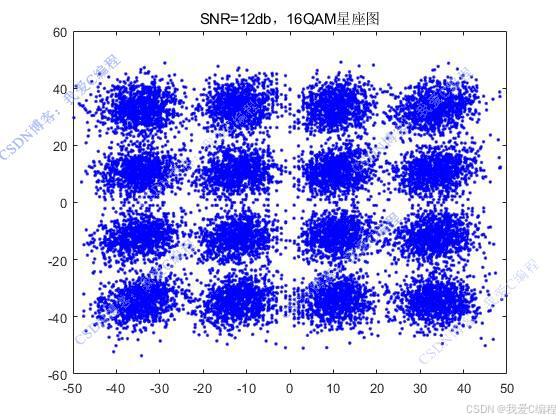

vivado仿真结果如下(完整代码运行后无水印):

设置SNR=8db

设置SNR=12db

设置SNR=16db

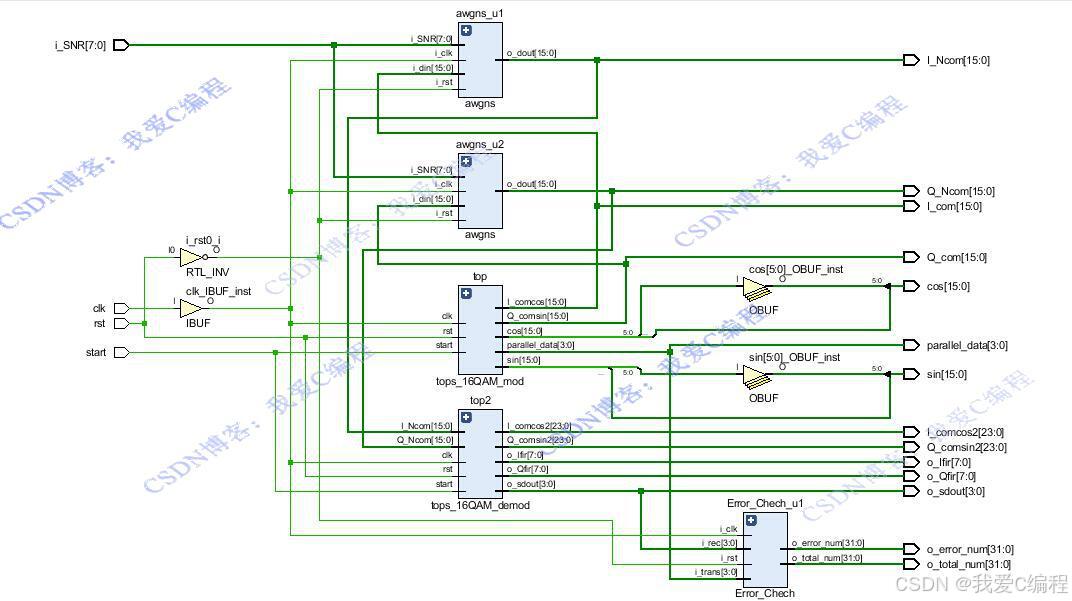

RTL结构图:

仿真操作步骤可参考程序配套的操作视频。

2.算法涉及理论知识概要

16QAM全称正交幅度调制是英文Quadrature Amplitude Modulation的缩略语简称,意思是正交幅度调制,是一种数字调制方式。产生的方法有正交调幅法和复合相移法。16QAM是指包含16种符号的QAM调制方式。

16QAM 调制原理

16QAM 是用两路独立的正交 4ASK 信号叠加而成,4ASK 是用多电平信号去键控载波而得到的信号。它是 2ASK 调制的推广,和 2ASK 相比,这种调制的优点在于信息传输速率高。

正交幅度调制是利用多进制振幅键控(MASK)和正交载波调制相结合产生的。

16 进制的正交振幅调制是一种振幅相位联合键控信号。16QAM 的产生有 2 种方法:

(1)正交调幅法,它是有 2 路正交的四电平振幅键控信号叠加而成;

(2)复合相移法:它是用 2 路独立的四相位移相键控信号叠加而成。

这里采用正交调幅法。

数字信号是通过FPGA的输出端口生成的。在16QAM调制中,每个符号包含4个比特,因此需要一个4位二进制计数器来生成数字信号。计数器的输出被映射到星座图上的一个点,然后通过数字到模拟转换器(DAC)转换为模拟信号。串/并变换器将速率为Rb的二进制码元序列分为两路,速率为Rb/2.2-4电平变换为Rb/2 的二进制码元序列变成速率为RS=Rb/log216 的 4 个电平信号,4 电平信号与正交载波相乘,完成正交调制,两路信号叠加后产生 16QAM信号.在两路速率为Rb/2 的二进制码元序列中,经 2-4 电平变换器输出为 4 电平信号,即M=16.经 4 电平正交幅度调制和叠加后,输出 16 个信号状态,即 16QAM.

16QAM 解调原理

16QAM 信号采取正交相干解调的方法解调,解调器首先对收到的 16QAM 信号进行正交相干解调,一路与 cos ω c t 相乘,一路与 sin ω c t 相乘。然后经过低通滤波器,低通滤波器 LPF 滤除乘法器产生的高频分量,获得有用信号,低通滤波器LPF 输出经抽样判决可恢复出电平信号。

3.verilog核心程序

module TOPS_16QAM(

input clk,

input rst,

input start,

input signed[7:0]i_SNR,

output [3:0] parallel_data,

output signed[15:0]sin,

output signed[15:0]cos,

output signed[15:0] I_com,

output signed[15:0] Q_com,

output signed[15:0]I_Ncom,

output signed[15:0]Q_Ncom,

output signed[23:0]I_comcos2,

output signed[23:0]Q_comsin2,

output signed[7:0]o_Ifir,

output signed[7:0]o_Qfir,

output [3:0] o_sdout,

output signed[31:0]o_error_num,

output signed[31:0]o_total_num

);

// DUT

tops_16QAM_mod top(

.clk(clk),

.rst(rst),

.start(start),

.parallel_data(parallel_data),

.sin(sin),

.cos(cos),

.I_com(),

.Q_com(),

.I_comcos(I_com),//基带方式输出,即实际通信中的复数模式

.Q_comsin(Q_com)

);

//加入信道

//实部

awgns awgns_u1(

.i_clk(clk),

.i_rst(~rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(I_com),

.o_noise(),

.o_dout(I_Ncom)

);

//虚部

awgns awgns_u2(

.i_clk(clk),

.i_rst(~rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(Q_com),

.o_noise(),

.o_dout(Q_Ncom)

);

tops_16QAM_demod top2(

.clk(clk),

.rst(rst),

.start(start),

.I_Ncom(I_Ncom),

.Q_Ncom(Q_Ncom),

.I_comcos2(I_comcos2),

.Q_comsin2(Q_comsin2),

.o_Ifir(o_Ifir),

.o_Qfir(o_Qfir),

.o_sdout(o_sdout)

);

//4个bit同时统计误码率

wire signed[31:0]o_error_num1;

wire signed[31:0]o_total_num1;

Error_Chech Error_Chech_u1(

.i_clk(clk),

.i_rst(~rst),

.i_trans(parallel_data),

.i_rec(o_sdout),

.o_error_num(o_error_num1),

.o_total_num(o_total_num1)

);

assign o_total_num = o_total_num1;

assign o_error_num = o_error_num1;

endmodule

0sj_012m

浙公网安备 33010602011771号

浙公网安备 33010602011771号