基于FPGA的16PSK调制解调系统,包含testbench,高斯信道模块,误码率统计模块,可以设置不同SNR

1.算法仿真效果

VIVADO2019.2仿真结果如下(完整代码运行后无水印):

设置SNR=30db

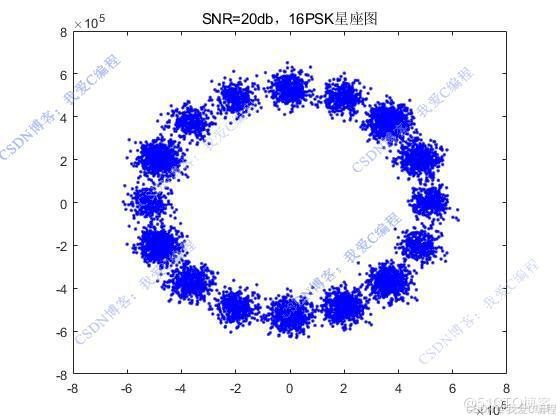

设置SNR=20db:

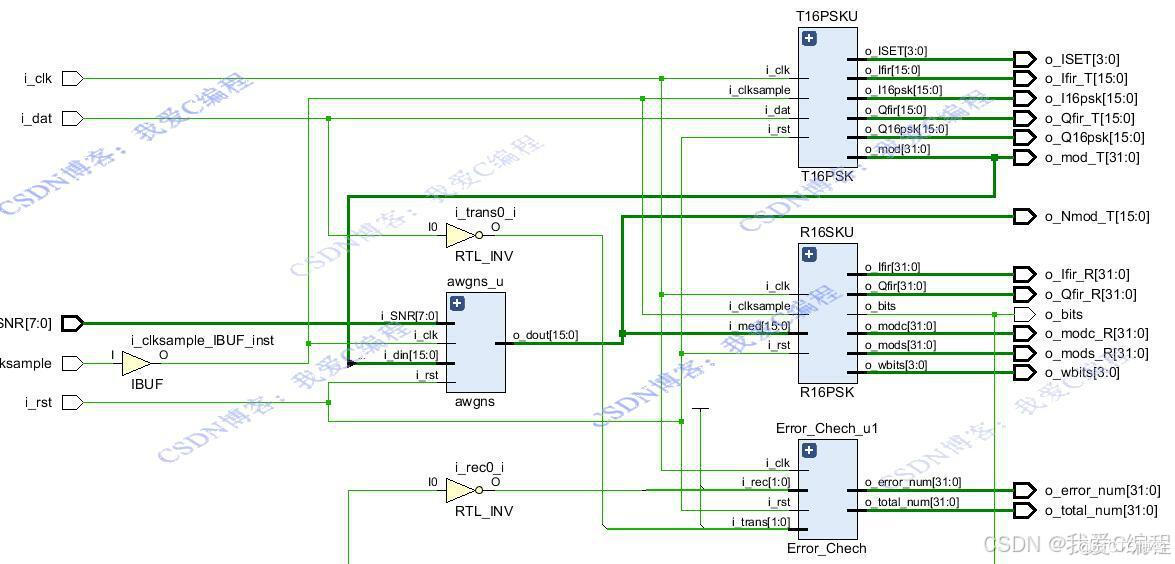

系统RTL结构图如下:

2.算法涉及理论知识概要

十六进制相位移键控(16PSK, 16-Phase Shift Keying)是一种数字调制技术,它通过改变载波相位来传输信息。16PSK能够在一个符号时间内传输4比特的信息,因此在高速数据传输中得到了广泛应用。

16PSK是一种相位调制技术,其中载波信号的相位根据要传输的信息发生改变。在16PSK中,一个符号可以表示4比特的信息,即每个符号有16种不同的相位状态。在16PSK中,每个符号可以表示16种不同的相位状态,这16个状态均匀分布在单位圆上,形成一个16点的星座图。每个符号对应于4比特的信息,即:

首先,需要将要传输的比特流转换成16个相位状态之一。假设信息比特序列为{bi},则将每4比特映射到一个相位状态上。映射规则如下:

16PSK的解调过程主要包括匹配滤波和决策两个步骤。

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/08/05 03:30:02

// Design Name:

// Module Name: TOPS_8PSK

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module TOPS_16PSK(

input i_clk,

input i_clksample,

input i_rst,

input i_dat,

input signed[7:0]i_SNR,

output [3:0]o_ISET,

output signed[15:0]o_I16psk,

output signed[15:0]o_Q16psk,

output signed[15:0]o_Ifir_T,

output signed[15:0]o_Qfir_T,

output signed[31:0]o_mod_T,

output signed[15:0]o_Nmod_T,

output signed[31:0]o_modc_R,

output signed[31:0]o_mods_R,

output signed[31:0]o_Ifir_R,

output signed[31:0]o_Qfir_R,

output [3:0]o_wbits,

output o_bits,

output signed[31:0]o_error_num,

output signed[31:0]o_total_num

);

T16PSK T16PSKU(

.i_clk (i_clk),

.i_clksample(i_clksample),

.i_rst (i_rst),

.i_dat (i_dat),

.o_ISET (o_ISET),

.o_clk_3div(),

.o_I16psk(o_I16psk),

.o_Q16psk(o_Q16psk),

.o_Ifir (o_Ifir_T),

.o_Qfir (o_Qfir_T),

.o_cos (),

.o_sin (),

.o_modc (),

.o_mods (),

.o_mod (o_mod_T)

);

//加入信道

awgns awgns_u(

.i_clk(i_clksample),

.i_rst(i_rst),

.i_SNR(i_SNR), //这个地方可以设置信噪比,数值大小从-10~50,

.i_din(o_mod_T[28:13]),

.o_noise(),

.o_dout(o_Nmod_T)

);

16PSK解调

wire [3:0]o_wbits;

wire o_bits;

R16PSK R16SKU(

.i_clk (i_clk),

.i_clksample(i_clksample),

.i_rst (i_rst),

.o_clk_3div(),

.i_med (o_Nmod_T),

.o_cos (),

.o_sin (),

.o_modc (o_modc_R),

.o_mods (o_mods_R),

.o_Ifir (o_Ifir_R),

.o_Qfir (o_Qfir_R),

.o_wbits(o_wbits),

.o_bits (o_bits)

);

Error_Chech Error_Chech_u1(

.i_clk(i_clk),

.i_rst(i_rst),

.i_trans({~i_dat,1'b1}),

.i_rec({~o_bits,1'b1}),

.o_error_num(o_error_num),

.o_total_num(o_total_num)

);

endmodule

0sj_010m

浙公网安备 33010602011771号

浙公网安备 33010602011771号