基于FPGA的BPSK数字平方环载波同步verilog实现,包含testbench

1.算法仿真效果

vivado2019.2仿真结果如下:

平方环锁定收敛曲线:

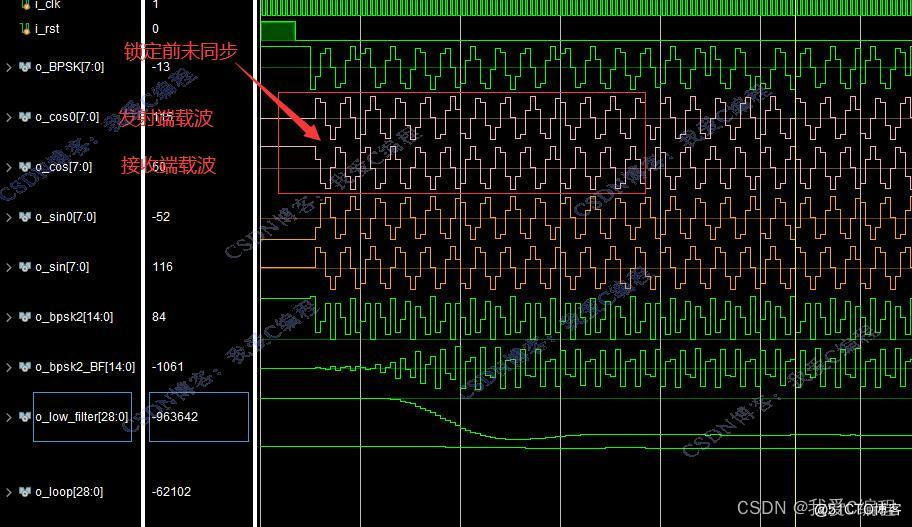

工作初始时间,发射端载波cos0和接收端载波cos不同步:

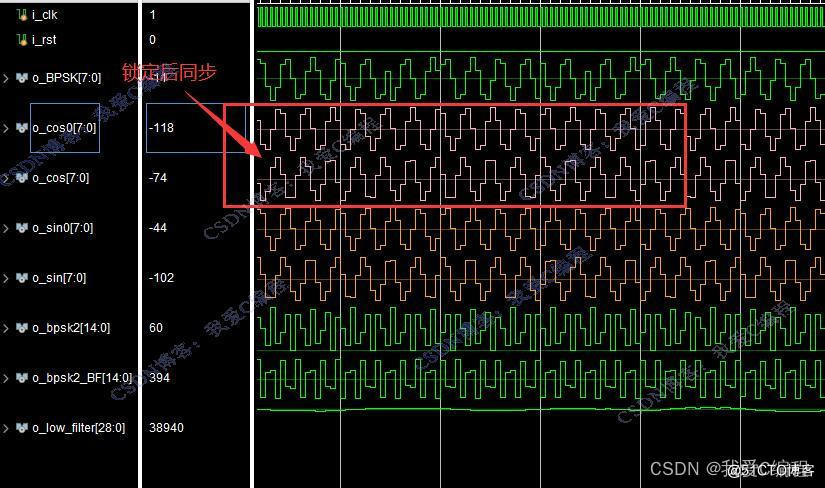

收敛之后,发射端载波cos0和接收端载波cos基本同步:

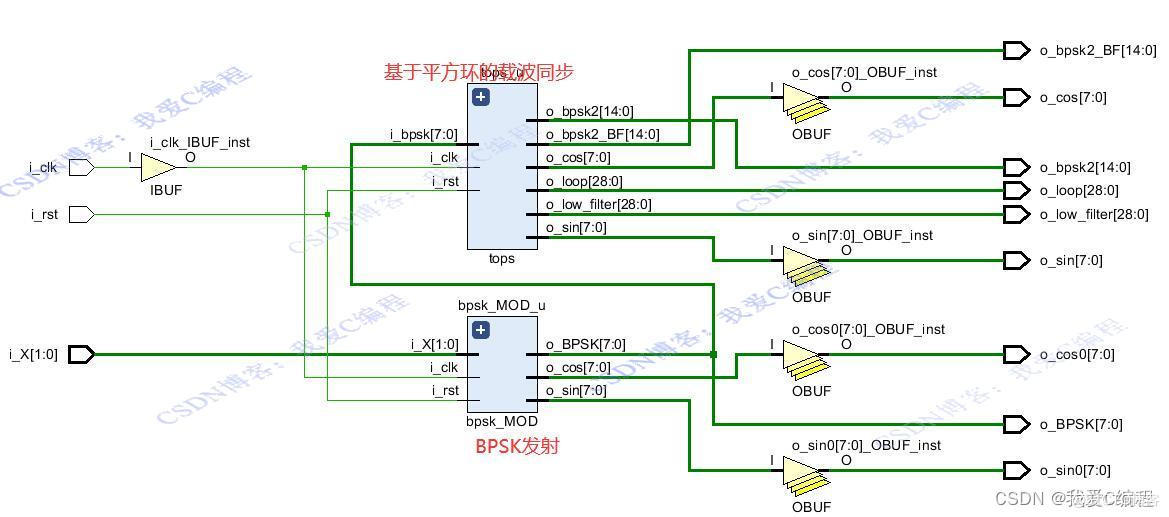

系统的RTL结构图如下:

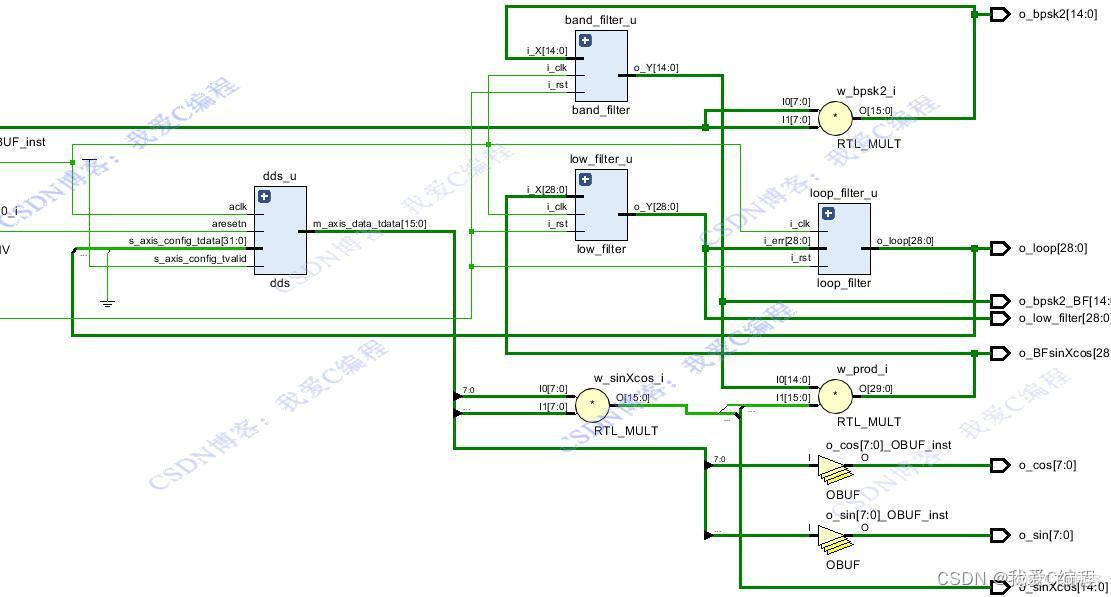

平方环内部结构如下:

2.算法涉及理论知识概要

BPSK(Binary Phase Shift Keying)数字平方环是一种用于载波恢复的非数据辅助同步方法,特别适用于二进制相移键控调制信号的解调。它利用信号的相位信息,通过平方处理和低通滤波等步骤,从接收到的信号中提取出载波的相位,从而实现相干解调。

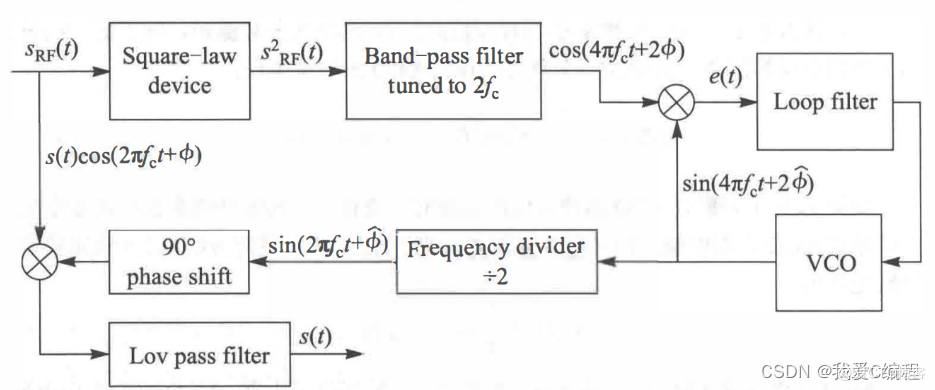

平方环是一种常用的相干解调方法。调制信号经过一个平方装置,进行平方操作,再经过一个中心频率为2fc的带通滤波器,滤除直流成分和携带的部分信息成分,得到二倍频信号cos(4πfct+2φ)。使用倍频信号驱动锁相环,得到对应的正弦信号sin(4πfct+2φ),经过二分频和90°相移,获得载波信号,从而用于相干解调获得基带信号s(t)。

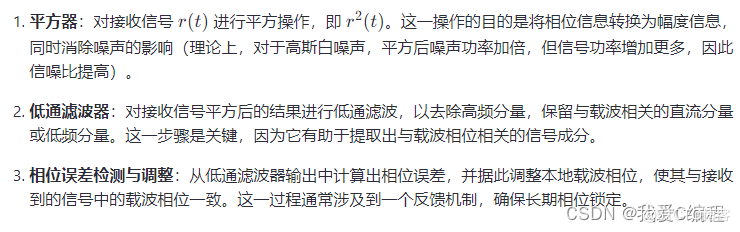

数字平方环主要包括三个主要部分:平方器、低通滤波器(LPF)、相位误差检测与调整。其工作流程如下:

3.Verilog核心程序

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2024/06/13 06:03:25

// Design Name:

// Module Name: tops_squarePLL

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tops_squarePLL(

input i_clk, //时钟

input i_rst, //复位信号

input signed[1:0]i_X, //输入数据:32MHz

output signed[7:0]o_BPSK,

output signed[7:0]o_cos0,

output signed[7:0]o_sin0,

output signed[7:0]o_cos,

output signed[7:0]o_sin,

output signed[14:0]o_bpsk2,

output signed[14:0]o_bpsk2_BF,

output signed[28:0]o_low_filter,

output signed[28:0]o_loop

);

bpsk_MOD bpsk_MOD_u(

.i_clk (i_clk), //时钟

.i_rst (i_rst), //复位信号

.i_X (i_X), //输入数据:32MHz

.o_BPSK (o_BPSK),

.o_cos (o_cos0),

.o_sin (o_sin0)

);

tops tops_u(

.i_clk (i_clk), //时钟

.i_rst (i_rst), //复位信号

.i_bpsk (o_BPSK), //输入数据:32MHz

.o_cos (o_cos),

.o_sin (o_sin),

.o_bpsk2 (o_bpsk2),

.o_bpsk2_BF (o_bpsk2_BF),

.o_sinXcos (),

.o_BFsinXcos (),

.o_low_filter (o_low_filter),

.o_loop (o_loop)

);

endmodule

00_066m

浙公网安备 33010602011771号

浙公网安备 33010602011771号