基于FPGA的FSK调制解调系统verilog开发

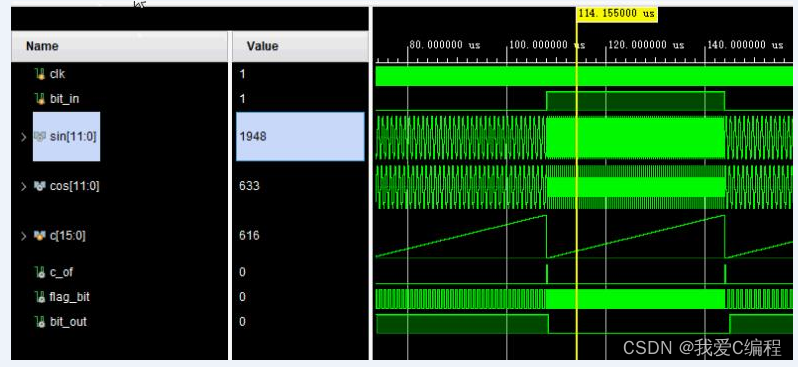

1.算法仿真效果

VIVADO2019.2仿真结果如下:

2.算法涉及理论知识概要

频移键控是利用载波的频率变化来传递数字信息。数字频率调制是数据通信中使用较 早的一种通信方式,由于这种调制解调方式容易实现,抗噪声和抗衰减性能较强,因此在 中低速数字通信系统中得到了较为广泛的应用。

在二进制频移键控中,幅度恒定不变的载波信号的频率随着输入码流的变化而切换(称为高音和低音,代表二进制的1 和0)。产生FSK 信号最简单的方法是根据输入的数据比特是0还是1,在两个独立的振荡器中切换。采用这种方法产生的波形在切换的时刻相位是不连续的,因此这种FSK 信号称为不连续FSK 信号。由于相位的不连续会造频谱扩展,这种FSK 的调制方式在传统的通信设备中采用较多。随着数字处理技术的不断发展,越来越多地采用连继相位FSK调制技术。目前较常用产生FSK 信号的方法是,首先产生FSK 基带信号,利用基带信号对单一载波振荡器进行频率调制。相位连续的FSK信号的功率谱密度函数最终按照频率偏移的负四次幂衰落。如果相位不连续,功率谱密度函数按照频率偏移的负二次幂衰落。

2-FSK功率谱密度的特点如下:

(1) 2FSK信号的功率谱由连续谱和离散谱两部分构成,离散谱出现在f1和f2位置;

(2) 功率谱密度中的连续谱部分一般出现双峰。若两个载频之差|f1 -f2|≤fs,则出现单峰。

PSK:在相移键控中,载波相位受数字基带信号的控制,如在二进制基带信号中为0时,载波相位为0或π,为1时载波相位为π或0。载波相位和基带信号有一一对应的关系,从而达到调制的目的。

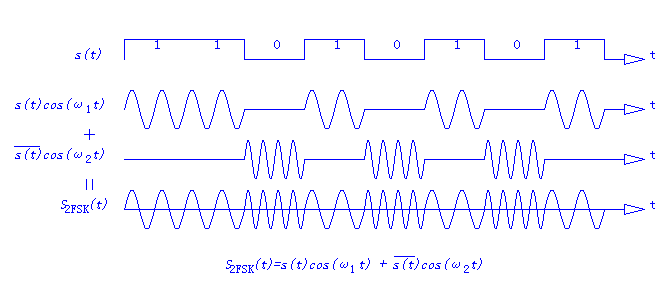

在二进制频移键控(2FSK)中,当传送“1”码时对应于载波频率,传送“0”码时对应于载波频率。 2FSK信号波形可看作两个2ASK信号波形的合成,下图是相位连续的2FSK信号波形。

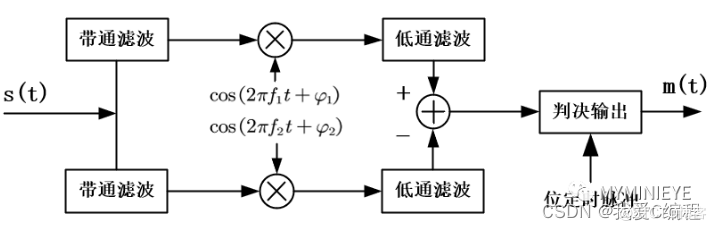

FSK信号的解调也有非相干和相干两种,FSK信号可以看作是用两个频率源交替传输得到的,所以FSK的接收机由两个并联的ASK接收机组成。

(1)相干解调

相干解调是利用乘法器,输入一路与载频相干的参考信号与载频相乘,通过低通滤波,滤除高频信号,即得原始信号,FSK经过带通滤波之后,可以看作是两路ASK信号,相干检测器组成的原理如下所示:

FSK相干解调结构

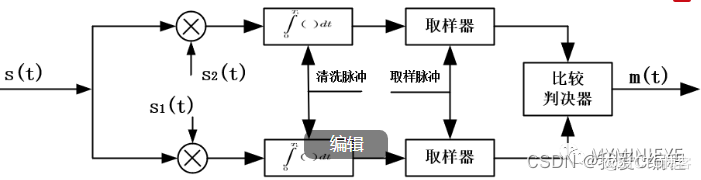

上图是一种易于实现的FSK相干解调器,还有一种最佳FSK相干解调器如下所示:

FSK最佳解调结构

从图上可以看出,在接收端要产生两个已知信号s1(t)和s2(t)的波形,分别和输入波形相乘,再送往积分器,在一定时间内积分,在t=Tb时刻,将积分结果取样,并在比较器中比较判决,然后输出,整个相干解调器的性能受载波锁相环路以及位同步性能影响很大,并且在高速率的情况下,积分、取样和清洗电路难以实现,因此通常采用第一种相干解调器的结构。

(2)非相干解调

由于FSK信号中提取相干载波相对比较困难,实际工程应用中多用非相干解调法,在相同误码率的条件下,非相干解调需要的信噪比只比相干解调高1~2dB。非相干解调的种类有很多,例如:基于自适应滤波的解调法、差分检波算法、AFC环解调法、过零检测法、包络检波法等。

3.verilog核心程序

module FSK_modulator( input bb_clk, input bit_in , input [15:0] cnt0,cnt1, input [7:0] step0,step1, output reg [11:0] sin ,cos ); wire [11:0] sin_w,cos_w; always @(posedge bb_clk)sin<=sin_w; always @(posedge bb_clk)cos<=cos_w; wire [15:0] cnt0_w,cnt1_w ; wire [7:0 ] step0_w,step1_w ; ......................................................................... reg [15:0] cnt = 0; reg [7:0] step = 0 ; always@(posedge bb_clk) cnt <= ( bit_in ) ? cnt1_w : cnt0_w ; always@(posedge bb_clk) step <= ( bit_in ) ? step1_w : step0_w ; my_dds my_dds(.clk( bb_clk ) ,.rst( 1'b0 ) ,.clr ( 1'b0 ) ,.cnt( cnt) ,.step( step) ,.sin(sin_w ) ,.cos(cos_w ) ); endmodule ......................................................................... module FSK_DEmodulator #(parameter SHORT_VALUE = 0 )( input bb_clk, output reg bit_out , input [15:0] v_short , v_long , input flag_bit ); wire flag_bit_cross; wire [15:0] v_short_w , v_long_w ; ......................................................................... reg [15:0] c;always @ (posedge bb_clk)c <= (flag_bit_cross)?0:(c+1); always @ (posedge bb_clk)if (flag_bit_cross) begin if(c<v_short_w) bit_out <= SHORT_VALUE;else if (c>v_long_w)bit_out <= ~ SHORT_VALUE ;end endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号