m基于FPGA的MSK调制解调系统verilog开发,并带FPGA误码检测模块和matlab仿真程序

1.算法描述

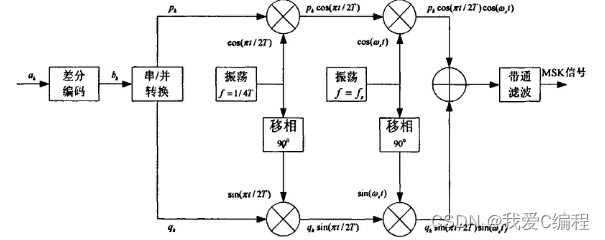

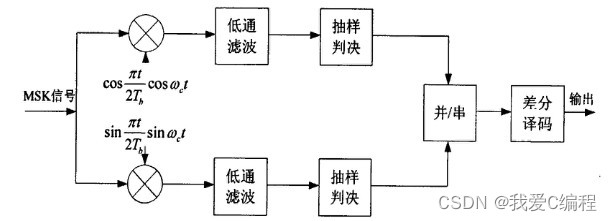

整个模型的基本框图为

软件无线电是现代通信技术的重要研究领域和发展方向,目前发展迅速.快速发展的软件无线电技术与落后的硬件计算资源之间的矛盾越来越突出.为了缓解这个矛盾,一方面可以加快集成电路的研发进度,提升硬件的计算性能;另一方面可以对信号处理的算法进行深入的改进研究,降低算法的运算量,在现有的硬件水平下提出符合实际的解决方案.在信号处理的各种算法中,调制解调算法的地位十分重要.尤其是其中的解调算法,其复杂度已被作为衡量整个信号处理系统工作性能的有效指标. 本文的研究对象是恒定包络连续相位调制技术中的最小频移键控(MSK).这种调制方式具有恒定包络,相位连续,功率谱密度较集中,频带利用率高等特点.MSK信号的诸多优点使得它在信号理论研究和应用中具有重要意义.

MSK信号是一种相位连续、包络恒定并且占用带宽最小的二进制正交FSK信号。它的第k个码元可以表示为:

MSK信号具有特点如下:①MSK信号是正交信号;②其波形在码元间是连续的;③其包络是恒定不变的;④其附加相位在一个码元持续时间内线性地变化2/p±;⑤调制产生的频率偏移等于T4/1±Hz;⑥在一个码元持续时间内含有的载波周期数等于1/4的整数倍。这里,我们考虑到硬件平台的高度可移植性,我们采用了无核化设计,就是全部使用verilog进行设计,下面首先说明一下系统的各个管脚。

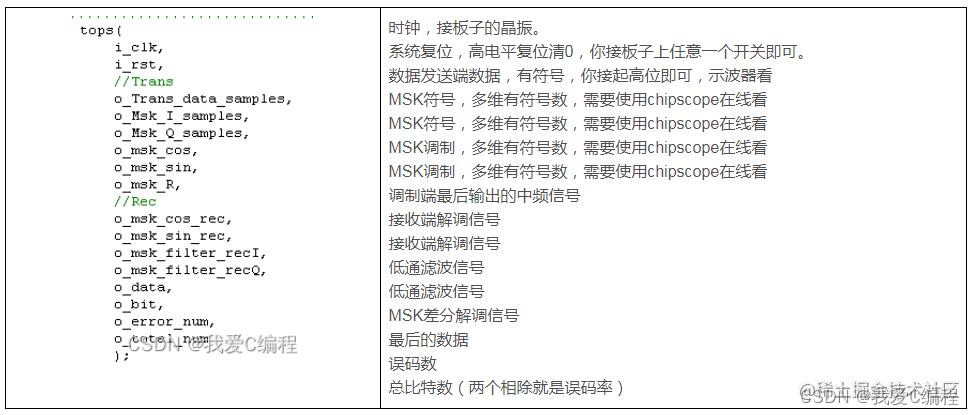

时钟,接板子的晶振。

系统复位,高电平复位清0,你接板子上任意一个开关即可。

数据发送端数据,有符号,你接起高位即可,示波器看

MSK符号,多维有符号数,需要使用chipscope在线看

MSK符号,多维有符号数,需要使用chipscope在线看

MSK调制,多维有符号数,需要使用chipscope在线看

MSK调制,多维有符号数,需要使用chipscope在线看

调制端最后输出的中频信号

接收端解调信号

接收端解调信号

低通滤波信号

低通滤波信号

MSK差分解调信号

最后的数据

误码数

总比特数(两个相除就是误码率)

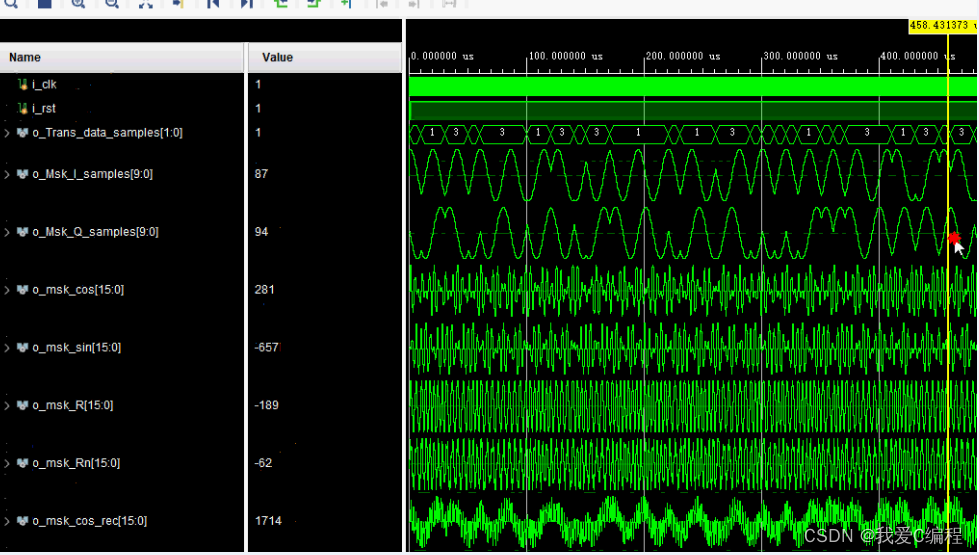

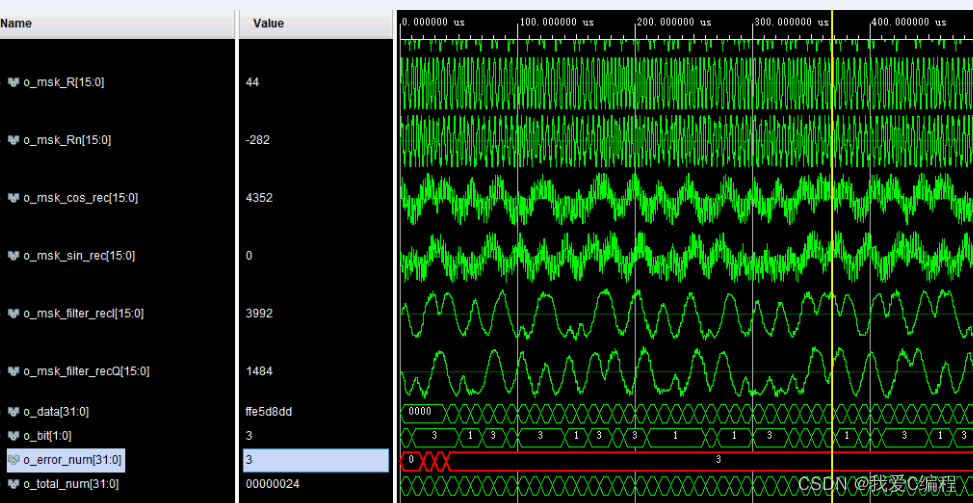

2.仿真效果预览

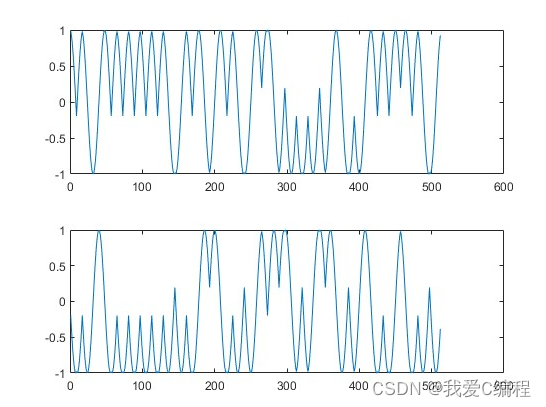

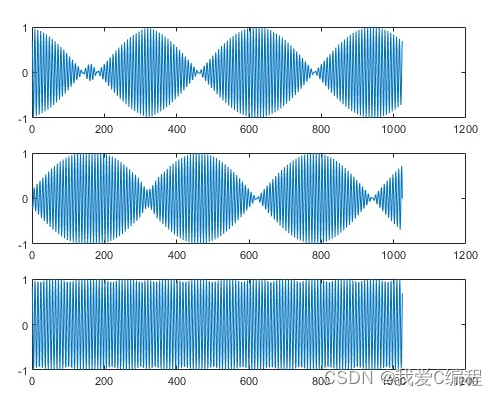

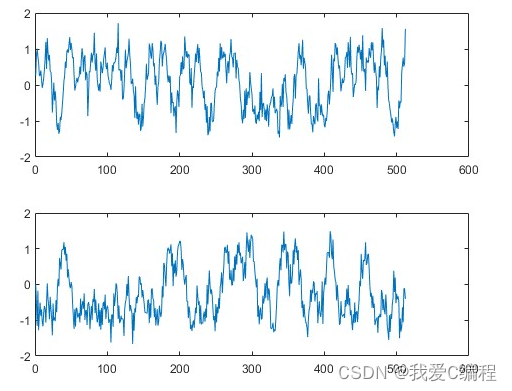

matlab2022a仿真结果如下:

3.Verilog核心程序

`timescale 1ns / 1ps

module tops(

i_clk,

i_rst,

//Trans

o_Trans_data_samples,

o_Msk_I_samples,

o_Msk_Q_samples,

o_msk_cos,

o_msk_sin,

o_msk_R,

o_msk_Rn,

//Rec

o_msk_cos_rec,

o_msk_sin_rec,

o_msk_filter_recI,

o_msk_filter_recQ,

o_data,

o_bit,

o_error_num,

o_total_num

);

input i_clk;

input i_rst;

//Trans

output signed[1:0] o_Trans_data_samples;

output signed[9:0] o_Msk_I_samples;

output signed[9:0] o_Msk_Q_samples;

output signed[15:0]o_msk_cos;

output signed[15:0]o_msk_sin;

output signed[15:0]o_msk_R;

output signed[15:0]o_msk_Rn;

//Rec

output signed[15:0]o_msk_cos_rec;

output signed[15:0]o_msk_sin_rec;

output signed[15:0]o_msk_filter_recI;

output signed[15:0]o_msk_filter_recQ;

output signed[31:0]o_data;

output signed[1:0] o_bit;

output signed[31:0]o_error_num;

output signed[31:0]o_total_num;

//Trans

//output o_clk_4M; //100M ~ 4M , 25 times

//output o_clk_1600K; //100M ~ 0.8M, 125 times

//output o_clk_200K; //100M ~ 0.1M, 1000 times

wire clk200;

wire clk_4M;

Msk_mod Msk_mod_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.o_clk_4M (clk_4M),

.o_clk_1600K (),

.o_clk_200K (clk200),

.o_Trans_data (),

.o_Trans_data_samples(o_Trans_data_samples),

.o_Msk_I (),

.o_Msk_Q (),

.o_Msk_I_samples (o_Msk_I_samples),

.o_Msk_Q_samples (o_Msk_Q_samples),

.o_cos (),

.o_sin (),

.o_msk_cos (o_msk_cos),

.o_msk_sin (o_msk_sin),

.o_msk_R (o_msk_R)

);

awgns awgns_u(

.i_clk(clk_4M),

.i_rst(~i_rst),

.i_power(16'd100),

.i_din(o_msk_R),

.o_dout(o_msk_Rn)

);

//Rec

Msk_demod Msk_demod_u(

.i_clk (i_clk),

.i_rst (~i_rst),

.i_msk_R (o_msk_Rn),

.o_msk_cos_rec (o_msk_cos_rec),

.o_msk_sin_rec (o_msk_sin_rec),

.o_msk_filter_recI(o_msk_filter_recI),

.o_msk_filter_recQ(o_msk_filter_recQ),

.o_data (o_data),

.o_bit (o_bit)

);

//error calculate

Error_Chech Error_Chech_u(

.i_clk(clk200),

.i_rst(~i_rst),

.i_trans(o_Trans_data_samples),

.i_rec(o_bit),

.o_error_num(o_error_num),

.o_total_num(o_total_num)

);

endmodule

01_117m

浙公网安备 33010602011771号

浙公网安备 33010602011771号