DSP5509开发之FPGA接口

1. DSP5509和FPGA或者CPLD之间是什么接口,DSP相对普通MCU,具有专门的硬件乘法器,程序和数据分开的哈弗结构,特殊的DSP指令,快速的实现各种数字信号处理算法。在一个周期内可以完成一次乘法和加法,而普通的MCU则可能需要多个周期。

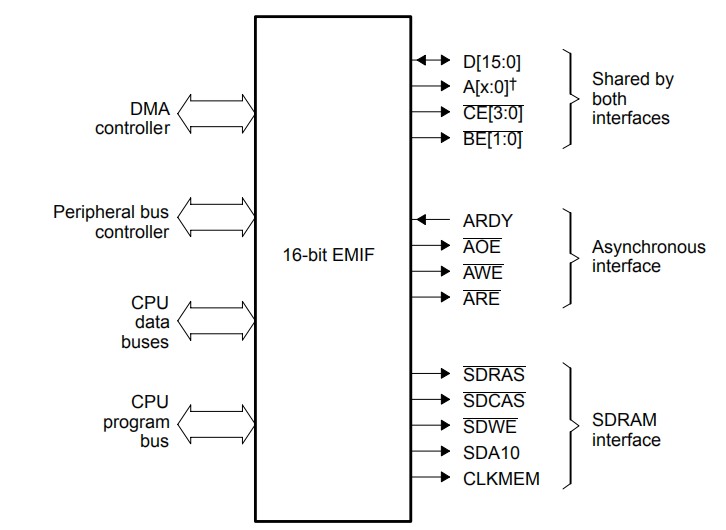

2. DSP和FPGA之间的硬件接口有两种,分别是EMIF和HPI,EMIF本来是DSP用来控制外部存储器的接口,比如RAM,SDRAM等。HPI是外部主机用来访问DSP所有地址空间的接口,从而实现对DSP的控制。

3. FIFO是一种先进先出的存储器,如果采用FIFO,那么从CPU或外设可以先将数据送往FIFO,一旦FIFO满,FIFO再向CPU申请中断,这样可以省去CPU花在等待和查询上的时间,而且中断次数也可以减少,从而提高了传输速度。问题是如果FIFO没满,那么一直收不到数据吗?所以此时有超时接受的解决办法。

4. 在FPGA上面实现一个FIFO,DSP通过EMIF接口,内部EDMA控制器去和FPGA进行交互。

5. 看下相关的代码