VC707开发板 switch例程测试 FPGA(virtex7)

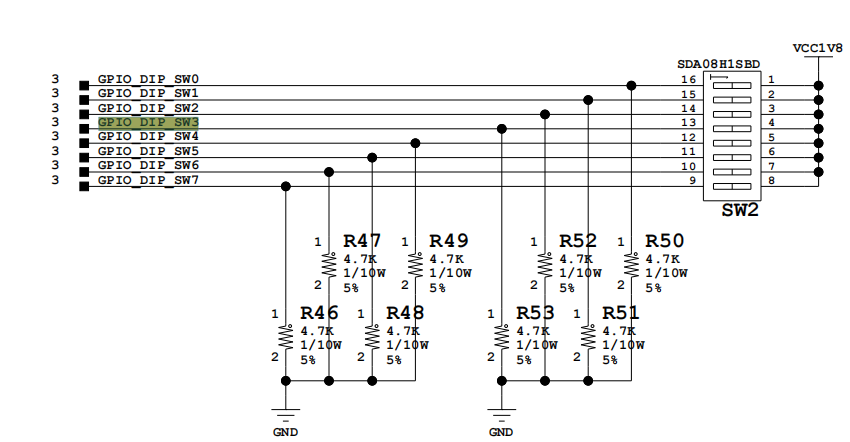

1. VC707 测试出问题,switch 例程测试失败,就是检测下面红框的拨码开关的值

2. 实测只有 SW5 和 SW1 测试正常,其他几个脚测试异常。

3. 测试这几个脚的电压,在都有OFF 情况下,只有 SW5 和 SW1 是 0.0V,其他脚都是 0.9V。

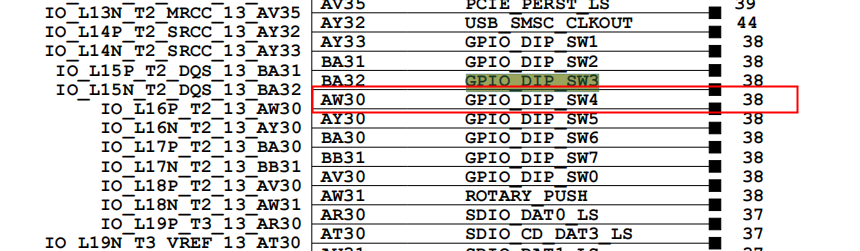

4. 断电测试,发现,SW4 对地的电阻 只有 385欧姆,VCC1.8V 到地的电阻只有 45欧姆,目前怀疑是 SW4的引脚坏了,那么把SW4不使用,其他的引脚是否就可以正常工作了?还是说整个BANK13都不行了,有遇到的指导下,可以对比下BANK15 的电阻看对不对?

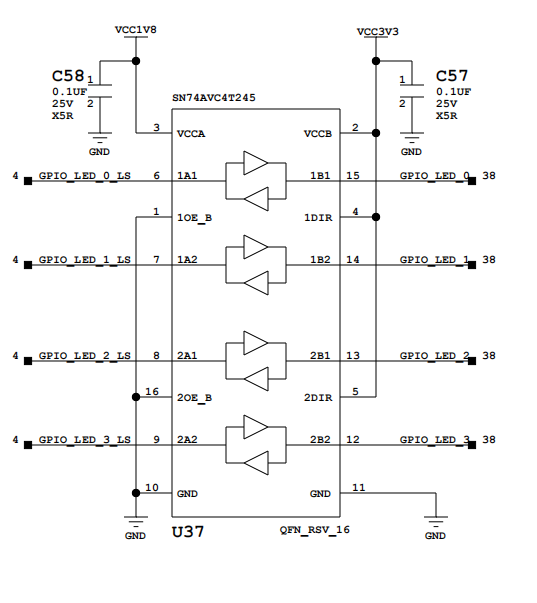

5. 写了程序测试,确实是 GPIO_DIP_SW0-7 的电平控制不了。难道是因为直接接的外部,中间没有加隔离导致烧坏了吗?像LED灯的话加的有隔离,所以没啥问题。

分类:

FPGA

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?

· 如何调用 DeepSeek 的自然语言处理 API 接口并集成到在线客服系统

· 【译】Visual Studio 中新的强大生产力特性

· 2025年我用 Compose 写了一个 Todo App

2018-11-12 NB05-01一直复位的问题解决

2018-11-12 解决韩国KT下发170次数据死机的问题