design compiler 废了九牛二虎之力装上了虚拟机。

1.可以在任何路径下打开 gui 界面。输入dv&不行(安装时候初始化是这样的) ,直接用命令design_vision 就会出现gui界面。

2,

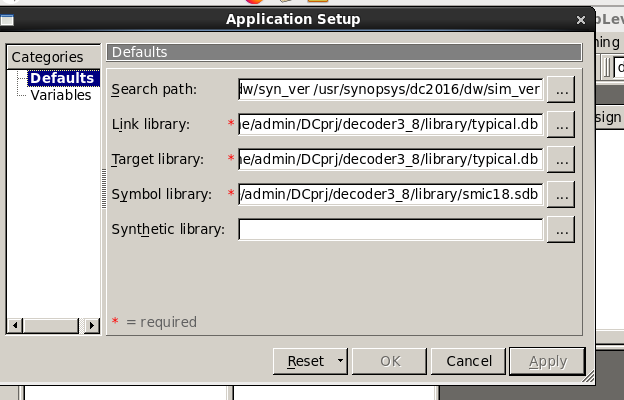

setup,可以tcl进行配置,奈何命令学的不精,只能手动进选择。刚开始配置时 总会出现Could not read the following target libraries:。重新建了一个prj>decoder>libraray .把晶圆厂给的工艺 IO_std 下的 smic18.sdb(符号库文件)和typical.db(目标工艺库文件)文件复制到libraray下面。然后加载到setup下面。可以完成library的读取。

该系列实验用的是13的guide和lab,均可以在eetop上找到!

Lab1:

实验流程:

1、打开 common_setup.tcl 文件,修改包含逻辑库、设计、脚本的路径:set ADDITIONAL_SEARCH_PAT,

逻辑工艺库文件:set TARGET_LIBRARY_FILES,

符号库文件:set SYMBOL_LIBRARY_FILES,

用户定义的 Milkyway 设计库名称:set MW_DESIGN_LI,Milkyway所参考的库目录:set MW_REFERENCE_LIB_DIRS;

2、键入命令 dc_shell 打开 dc 命令行模式,键入命令 printvar search_path、printvar target_library、printvar link_library 查看库搜索路径、目标库和链接库:

在这里插入图片描述

输入 alisa 查看命令的对应自定义缩写,check_library 除了检查逻辑库和物理库的完整性,还可以查看最小时间、电容、功耗、电流单位:

在这里插入图片描述

3、读入设计 v 文件并与逻辑库相连接

read_file -format verilog ./rtl/TOP.v、 current_design TOP、link

查看设计文件名和与之连接的逻辑库等库的名字:list_designs、list_libs

在这里插入图片描述

4、读入约束文件 source TOP.con

compile_ultra 完成编译

在这里插入图片描述

AREA 表示设计电路的总面积,WORST NEG SLACK 表示最坏的路径裕度(负值)。

5、report_constraint -all 报告违规的路径及其负裕度,和总的裕度值。

在这里插入图片描述

report_timing 指出各路径的延时和数据要求、到达时间,判断违规情况

在这里插入图片描述

report_area:指出设计的各部分形式单元的面积:组合逻辑部分,反相器缓冲器部分、非组合逻辑部分,最后的总面积为单元的面积和连线的面积之和。

在这里插入图片描述

其实没有Lab2嘻嘻嘻

浙公网安备 33010602011771号

浙公网安备 33010602011771号