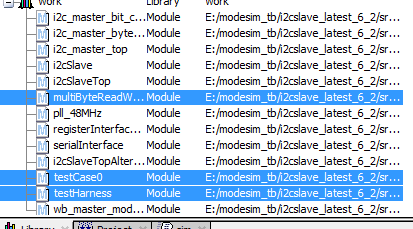

Q: modelsim 仿真, testbench.v 调用另一个模块的一个task会出现4): Unresolved reference to 'testHarness

D ,把那些未reference 的文件加载一起仿真。

,把那些未reference 的文件加载一起仿真。

Verilog里的`符号表bai示宏定义(macro definition)或者du编译指令(zhicompiler directives),对整个工程(project)有效。我见过的有`daoinclude;`timescale;`define,`undef,`ifdef,`ifndef,`elsif,`else,`endif。

另外,关于begin/end的问题,如果语句块里面有多于1条执行语句就必须要用begin/end顺序语句块或者fork/join并行语句块.

用<module>.<task>的方式,module就是包含task的模bai块名du,task就是任务名(且task有input b,c,d; 形参)对应sum(a,b,c)实参;

例如你的zhi模块名是comp,里面有个任务叫sum(a,b,c);

在当dao前的模块下先例化comp my_comp();

使用任务就用my_comp.sum(a,b,c);

科技与美好相连

浙公网安备 33010602011771号

浙公网安备 33010602011771号