过载 :相对于电源来说的。当流过电源的电流过大时,会发生过载。

噪声容限(英语:Noise Margin)是指在前一极输出为最坏的情况下,为保证后一极正常工作,所允许的最大噪声幅度 。在数字电路中,一般常以“1”态下(上)限噪声容限和“0”态上(下)限噪声容限中的最小值来表示电路(或元件)的噪声容限。噪声容限越大说明容许的噪声越大,电路的抗干扰性越好。

高电平噪声容限 = 最小输出高电平电压-最小输入高电平电压

低电平噪声容限 = 最大输入低电平电压-最大输出低电平电压.

最小项,包含所有输入变量的乘积项。

最大项 包含所有输入项的和。

有N个输入的真值表,包含 2^N行。

噪声容限 = min{ 高电平噪声容限,低电平噪声容限 }

静态约束:为了避免输入落到禁止区域,数字逻辑门的设计需要遵循静态时序。 对于给定有效逻辑输入,每个电路能产生有效的逻辑输出。

CMOS 逻辑门 具有正常的功能的逻辑门中,上拉网络和下拉网络必然有一个导通一个截止,这样不会产生悬浮和短路。传导互补规则可以保证

nMos 采用串联,pMOS 才有并联。反正相反。 多个串联的晶体管速度也是比较慢。由于PMOS晶体管的空穴在硅晶格中的移动速度低与电子速度

所以PMOS 晶体管的速度要慢与nMOS管的速度。

NMOS可以很好的导通0 pMOS 可以很好的道通1

功耗是单位时间内所消耗的能量。

数字系统的功耗包括动态功耗和静态功耗。dynamic power 是信号在0 到1变化过程中电容充电所消耗的功耗的能量。static power 是系统处于空闲状态下的功耗。

逻辑门和他们的连线都有电容。将电容C充电到电压VDD所需的能量为 CVDD^2. 如果电容电压的切换频率为F(每秒变化f次)

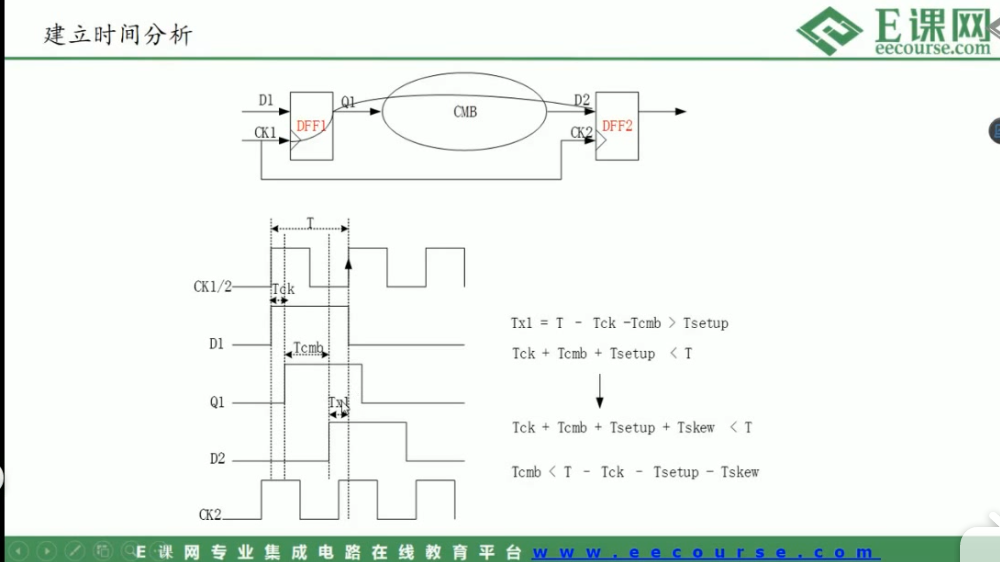

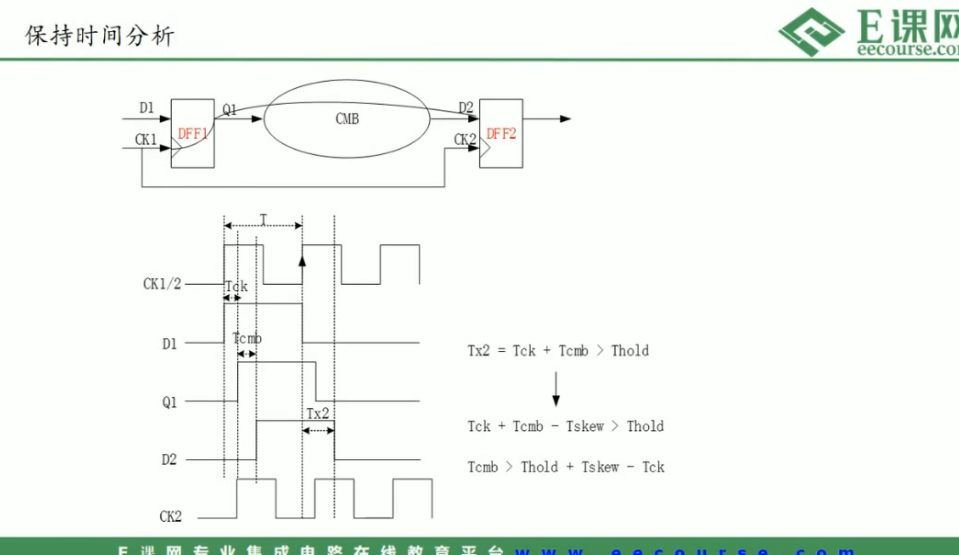

setuptime 和 hold time的理解

set

hold

浙公网安备 33010602011771号

浙公网安备 33010602011771号