毕业设计预习:VHDL入门知识学习(一) VHDL程序基本结构

VHDL入门知识学习(一) VHDL程序基本结构

- 简介

- VHDL程序基本结构

简介

概念:

- HDL—Hardware Description Language—硬件描述语言—描述硬件电路的功能、信号连接关系及定时关

系的语言。

- VHDL—Very High Speed Integrated Circuit Hardware Description Language—超高速集成电路硬件

描述语言

特点:

- 工艺无关

- 共享复用

- 不支持描述模拟电路

规定:

- 在VHDL中,字母的大、小写没有区别(单引号内的字符常数和双引号内的字符串除外);

- 以分号“;”作为语句结束的标志;

- 注释行以双短线“- -”开始;

- 各种名称的命名规则:

- 名称由字母、数字和下划线组成;

- 名称的第一个字符必须是字母;

- 名称的最后一个字符不能是下划线,也不能连用下划线;

- 命名不能与VHDL的保留字或关键字相同。

VHDL程序基本结构

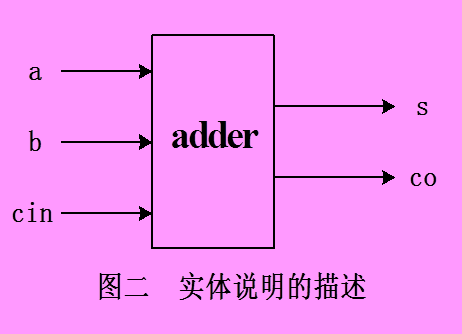

例:1位全加器

ENTITY adder IS

PORT( a, b,cin : IN BIT;

s ,co : OUT BIT);

END adder;//实体说明

ARCHITECTURE a OF adder IS

BEGIN

s<=a XOR b XOR cin;

co<=((a XOR b) AND cin) OR (a AND b);

END a;//结构体说明

实体说明:描述了一个设计对外的输入、输出接口以及一些用于结构体的参数定义。

结构体说明:描述的是设计实体的行为和结构。

实体(Entity )

ENTITY <实体名> IS

[类属参数说明]

[端口说明]

END <实体名>;

ENTITY adder IS

PORT(

a, b,cin : IN BIT;

s ,co : OUT BIT);

END adder;

实体名: 对实体的命名,在MAXPLUSII中要求实体名必须与存盘文件名相同。

类属参数说明:用来为设计实体指定参数,如定义端口宽度、器件延时等。

端口说明:描述端口的名称、模式和数据类型。

PORT(端口名[,端口名]:模式 数据类型;

┇

端口名[,端口名]:模式 数据类型);

端口名称: 对端口的命名,是端口的标识符。

端口模式: 说明端口信号的流动方向。

① 输入模式(IN)

② 输出模式(OUT)

③ 双向模式(INOUT)

④ 缓冲模式(BUFFER)

⑤ LINKAGE模式

端口: 实体的每一个输入、输出信号称为端口,对应于硬件电路图或芯片的一个'引脚'。

数据类型:说明经过端口的信号的数据类型。

- VHDL是一种强类型语言,有10种标准的数据类型,还可以由用户自定义数据类型。

- BIT(位,可取值为‘0’或‘1’ )类型是VHDL的预定义类型,使用此类型时无需特别说明。

- 当使用非预定义的数据类型时,必须用

库和程序包调用语句来为程序的编译指明所使用的数据类型的定义在哪里。

库和数据包的调用

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY adder IS

PORT( a, b,cin : IN STD_LOGIC;

s ,co : OUT STD_LOGIC);

END adder;

结构体

ARCHITECTURE <结构体名> OF <实体名> IS

[结构体说明部分];

BEGIN

<并行处理语句>;

END结构体名;

ARCHITECTURE a OF adder IS

BEGIN

s<=a XOR b XOR cin;

co<=((a XOR b) AND cin) OR (a AND b);

END a;

结构体名:对本结构体的命名。

结构体说明部分:对结构体内部所使用的'信号'、'常数'、数据类型和函数进行定义;

并行处理语句:具体描述了结构体的行为和结构。

VHDL程序五大部分

1、实体(Entity )

描述所设计的系统的外部接口信号。

2、结构体(Architecture Body)

描述系统内部的结构和行为。

3、程序包(Package)

存放各个设计模块都能共享的数据类型、信号和常数的定义以及函数和过程的定义等。

4、库(Library)

存放已经编译的实体、结构体、程序包和配置的定义。

5、配置(Configuration)

描述实体与结构体之间的连接关系,或者在分层设计中描述层与层之间的连接关系。

PS:MAXPLUSII自动选择几何位置排列在最后的结构体作为当前结构体进行编译。

参考

书籍:《VHDL入门·解惑·经典实例·经验总结》