1553B总线介绍及其硬件方案设计

1553B总线介绍及其硬件方案设计

1.简介

简单介绍可参考(https://blog.csdn.net/ScilogyHunter/article/details/108444231)博主写的很详细。

1553B总线是MIL-STD-1553总线的简称,其中B就是BUS,MIL-STD-1553B总线是飞机内部时分制命令/响应式多路复用数据总线。1553B数据总线标准是20世纪70年代由美国公布的一种串行多路数据总线标准。1553B总线能挂31个远置终端,1553B总线采用指令/响应型通信协议,它有三种终端类型:

BC:总线控制器, bus controller

RT:远程终端,remote terminal

BM/MT: 总线监视器,bus monitor terminal

信息格式有BC到RT、RT到BC、RT到RT、广播方式和系统控制方式;传输媒介为屏蔽双绞线,1553B总线耦合方式有直接耦合和变压器耦合;1553B总线为多冗余度总线型拓扑结构,具有双向传输特性,其传输速度为1Mbps传输方式为半双工方式,采用曼彻斯特码进行编码传输。采用这种编码方式是因为适用于变压器耦合,由于直接耦合不利于终端故障隔离,会因为一个终端故障而造成整个总线网络的完全瘫痪,所以其协议中明确指出不推荐使用直接耦合方式。

2.特点

一.是实时性好,1553B总线的数据传输率为1Mbps,每条消息最多包含32个字,传输一个固定不变的消息所需时间短。数据传输速率比一般的通讯网高。

二.是合理的差错控制措施和特有的方式命令,为确保数据传输的完整性,1553B采用了合理的差错控制措施――反馈重传纠错方法。当BC向某一RT发出一个命令或发送一个消息时,终端应在给定的响应时间内发回一个状态字,如果传输的消息有错,终端就拒绝发回状态字,由此报告上次消息传输无效。而特有的方式命令不仅使系统能完成数据通讯控制任务,还能检查故障情况并完成容错管理功能。

三.是总线效率高,总线形式的拓扑结构对总线效率的要求比较高,为此1553B对涉及总线效率指标的某些强制性要求如命令响应时间、消息间隔时间以及每次消息传输的最大和最小数据块的长度都有严格限制。

四.是具有命令/响应以及“广播”通讯方式,BC能够以“广播”方式向所有RT发送一个时间同步消息,这样总线上的所有消息传输都由总线控制器发出的指令来控制,相关终端对指令应给予响应并执行操作。这种方式非常适合集中控制的分布式处理系统。但1553B 总线价格高昂,限制了它在工业领域的普遍性应用。

3.消息传输机制

1553B总线上的信息是以消息(Message)的形式调制成曼彻斯特码进行传输的。每条消息最长由32个字组成,所有的字分为三类:命令字、数据字和状态字。每类字的长度为20位,有效信息位是16位,每个字的前3位为单字的同步字头,而最后1位是奇偶校验位。有效信息(16位)及奇偶校验位在总线上以曼彻斯特码的形式进行传输,传输一位的时间为1us(即码速率为1MHz)。同步字头占3位,先正后负为命令字和状态字,先负后正为数据字。

在这三种类型的字中,命令字位于每条消息的起始部分,其内容规定了该次传输的具体要求。状态字只能由RT发出,它的内容代表RT对BC发出的有效命令的反馈。BC可以根据状态字的内容来决定下一步采取什么样的操作。数据字既可以由BC传输到某RT,也可以从某RT传输至BC,或者从某RT传输到另一RT,它的内容代表传输的数据。

1553B总线上消息传输的过程是:总线控制器向某一终端发布一个接收/发送指令,终端在给定的响应时间范围内返回一个状态字并执行消息的接收/发送。BC通过验收RT回答的状态字来检验传输是否成功并做后续的操作。

消息是构成1553B总线通讯的基本单位,如果需要完成一定的功能,就要将多个消息组织起来,形成一个新的结构叫做帧(Frame)。帧的结构见图2。在图中,完成一个消息的时间称为消息时间,两个消息之间的间隔称为消息间隔时间,完成一个帧的时间称为帧时间。在实际应用中这三种时间都是可以通过编程设置的。

4.硬件接口设计方案

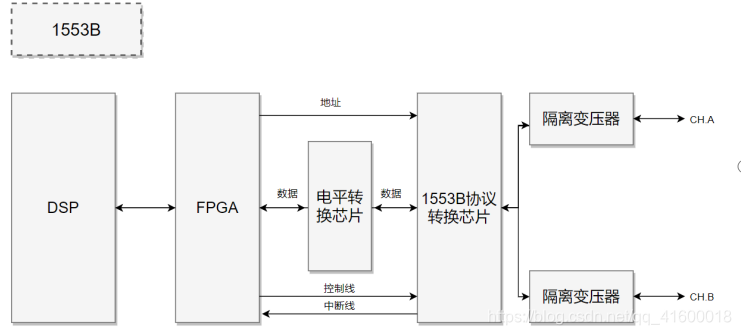

4.1 协议转换芯片+DSP

采用1553B协议转换模块芯片,该协议芯片采取并口通讯的方式传给CPU,防止占用CPU资源,采用FPGA+1553B协议芯片的方式处理1553B协议,FPGA和DSP之间采用串口通信。FPGA选型和1553B协议转换芯片的选型应该保持IO电平一致,可以节省一块电平转换芯片,从而节省硬件资源。国内主要的FPGA厂商深圳国微是国内开展微处理器、可编程器件的主要研制、开发单位,已有系列化的可编程器件产品,可通过改进设计实现国产化替代。

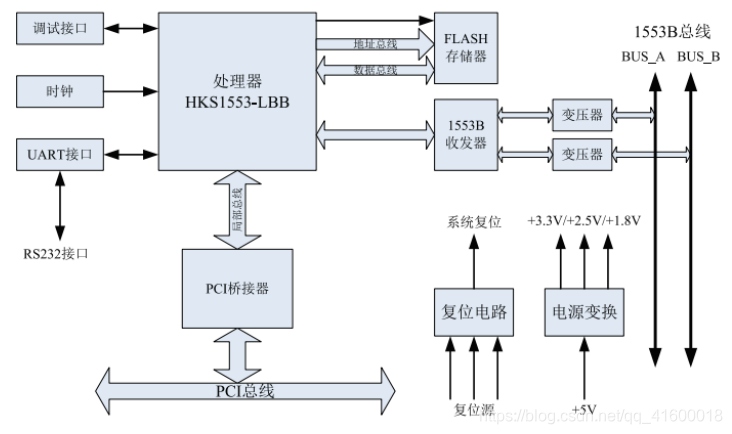

4.2 SoC方案

PCI 总线接口的 1553B 多路数据总线接口模块简称 PMCMBI 模 块, PMC-MBI 模 块片上系统 HKS1553BCRT 实现, 该系统内部含有 ARM 处理器, 并具有 RTC 实时时钟电路,1553B总线收发电路, 1553B 总线解码分析、串并转换功能,HKS1553BCRT内部有双端口存储器,作为 MBI 模 块 收 到 的1553B 数据和系统主机共享使用。

PMC-MBI 模块设计和主机的接口为 PCI 总线,系统主机通过 PCI 总线初始化和驱动 MBI 模块工作 。

浙公网安备 33010602011771号

浙公网安备 33010602011771号