信号完整性(SI)电源完整性(PI)学习笔记(十三)传输线与反射(三)

传输线与反射(三)

1.容性终端的反射

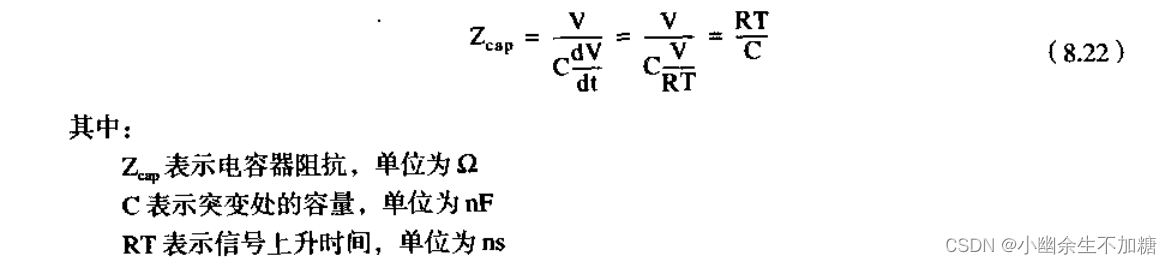

(1)当信号沿传输线到达末端的理想电容器时,决定反射系数的瞬时阻抗将随时间的变化而变化,因为时域中的电容器阻抗为:

(2)如果时间足够长,电容器充电达到饱和,电容器就相当于断路。

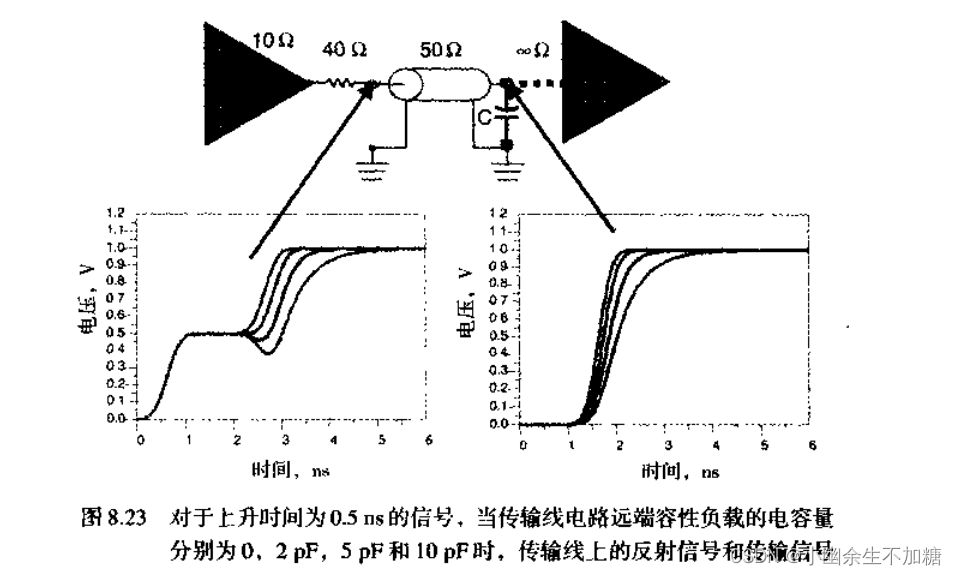

(3)这意味着反射系数随时间的变化而变化,反射信号将先下跌再上升到开路状态的情形。这个精确波形是由传输线特性阻抗Z0、电容器的电容量和信号上升边决定的。

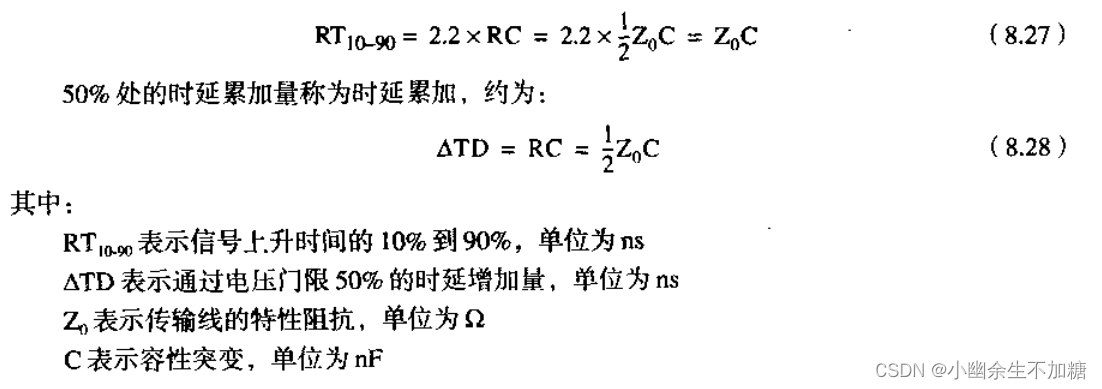

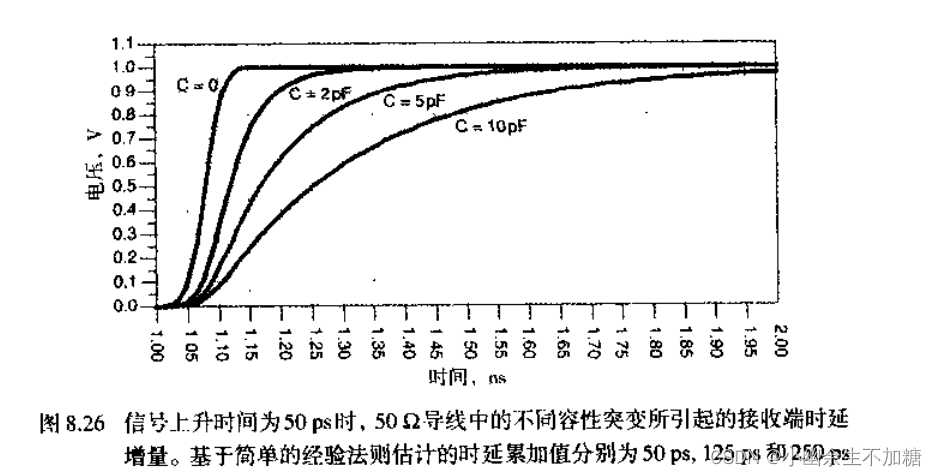

2.电容器对信号上升边进行滤波,对接收端而言,它就相当于一个“时延累加器”。新的信号的上升边上升至幅度中间值的时延增加量,即时延累加。时间常数:te=RC。

这个时间常数是电压升到电压终值1/e或37%所需要的时间,10%~90%上升边与RC。

3.测试焊盘,过孔,封装引线或连接到互连线途中的短桩线都起着集点电容器的作用。

(1)对于远端而言,第一次经过电容器的传输信号并没有受到太大影响,但当信号在末端发生反射后。它将向源端方向返回。

(2)电容量越大,电容器阻抗就越小,负反射电压就越大,从而接收端的下冲就很大。同理,上升边就短促,电容器阻抗就越小,下冲也就越大。

若信号是线性上升边:

Zcap=RT/C

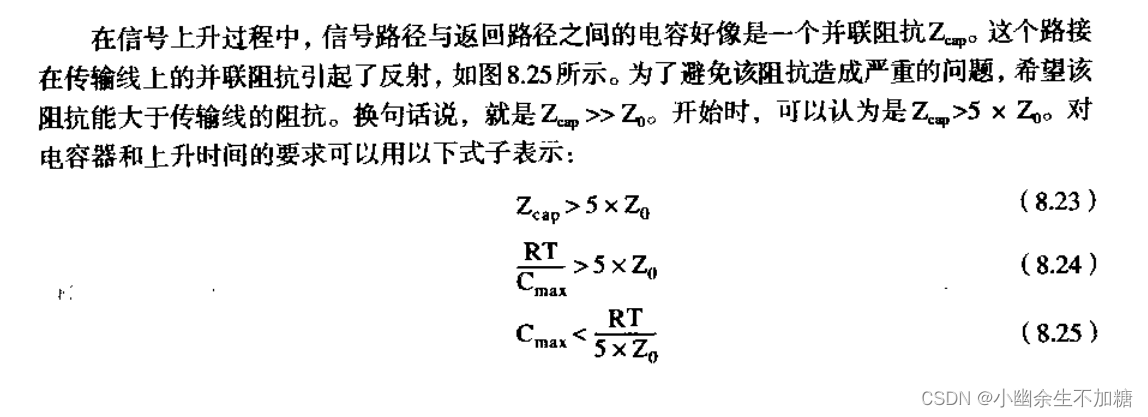

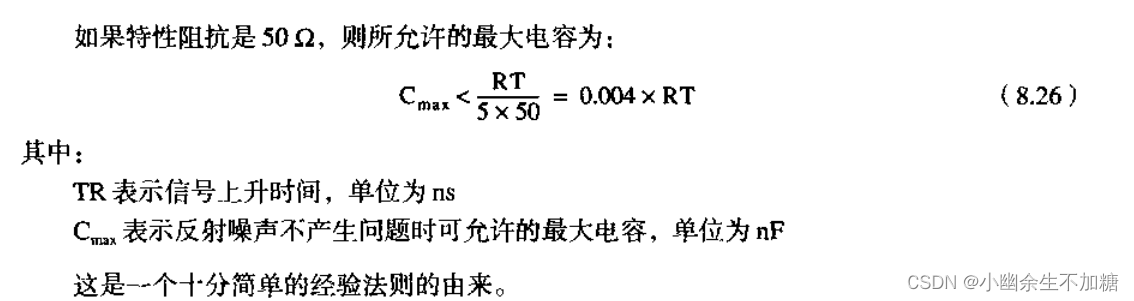

4.在信号上升过程中,信号路径与返回路径之间的电容器就是一个并连阻抗Zcap,这个跨接在传输线上的并联阻抗引起了反射,为了避免该阻抗造成严重的问题,希望该阻抗能大于传输线的阻抗。Zcap>Z0

5.中途容性负载产生的第一位的影响就是接收端的下冲噪声。第二位的更复杂影响则是远端信号的接收时延被延迟。

50%处的时延累加量称为时延累加。

公式中的1/2是因为传输线的前一半使电容器充电,而后一半使电容器放电,所有给电容器充电的有效阻抗实际上是特性阻抗的1/2.

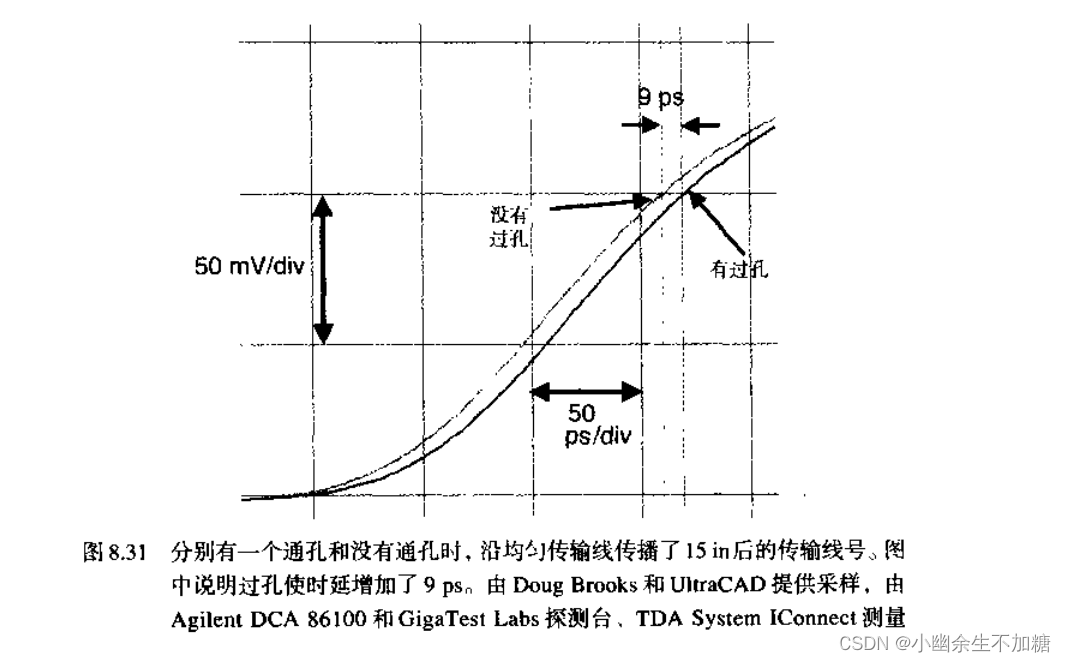

6.每个过孔焊盘或连接器都可能增加25ps时延。使用低特性阻抗是减小时延累加的一种方法。对于同样的容性突变,特性阻抗越低,时延累加就越小。

7.任何均匀互联中90°拐角一定会造成阻抗突变,影响信号质量。

8.很高的直流电场会使拐角处尖端变长,并引发长期可靠性问题,但不会影响信号质量。弯曲处的额外线宽是使拐角影响信号传输的唯一原因,如同一个容性突变。

9.50Ω传输线上一个拐角的电容量(fF)约等于两倍线宽(mil)。

10.一般过孔处的有效特性阻抗,包括经过不同平面的返回路径,小于50Ω,约为35Ω。50Ω的长度电容为3.5pF/in,过孔5pF/in。

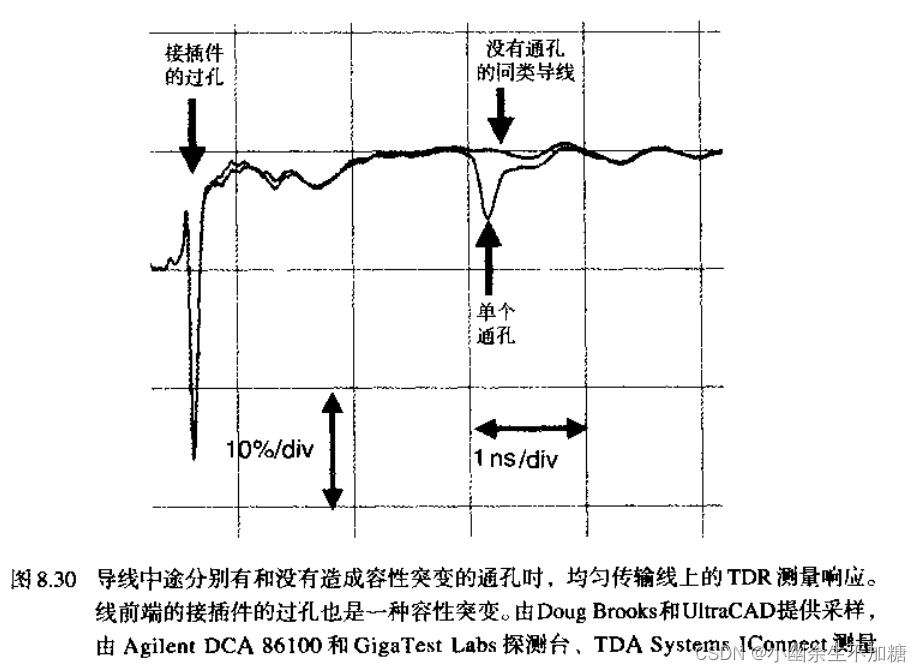

11.导线中,SMA连接器的过孔和线中间位置上的通孔的电容量均为0.4pF,致使这个过孔产生反射电压不同原因是:当信号传播到中间位置及后续返回的过程中,介质损耗使信号上升边发生了退化。

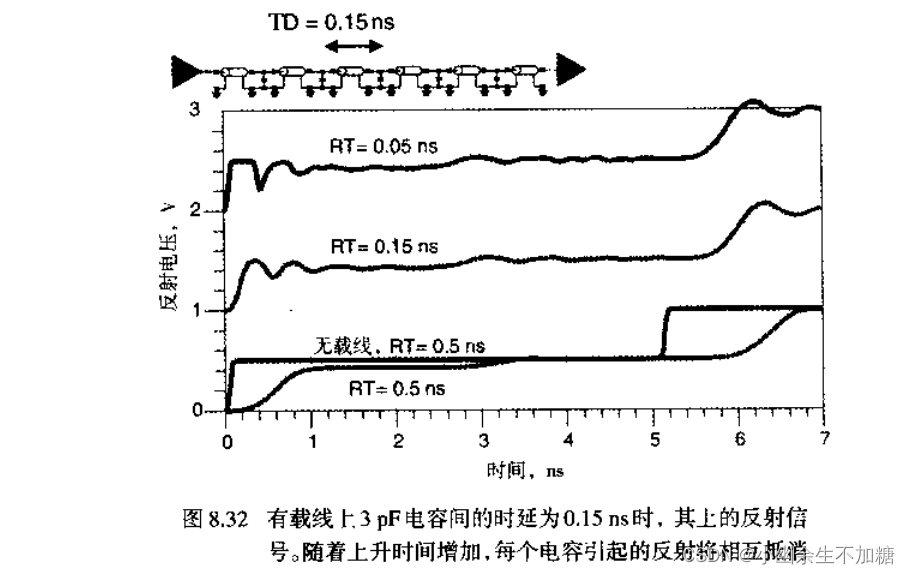

12.均匀分布着容性负载的传输线称为有载线。有载线的信号将失真,而且上升边也退化,每个分立电容会降低它附近的阻抗。

13.当信号上升边大于容性突变之间的时延时,均匀分布的容性负载会降低导线的特性阻抗。在有载线上,电路板上这些额外的负载特性使导线的单位长度电容增加。单位长度电容越大,特性阻抗就越低,时延就越长,无载传输线特性阻抗和时延与长度单位电容及单位长度电感之间的关系为:

14.

(1)随着导线特性阻抗的降低,用于端接匹配的电阻也随之降低;

(2)分立电容的加大对导线的作用就是降低了特性阻抗并加大了时延,他在与过孔中所发生的的情况相同。

15.不同感性突变情况下的源端和接收端,近端信号的形状为先上升后下降,称为非单调性,即信号不是稳定的一致单调上升。

16.当信号的上升边通过电感器时,如果电容器的阻抗小于特性阻抗而且信号的上升边是线性上升的,则电感器的阻抗约为:

Z=L/RT

17.感性突变会引起反射噪声和时延累加,如上升边很短,信号的上升边主要由串联电感决定。则传输线信号的10%~90%上升边约为:

18.补偿的概念是尽量让信号感受不到很大的感性突变而是觉得遇到了与导线特性阻抗相匹配的一段传输线。

19.补偿这一技术适用于所有的感性突变,如过孔、电阻器等,根据焊盘上的电容量和电感总量,可以把实际突变看成容性或是感性的。

浙公网安备 33010602011771号

浙公网安备 33010602011771号