HyperLynx(二十九)高速串行总线仿真(一)

高速串行总线仿真(一)

1.高速串行接口

2.SERDES(串行/解串器)架构

3.高速串行链路仿真拓扑结构

4.高速串行信号仿真流程

5.IBIS-AMI模型

6.高速串行信号仿真方法

随着电子产品系统中数据传输速率的提高,互连传输带宽要求也越来越宽;而随着时钟

频率的提升,传统的并行接口技术已经成为数据传输的一大瓶颈。高速串行接口不仅提高了数据传输速率,还扩展了许多功能,从而满足了互连传输网络高带宽的需求,但是,高速串行传输也面临很多挑战,例如,怎样进一步提高数据传输速率?如何降低误码率(BER)?

如何保证信号和电源完整性的同时维持高功效不变,并优化设计效能?这些都是工程师需要面对的问题,但不管怎么样,高速串行信号已然是未来总线发展的趋势。

目前主要介绍使用 HyperLynx 中的两个重要串行通道仿真工具,即 IBIS-AMI 通道仿真

分析和 FastEye 通道仿真分析,并结合 PCIE串行总线分别介绍两种不同的分析仿真流程。通过学习,工程师可以在研发阶段深人了解及预防和解决高速串行传输所面临的问题。

1.高速串行接口

目前,对于高速串行接口没有一个明确的定义,只是在工程领域,一般把串行总线接口

称为高速串行接口。

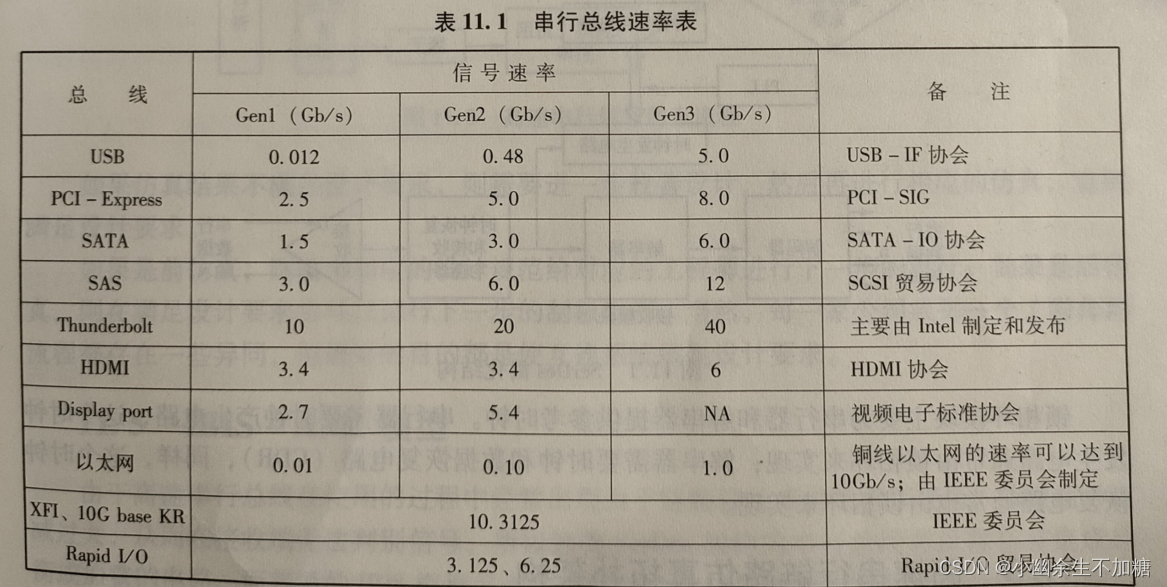

从当前的信号速率来看,几乎所有的串行接口的速率都达到 Gb/s以上,如表所示

为当前主流的一些串行总线的信号速率。