HyperLynx(三十)高速串行总线仿真(二)

高速串行总线仿真(二)

仿真实例

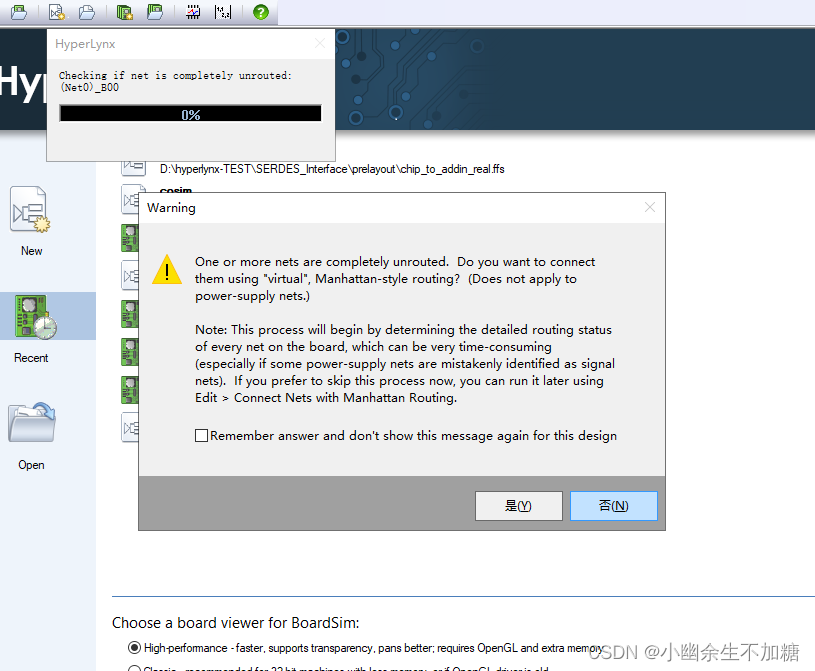

1.探索多层板中的PCI-E串行通道

2.设置叠层以减小损耗

3.分析通道的不同配置对损耗的影响

4.检测驱动端规范

5.检查接收器规范

6.通过仿真得出整个通道的驱动约束限制

1.探索多层板中的PCI-E串行通道

在本节练习中,将探索在不同的通道配置下分析 PCI-Express多层板设计。

(1)打开HyperLynx.

(2)使用“File”一“Open Multiboard Project”来打开 Entire_System-pjh,路径如下:C:

\Adv_HL_Trng\SERDES_Interface \postlayout \MultiBoard

(3)当加载设计时遇到如图所示信息提示,选择“否”。

(4)通过“Models”→“Edit Model Library Paths”添加以下路径:C:\Ady_HL_Tng\SERDES_Interface\models。

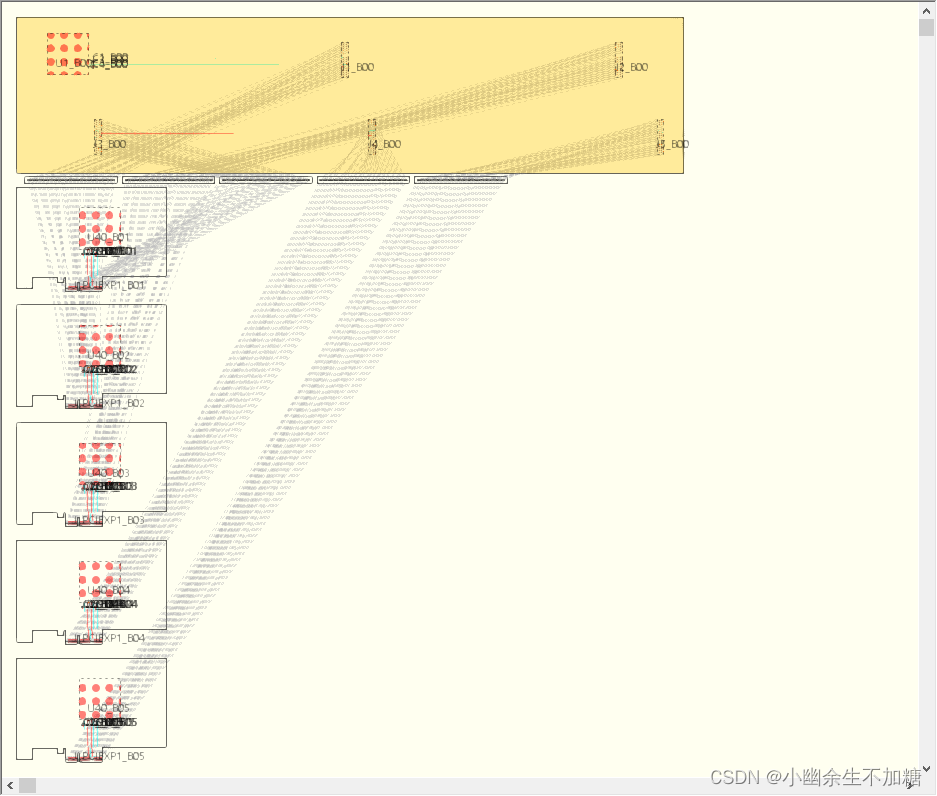

(5)选择网络“CHANNEL1_TX_TO_J1_P”,如图所示。

浙公网安备 33010602011771号

浙公网安备 33010602011771号