HyperLynx(三十二)高速串行总线仿真(四)

高速串行总线仿真(四)

在上节的基础上

1.通过导出到LineSim验证一个串行通道

2.快速眼图仿真

3.高速串行总线设计注意事项

1.通过导出到LineSim验证一个串行通道

接下来,将导出网络到LineSim,并为电容分配SPICE模型。然后,将添加封装和串行电容模型,进一步对不同的终端方案进行假设分析。

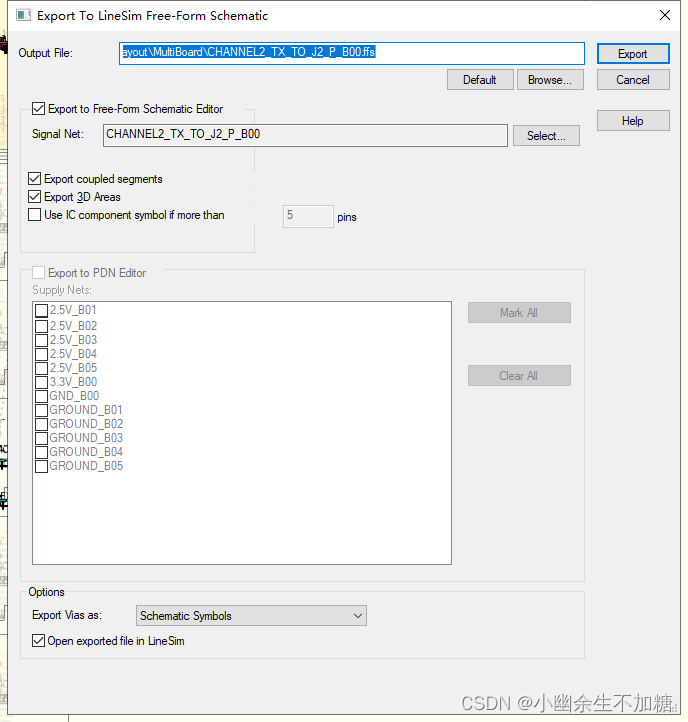

(1)选择“Export” →“Net To”→“Free Form Schematic”,打开如图所示对话框。

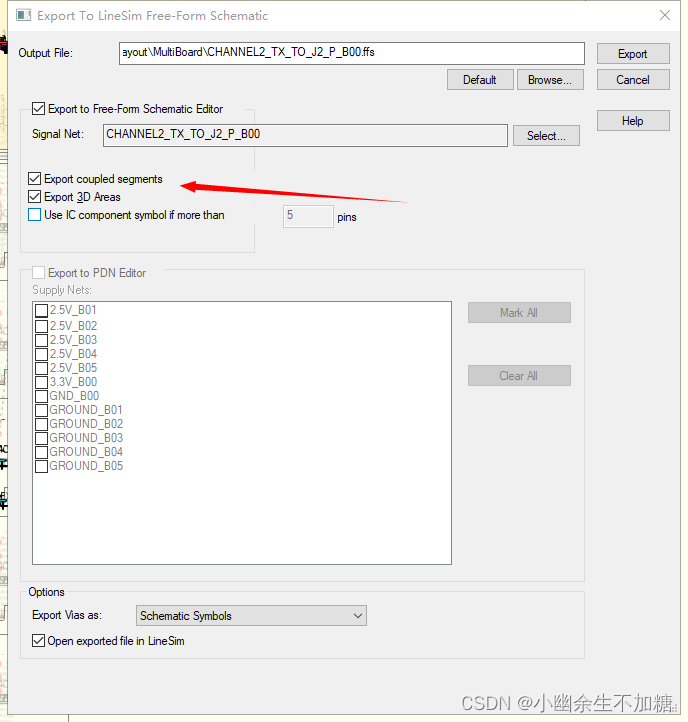

(2)使能“Expont coupled segments”选项,如图所示,单击“Export”按钮。

注意到,驱动引脚没有导出为差分缓冲器,但接收端引脚是差分缓冲器。这是由于SPICE模型被分配到了驱动端,而以[diff pin]为关键词的IBIS模型分配到了接收端。因此知道接收端是一个差分接收器。同时也注意到S参数连接器模型也被导出为一个封装/连接器符号。

(3)删除C3_B00和C4_B00符号(记得之前在多板工程中已经将它们改为电阻)。

(4)用已经分配cap0402.sp的封装和连接器模型替代它们。

①在电路图中放置封装连接器符号非。

②双击符号。

③选择“cap0402.sp”模型&

浙公网安备 33010602011771号

浙公网安备 33010602011771号