EMC学习笔记(三)滤波

滤波

1.概述

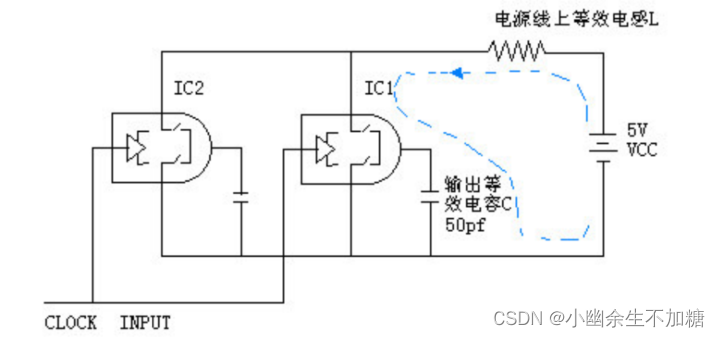

在PCB设计中,滤波既包括专门的信号滤波器的设计,也包括大量电源滤波电容的使用。滤波是必不可少的:一方面,通过其它方式并不能完全抑制进出设备的传导噪声 ,当电气信号进出设备时,必须进行有效地滤波: 另一方面,集成芯片的输出状态的变化或其它原因会使芯片供电电源上产生一定的噪声 ,并影响该芯片本身或其它芯片的正常工作 。下面的例子说明了 电源滤波电容的作用 。电源走线上存在一定的电感。

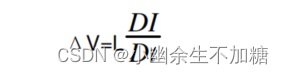

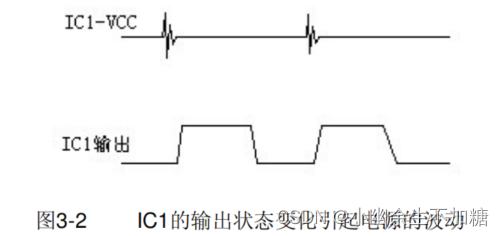

如图所示,当IC1的输出由0变到1时,需要电源VCC对电容C充电 (dl)来实现,电源供电回路上对于脉冲充电电流存在等效电感L,当电流变化时,就会在等效电感L上产生电压△V

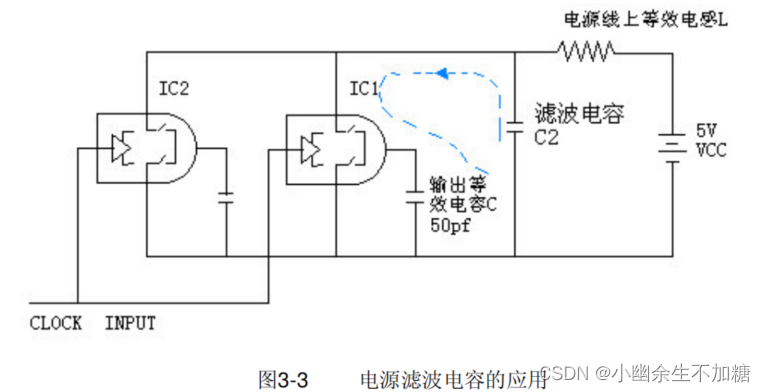

△V一方面可以引起电路功能失效,另一方面是主要的辐射源,引起单板辐射增大,为了消除上述影响,采用滤波电容可以解决,改进后的电路如图所示。

如图所示,当IC1的输出由0到1变化时,不再是通过VCC提供dl,而是通过滤波电容C2的放电来提供所需要的瞬时电流,完成电路的逻辑转换,这样就可以避免电源线上等效电感L而引起的电源噪声。

2.滤波器件

常用的滤波器件有很多种,包括电阻、电感、电容、铁氧体磁珠等。

2.1 电阻

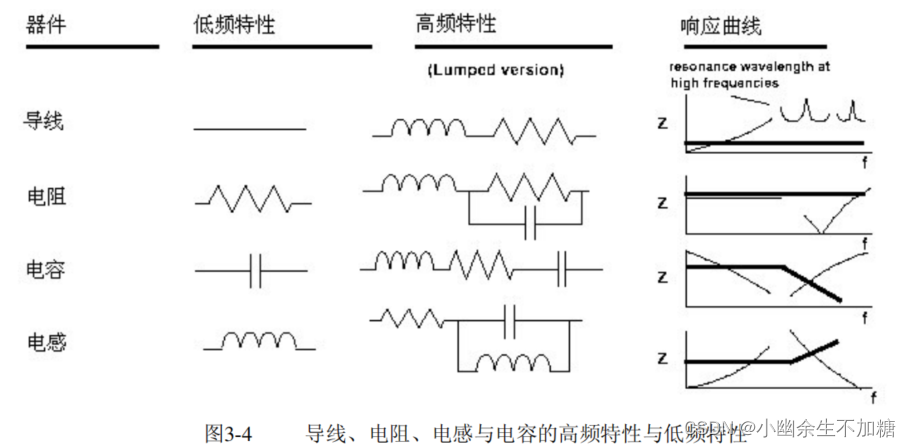

电阻不能单独用来做滤波的用途,它一般与电容结合起来组成RC滤波网络使用。电阻的特性如图3-4所示。由图可知,由于引线电感(ESL) 与寄生电容的存在,电阻的高低频特性有很大的差异,这一点在设计滤波器时应该加以注意。

如图所示同时给出了导线的低频特性与高频特性的区别,可以进一步地说明滤波的重要性。

2.2 电感

电感的高、低频特性如图所示。由于引线电阻 (ESR) 和寄生电容的存在,使电感存在一个自谐振频率f,电感在低于f的频率范围内表现为电感的特性,但在高于f的频率范围内,则表现为电容的特性。这是在计算滤波器的插入损耗时需要尤其注意的地方。

2.3 电容

电容也是滤波电路中最为常见的器件。后面进行详细介绍。

2.4 铁氧体磁珠

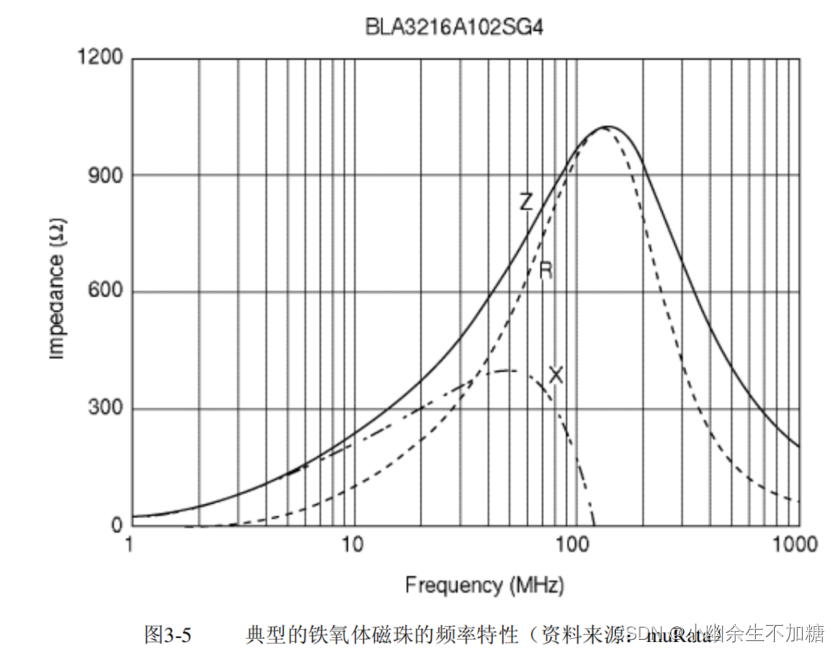

铁氧体磁珠也是滤波常用的器件。用于电磁噪声抑制的铁氧体是一种磁性材料 ,由铁、镍、锌氧化物混合而成,具有很高的电阻率,较高的磁导率(约为100~1500) 。铁氧体磁珠串接在信号或电源通路上,用于抑制差模噪声。当电流流过铁氧体时,低频电流可以几乎无衰减地流过但高频电流却会受到很大的损耗 ,转变成热量散发。铁氧体磁珠可以等效为电阻与电感的串联但电阻值与电感值都是随频率而变化的。典型的铁氧体磁珠的频率特性如图所示。

铁氧体磁珠与普通的电感相比具有更好的高频滤波特性 。铁氧体在高频时呈现电阻性,相当于品质因数很低的电感器,所以能在相当宽的频率范围内保持较高的阻抗 ,从而提高高频滤波效能。

2.5 共模电感

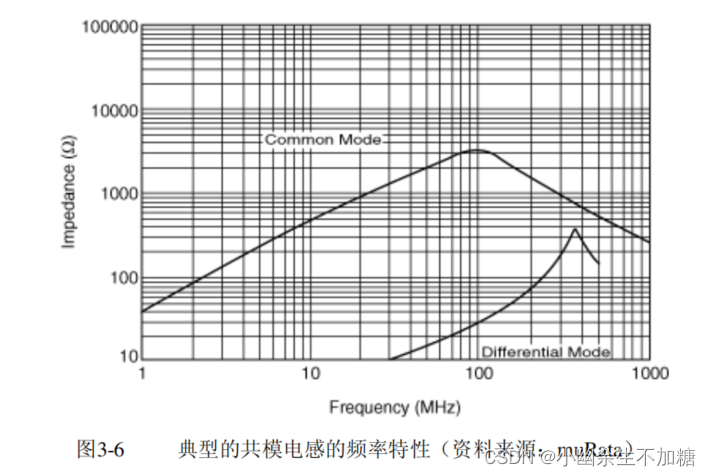

共模电感插入传输导线对中 ,可以同时抑制每根导线对地的 共模高频噪声。通常的做法是把两个相同的线圈绕在同一个铁氧体环上 ,铁氧体磁损较小,绕制的方法使得两线圈在流过 共模电流时磁环中的磁通相互叠加,从而具有相当大的电感量,对共模电流起到抑制作用,而当两线圈流过差模电流时,磁环中的磁通相互抵消,几乎没有电感量,所以差模电流可以无衰减地通过。典型的共模电感的特性曲线如图所示。

3.滤波电路

3.1 滤波电路的形式

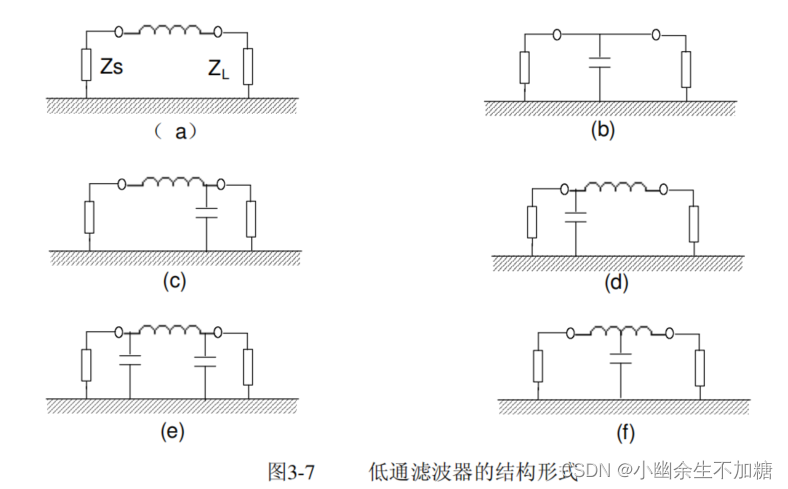

在EMC设计中,滤波的作用基本上是衰减高频噪声,所以滤波器通常都设计为低通滤波器滤波电路的典型结构形式如下图所示。

图(a)所示为电感滤波器,适用于高频时源阻抗和负载阻抗较小的场合:

图(b) 所示为电容滤波器,适用于高频时源阻抗和负载阻抗较大的场合:

图 © 和 (d)所示为T形滤波器,前者适用于高频 时源阻抗较小、负载阻抗较大的场合,后者适用于高频时源阻抗较大、负载阻抗较小的场合;

图 (e) 所示为I型滤波器,适用于高频时源阻抗与负载阻抗均较大的场合;

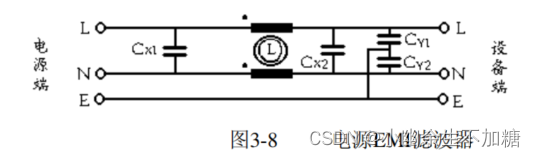

图 (f) 所示为T型滤波器,适用于高频时源阻抗与负载阻抗都比较小的场合。还有一种经常应用的滤波器是电源用EMI滤波器。其结构形式如图所示。

3.2 滤波电路的布局与布线

滤波电路在布局布线时必须严格注意。

(1) 滤波电路的地应该是一个低阻抗的地,同时不同的功能电路之间不能存在共地阻抗:

(2) 滤波电路的输入输出不能相互交叉走线,应该加以隔离;

(3) 在滤波电路的设计中,同时应该注意使信号路径尽量短、尽量简洁: 尽量减小滤波电容的等效串联电感和等效串联电阻;

(4) 接口滤波电路应该尽量靠近接插件。

4.电容在PCB的EMC设计中的应用

4.1 滤波电容的种类

电容在PCB 的EMC设计中是使用最为广泛的器件。电容按功能的不同可以分为三种:

去耦(Decouple) : 打破系统或电路的端口之间的耦合,以保证正常的操作。

旁路 (Bypass): 在瞬态能量产生的地方为其提供一个到地的低阻抗通路 。是良好退的必备条件之一。

储能 (Bulk) : 储能电容可以保证在负载快速变到最重时电压不会下跌。

4.2 电容自谐振问题

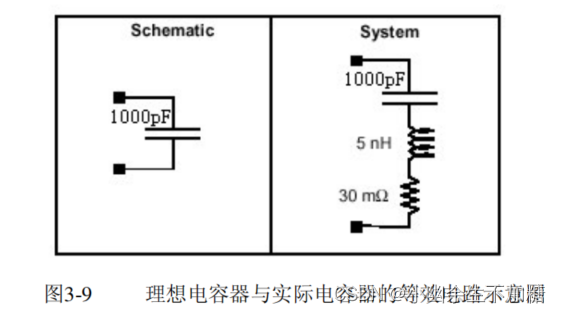

我们用来滤波的电容器并不是理想的电容器,在系统中实际表现为理想电容与电感和电阻的串联。如图所示。

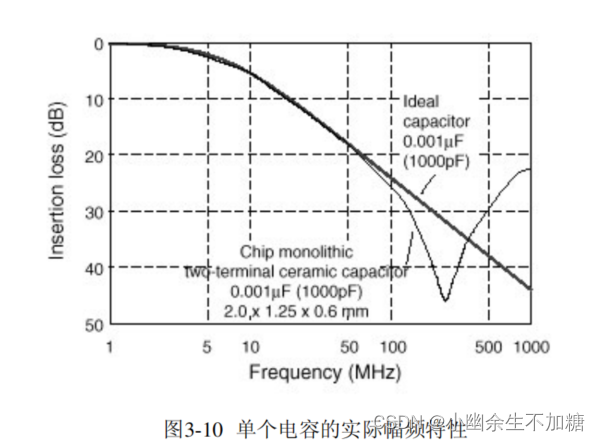

多层电容器 (Muti-Layer Capacitor) 在装配到PCB板上时会产生将近5nH的寄生电感,再加上约30m欧的引线电阻,其频率特性表现为如图所示的曲线。滤波电容将不是理想的低通滤波器,实际的插入损耗特性表现为以自谐振点为中心的带通滤波电路。

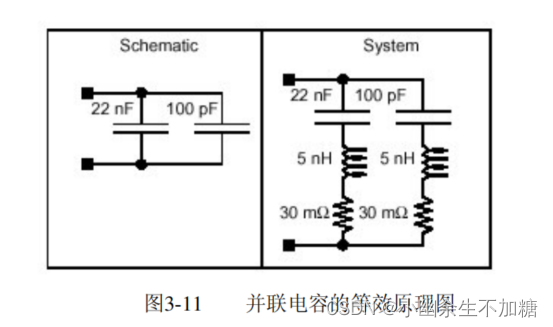

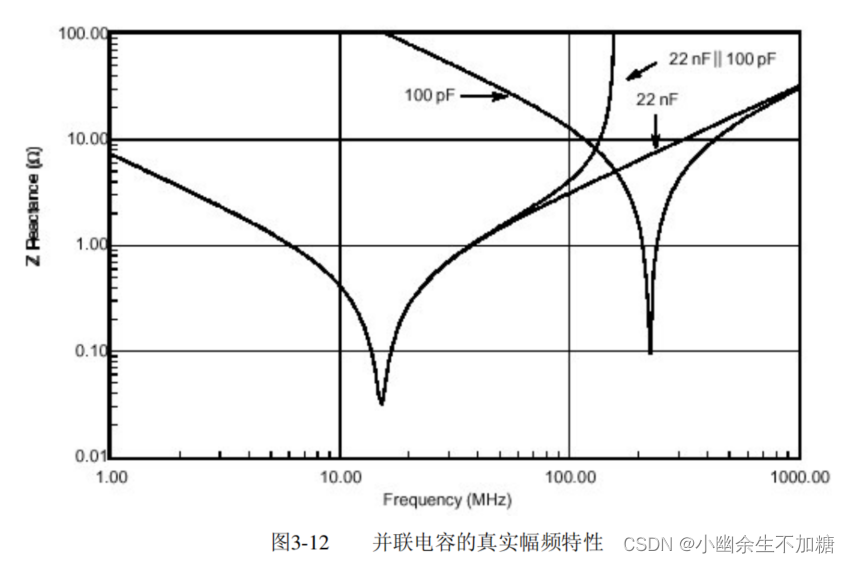

两个电容串联时,由于ESL (等效串联电感) 和ESR(等效串联电阻) 的存在,会产生反谐振问题。图3-11给出了电容并联的等效原理图,图给出了它们的真实的幅度-频率特性。

图显示,在将近15MHz到175MHz的一个较宽的频带内,并联电容的阻抗比单独一个大电容的阻抗要来的大,由于两电容产生了谐振,在150MHz处产生了一个阻抗的峰值,系统其他部分在该频率范围内产生的能量只能有很少的一部分被旁路到地平面。

4.3 ESR对并联电容幅频特性的影响

图所示的阻抗的峰值与电容器的ESR的值成反比,随着单板设计水平与器件性能的提高.并联电容的阻抗的峰值将会随着ESR的减小而增加,并联谐振峰值的形状与位置取决于PCB板的设计与电容的选择。

有几条原则应该了解:

1、随着ESR的减小,谐振点的阻抗会减小,但反谐振点的阻抗会增大;2、n个相同电容并联使用时,最小阻抗可能小于ESR/n;

3、多个电容并联时,阻抗并不一定发生在电容的谐振点;

4、对于给定数量的电容器,比较好的选择是电容值在一个较大的范围内均匀展开,各个电容值的ESR适中:比较差的选择是仅有少量的电容值,而且电容的ESR都非常小。

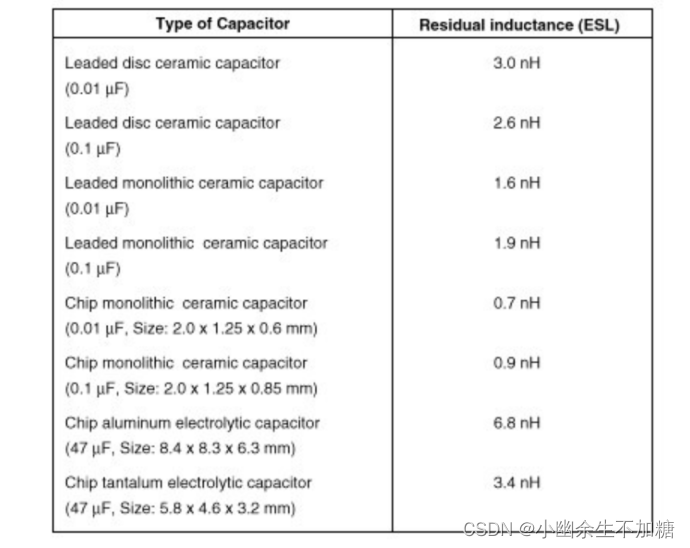

4.4 ESL对并联电容幅频特性的影响

电容封装和结构不同,ESL也不同,几种典型封装电容的ESL如下表所示:

电容的ESL与电容值一起决定电容器的谐振点与并联电容器的反谐振点的频率范围。在实际的设计中,应该尽量选用ESL小的电容器。

4.5 电容器的选择

对于RF设计而言,陶瓷电容器、聚醋纤维电容器和聚苯乙烯薄膜电容器都是很好的选择。对于EMI滤波器来讲,对电容器的介质材料要求并不高,常见的X7R、Y5V和Z5U等松散介质都是不错的选择:通常绝对的电容值、电容器的温度系数、电压变化系数等并不重要不同种类、不同容值的电容滤波范围是不同的,下面是典型的插入损耗比对效果:

由上图可看出,同为0805封装的贴片陶瓷电容,0.01UF的电容比0.1UF的电容具有更好的高频滤波特性 ; 建议板极工作频率高于 50MHZ的单板 (如传输 、MUSA的多数单板 ) 全部使用0.01UF的滤波电容,而不是我们目前大量采用的0.1UF的滤波电容。

4.6 去耦电容与旁路电容的设计建议

1、以供应商提供的产品资料上的自谐振特性为基础选择电容,使之符合设计的时钟速率与噪声频率的需要。

2、在所需要的频率范围内加尽可能多的电容。例如,图3-12所示的22nF的电容的自谐振频率将近为11 MHz,有用的阻抗 (Z1欧姆) 范围为6M~40MHZ,你可以在该频带范围内加尽可能多的电容,以达到需要退耦的水平。

3、在尽可能靠近IC每个电源管脚的地方,至少放一个去耦电容器,以减小寄生阻抗。

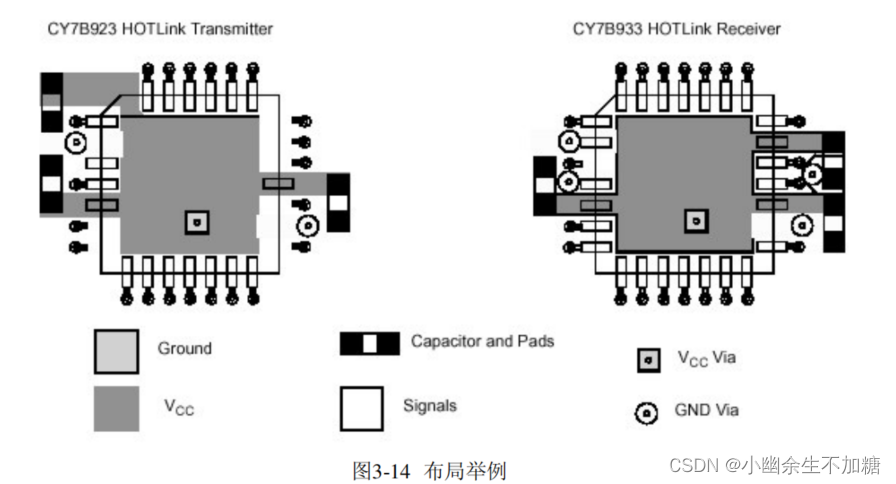

4、旁路电容与IC尽可能放在同一个PCB平面上。图3-14给出了一个示例。图有一个需要特别注意的地方:在两种布局中,Vcc网络都只有一个点连到Vcc平面。这样做,使得IC内外的噪声都必须通过这个唯一的过孔走到电源平面上去,过孔的附加阻抗帮助避免了噪声向系统其余部分的扩散。

5、对于多时钟系统可以将电源平面作图 3-14所示的分割,对每一个部分使用一种正确容值的电容器,被狭缝分隔的电源平面将一部分的噪声与其他部分的敏感器件分隔开来 ,同时提供了电容值的分离;

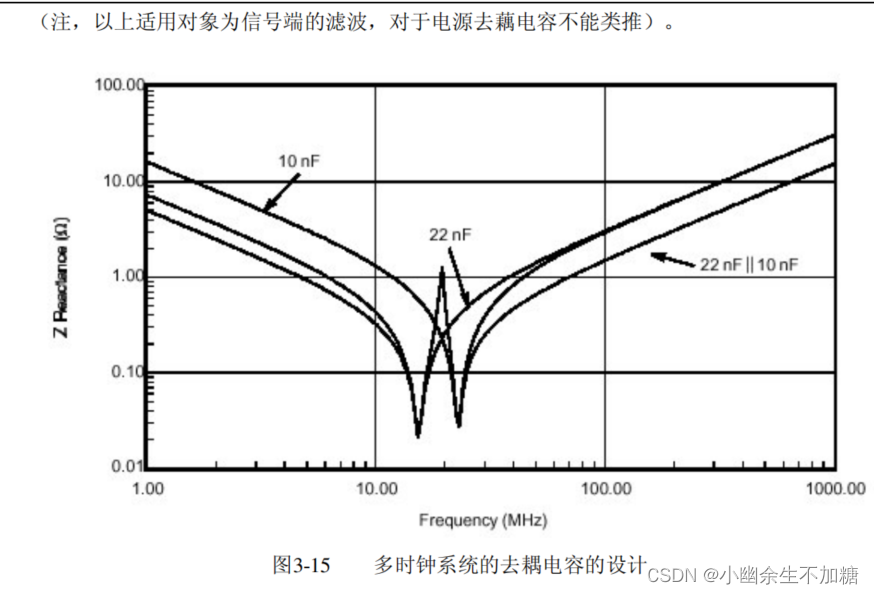

6、对于时钟频率在一个较宽的范围内变化的系统,旁路电容的选择甚为困难。一个较好的解决方法是将两个容值上接近2: 1的电容并联放置,这样做可以提供一个较宽的低阻抗区 ,和一个较宽的旁路频率,图3-15给出了这种搭配的一个例子 ,可以看到,阻抗峰值仍然产生了 ,但却小于1.5欧,而可用的频率范围 (阻抗小于1.5欧) 则扩展到将近 3.25MHz到100MHz的范围,这种多退耦电容的方法只在一个单独的IC需要一个较宽的旁路频率范围而且单个电容无法达到这一频带时才使用。而且,容值必须保持2: 1的范围内,以避免阻抗峰值超过可用的范围。

4.7 储能电容的设计

储能电容可以保证在负载快速变到最重时供电电压不会下跌。储能电容可分为板极储能电容、器件级储能电容两种:

A,板极储能电容:保证负载快速变到最重时,单板各处供电电压不会下跌。在高频、高速单板 (以及条件允许的背板),建议均匀排布一定数量的较大容值的铝电容 (1uf、10uf、22uf、33uf),以保证单板同一电压的值保持一致。

B,器件级储能电容: 保证负载快速变到最重时,器件周围各处供电电压不会下跌。对于工作频率、速率较高、功耗较大的器件,建议在其周围排放1一4个较大容值的钮电容 (1uf10uf、22uf、33uf) ,以保证器件快速变换时其工作电压保持不变

储能电容的设计应该与去耦电容的设计区别开来。有以下设计建议:

1、当单板上具有多种供电电压时 ,对一种供电电压储能电容仍然只选用一种容值的电容器般选用表贴封装的Tantalum电容 (钜电容),可以根据需要选择10uf、22uf、33uf等:

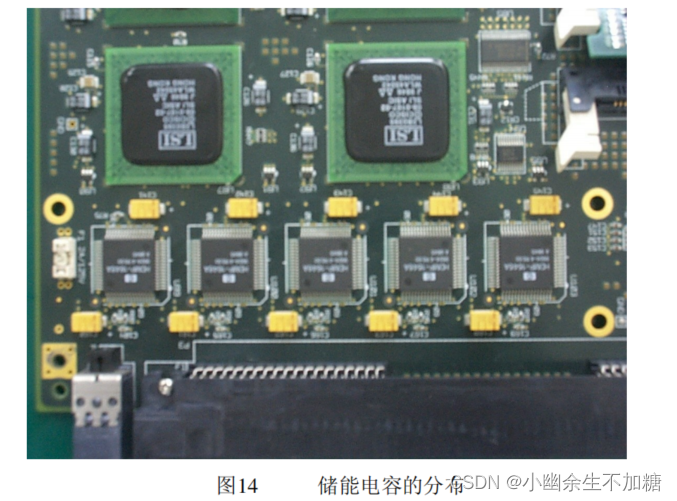

2、不同供电电压的芯片构成一个群落,储能电容在这个群落内均匀分布,如下图所示:

浙公网安备 33010602011771号

浙公网安备 33010602011771号