高速DSP系统设计参考指南(五)印制电路板或PCB布局

(五)印制电路板或PCB布局

所有电路设计完成后,下一步是电路板布局。这是开发过程中非常关键的一步,因为滤波电路的有效性取决于元件相对于 DSP引脚的放置位置。此外,电路板布局对噪声、串扰和传输线效应有很大影响,因此优化布局可以将这些影响降至最低。首先,设计师需要确定PCB 的最少层数,然后配置电路板叠层。以下是一些通用指南。

进行布局实验,并参考DSP 参考设计包,找出从DSP输出信号所需的最少层数。如果可能,复制TI推荐的精确布局。考虑在接地层和电源层之间屏蔽高速信号的需求。USB、DDR、以太网和 RapidIO 等总线是否需要严格的差分阻抗规格?PCB制造是否需要一定的走线宽度和间距?这决定了走线是否可以在小间距 BGA封装的球之间布线。为了实现良好的信号完整性和最小的趋肤效应损耗,走线宽度应保持在4密耳至 12密耳之间。常见的选择是5密耳走线和5密耳间距。

一个电源层和一个接地层是否足够?

DSP 系统需要受控阻抗板吗?这种方法成本较高,但可以从信号完整性的角度优化电路板。

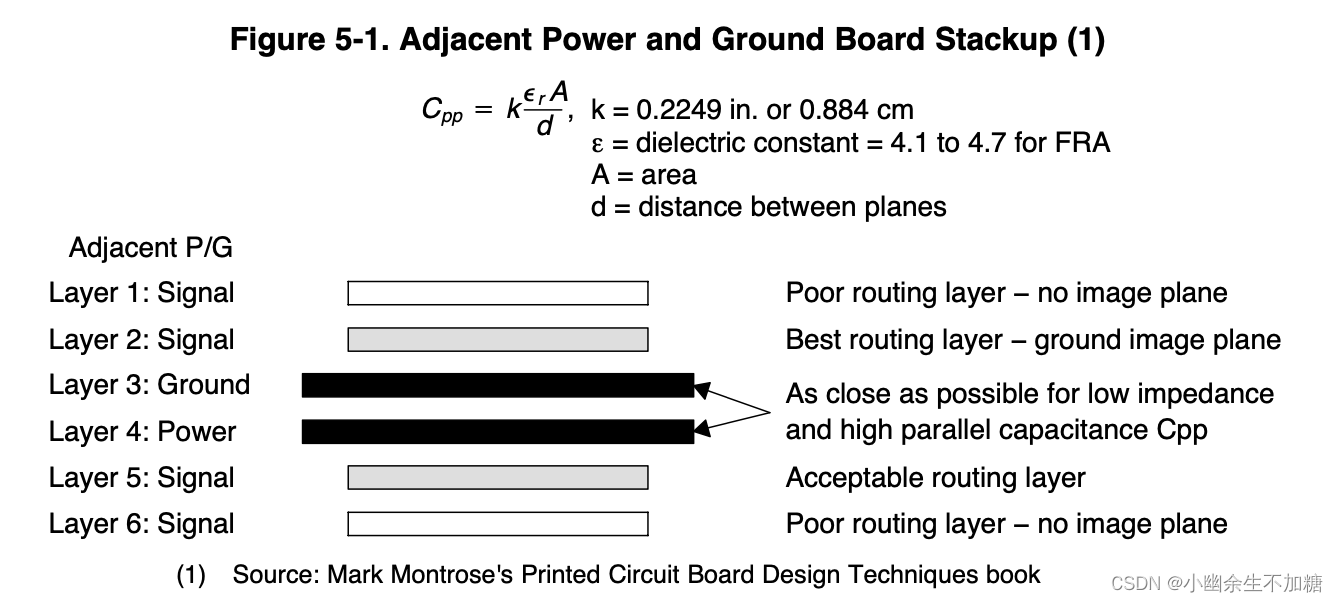

通常使用两种PCB 层叠拓扑结构:相邻电源层和非相邻电源层和接地层。Figure 5-1 显示了针对相邻电源和接地拓扑在 6层 PCB 上实施设计时,每层可以做什么,不可以做什么。

使用这种层叠结构时,需要注意以下几点:

如 Cpp 公式所示,电源层与接地层之间的距离d决定了电路板电容。缩短距离会增加电容,也会降低高频阻抗。限制因素是在保持设计质量和可靠性的同时,各层之间的紧密程度。

将高速信号布设在电源层和接地层旁边的层上。

最佳布线层是第2层,因为它靠近接地层。这提供了最佳的电流返回路径,有助于减少辐射。这就是为什么建议在极高频率下工作的DSP 系统采用相邻电源和接地拓扑结构。

相邻的电源和接地拓扑不适用于 DSP 系统,因为DSP 系统需要许多层来将信号从DSP 略由出去并与其它电路接口。

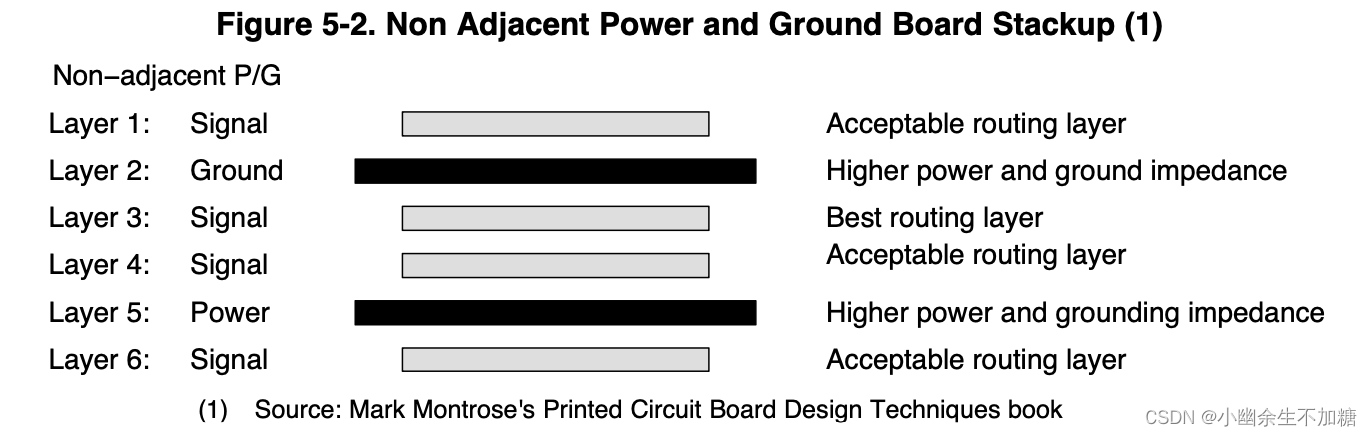

Figure 5-2 显示了非相邻电源和接地拓扑的典型 PCB叠层。电源层和接地层分别位于第5层和第2层。第3层最适合高速走线布线,而第1层、第4层和第6层也可接受。如图所示,每个布线层都靠近接地层或电源层。第3层最好,因为它不仅靠近接地层,而且受到其下的电源层的保护。这种方案最适合工作频率不是很高的难以布线的DSP 系统。需要记住的一点是,对于工作频率超过300MHz 的系统,电路板电容变得非常重要。

以下是进行非相邻板叠层设计的规则:

对于非相邻拓扑结构,电容等式 Cpp 所示的电路板电容较低,日电源层和接地层之间的电路板阻抗较高。这与系统所需的低噪声和低EMI 正好相反。

这种拓扑结构需要更多高频去想电容来补偿电路板特性。

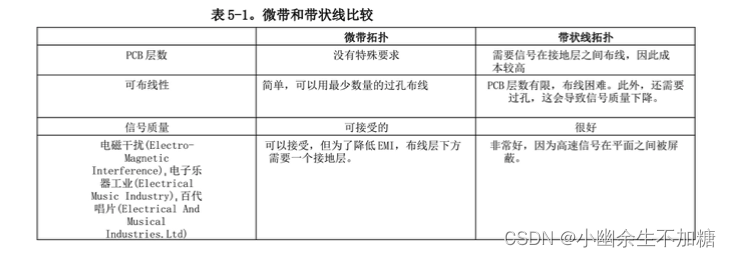

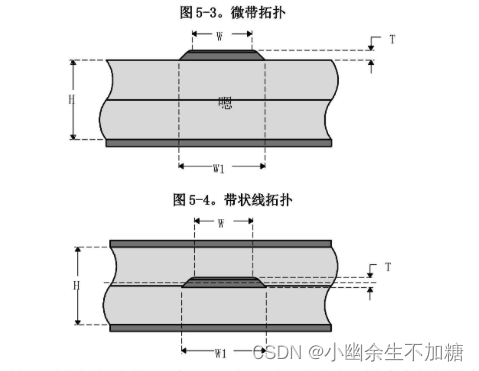

一旦决定了电路板叠层,下一步就是确定在布线层上布线信号的最佳方式。Table 5-1 显示了两种主要信号路由技术的优缺点

设计人员通常会做出妥协,使用两种拓扑结构,其中一些关键信号在接地层和电源层之间走线。

PCB 布线和电路板层叠是电磁干扰的主要来源,因此设计人员需要采用最佳实践来减少辐射。一个例子是使用镜像层,即位于布线层旁边的接地层,为高速信号提供低电感电流迈回路径。镜像层有助于减小电流环路面积,并将接地层上的电位差降至最低。Clayton 进行的实验比较了有和没有图像平面的 PCB的EI。他们证明,具有镜像平面的PCB在整个频谱范围内的EMI 降低了约 15dB。