高速DSP系统设计参考指南(四)DSP电源设计

1.电源设计的重要性

电源设计可能是高速 DSP 设计中控制噪声和辐射的整个过程中最具挑战性的一个方面。

这主要是因为动态负载切换条件的复杂性。其中包括DSP 进入或退出低功耗模式、总线争用和去棉电容充电导致的过大浪涌电流、去码和布局不当导致的较大电压下降,以及使线在调节器输出过载的振荡。

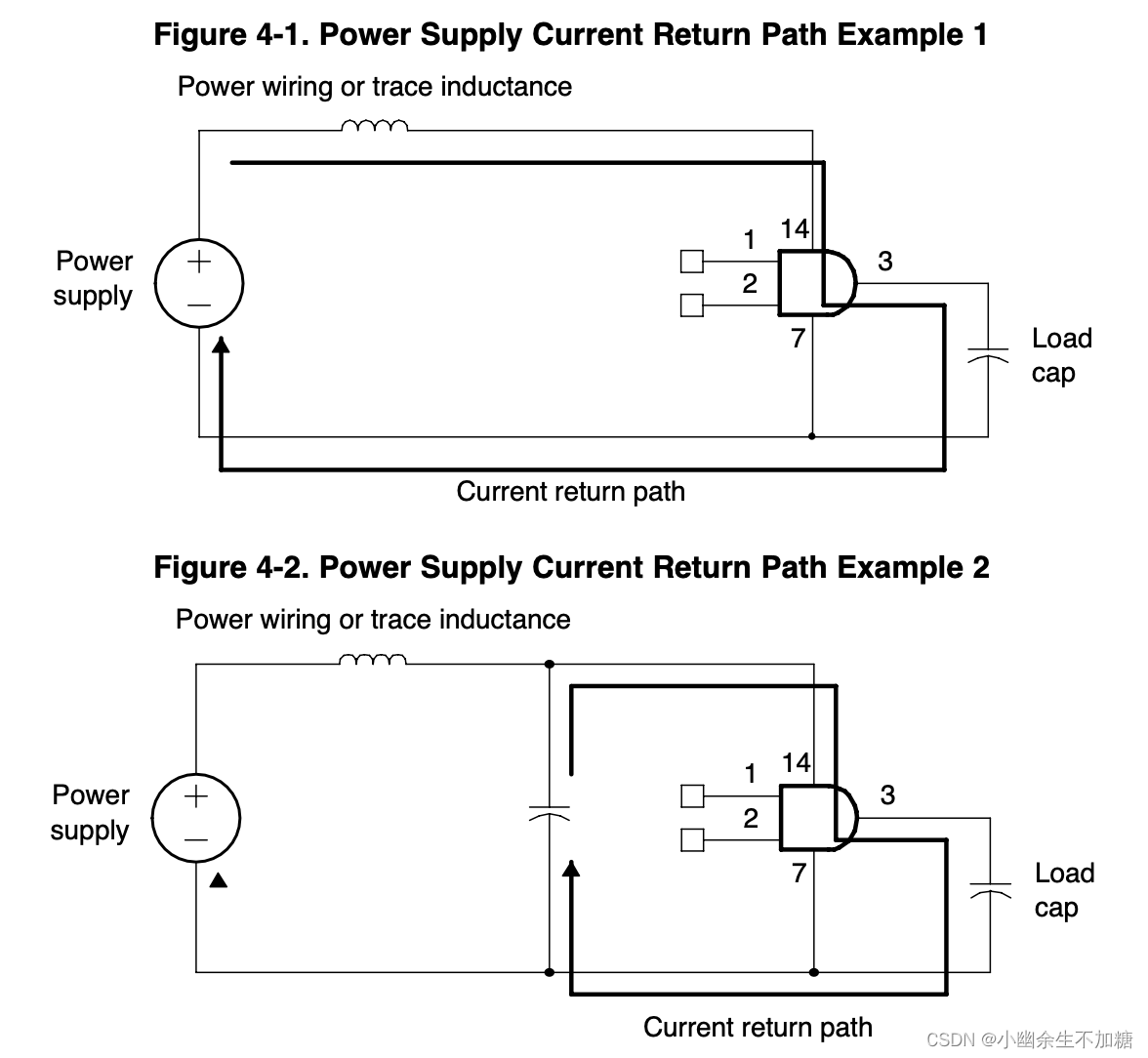

所有DSP 系统都需要干净构定的电源设计。Figure 4-1 和Figure 4-2 显示了两条电路,其中一条,Figure 4-2在DSP附近有一个去祸电容。假设电源走线电感相同,更大的动态电流返回路径会导致更大的电源电压下降和更大的电磁辐射这可能会导致非常难以调试的随机系统故障。

系统设计人员面临的最大挑战之一是确定特定应用中DSP 的可接受噪声水平。DSP 数据手册明确规定了工作条件,但无法解释高速系统的动态特性。这是因为动态开关特性在很大程度上取决于实际的系统设计和布局。以下是电源设计过程中必须解决的一些重要问题:

电源瞬态响应,例如负载调节、线路调节、电源纹波、电源噪声抑制和多轨电源时序控制。

电源去,以确保DSP 引脚的压降最小。

线性调节器与开关调节器。

电源层与电源走线。

电源斜坡期间和稳态下的DSP 浪涌电流。

电源循环:DSP 启动期间无残余电压。

电源轨排序:先内核后 IO还是先 IO后内核。

使用开关调节器为 PLL、音频编解码器、视频编码器和解码墨供电时要小心。

在电源斜坡期间始终置位复位,以降低内部DSP 总线争用的可能性。

2.DSP电源架构考虑

过度的电源噪声会产生以下有害影响:

电压下降、去楞电容不足或电流不足可能会导致随机逻辑故障。这很难调试,甚至可能需要重新设计系统以消除噪声。

电压调节不当会导致可靠性问题或系统意外关闭。

时钟电路可能会出现过度抖动,尤其是PLL。

辐射可能会上升到难以通过EC测试的水平。

视频和音频系统上的可视和可听伪像。

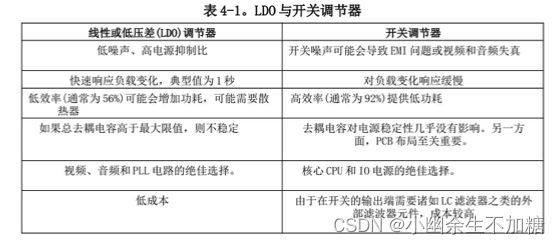

设计人员有三种主要方法来克服这些问题:稳压器设计(线性与开关式)、去耦技术和PCB布局。设计人员最重要的决策之一是使用线性调节器还是开关调节器。这一决策需要充分了解电源的特性以及电源对系统吸声性能的影响。电源本身的设计超出了本文档的范围。让我们看看线性调节器和开关调节器之间的区别:

表4-1 将有助于确定哪种电源解决方案更适合该应用。下一步是确定功耗以及是否需要电源时序控制。

一般来说,TI DSPs 至少有两个电源轨,内核和IO。内核和IO 电压的上升顺序会影响启动功耗,因此请参考器件数据手册,为特定 DSP 设计稳定的电源。以下是选择DSP 电源的推荐规则:

核心电压调节器设计:

请参考器件数据手册,了解内核电源的最大功耗。许多TI DSPs都带有功率电子表格,可以用来估计特定 CPU工作条件下的电流消耗。

选择至少两倍于最大核心电流能力的调节器。这提供了足够的余量来处理动态电流条件。

小心目前的饥饿状况。启动期间,浪涌电流可能会在短时间内超过调节器的最大限值。所选调节器应具有软启动能力,以防止出现过热或过流关断情况。

核心电压调节器的最后一个设计步骤是是否需要散热器。

IO 电压调节器设计:

I0 电压调节器的设计取决于特定应用中的外部负载。对于快速开关信号,I0 电流由去耦电容提供,而不是由调节器本身提供,因为存在与电源走线和电源层相关的寄生电感。动态电流计算将在去病部分显示。以下准则提供了一种为DSP本身设计 I0 电压调节器的保守方法。应当注意,这种方法仅适用于 DSP电源,而不是整个系统。

计算DSP 的输出数量。所有GPIOs 都应被视为输出。

将输出数量乘以数据手册中规定的源电流。

使用数据手册中规定的最大 IO 电流消耗,添加总源电流。

然后,将结果乘以 2,得到100%的余量。

由于传输线路的影响,IO 电流可能会在切换过程中出现浪涌,但这种情况会被本地 DSP 去耦电容吸收。

最后一步是确定是否需要散热器。

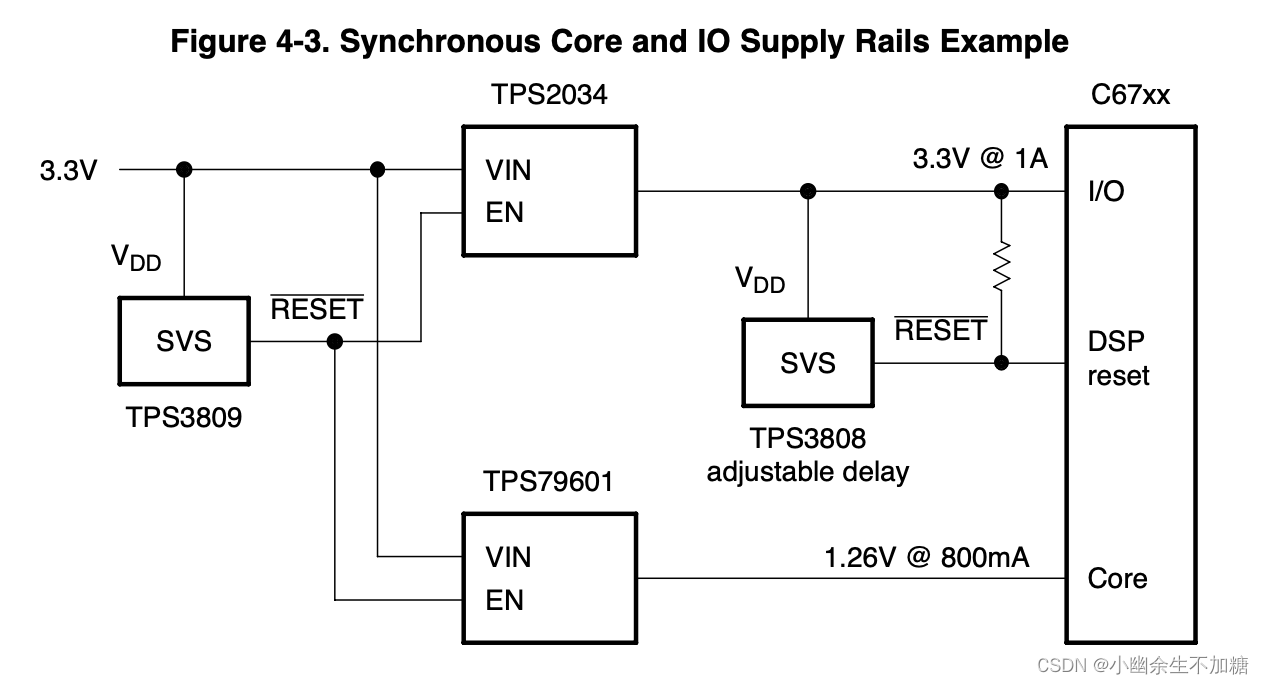

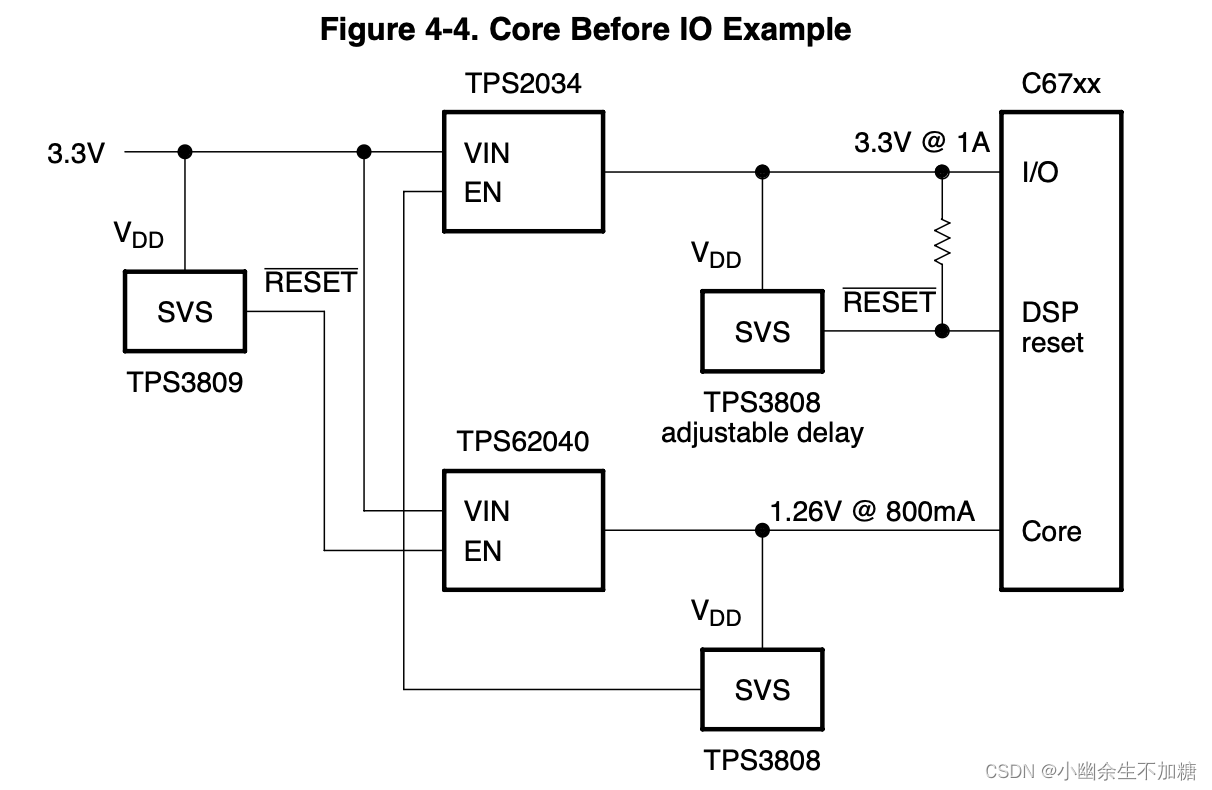

设计人员完成特定DSP 的电源架构后,下一步就是确定DSP 是否需要时序控制。例如,可以对供电轨进行排序,以便在 1O之前提升内核,反之亦然。正确的排序对于避免内部争用是必要的。

通电期间不正确的复位。Reset 置位时间必须长于数据手册中规定的最小复位脉冲。

核心和10 未在指定的时间限制内启动。通常,TI DSPs 不需要电源时序,但一个供电轨开启而另一个供电轨关闭有时间限制。

JTAG 仿真端口重置不正确。例如,TRST 需要稳定的低利率。耦合到该信号的过多噪声可能会导致启动问题或总线争用。

在释放reset 之前,引导模式配置引脚没有被驱动到正确的状态。请参考器件数据手册,确保配置引脚有适当的上拉和下拉,并且这些引脚在释放reset 之前已经达到稳定的逻辑电平。

3.电源去耦技术

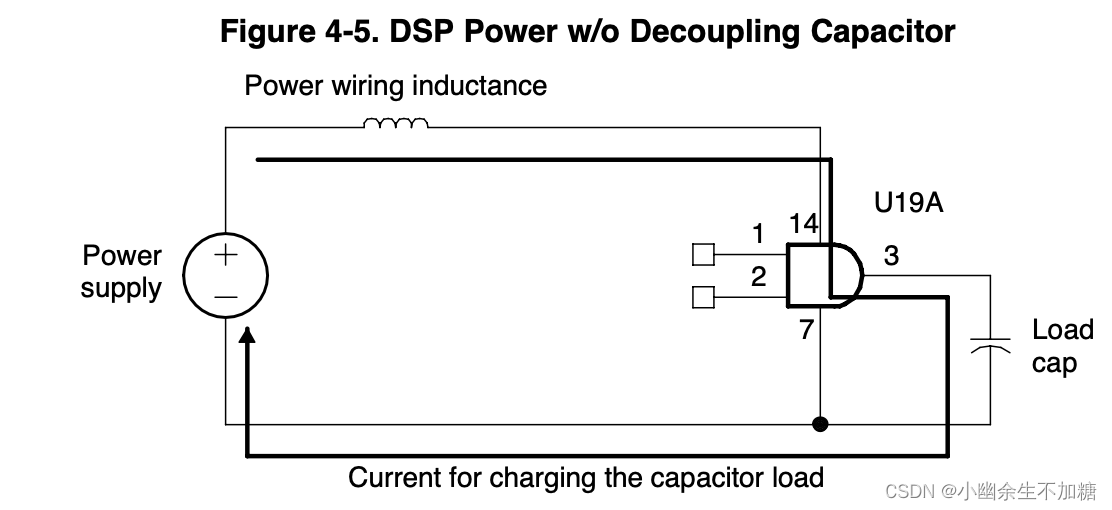

设计人员为DSP 选择电源架构后,下一步就是确定所需的去耦电容,以确保所有动态工作条件下的电源压降低于额定限值。例如,3.3V 10 电源的 5%容差额定值要求纹波小于 165mV。让我们首先考虑不使用去耦电容的情况,如图所示Figure 4-5。

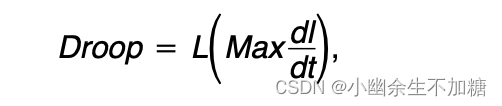

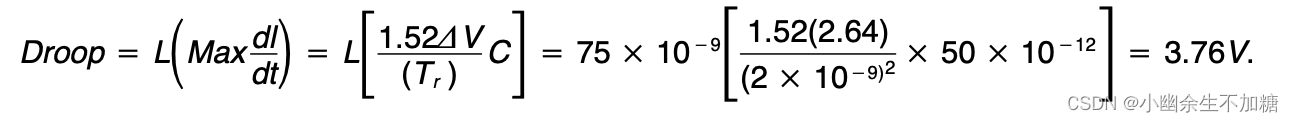

Figure 4-5标记为U19A的DSP驱动一个容性负载,并以高速开关。现在,假设调节器距离DSP 5英寸,并通过一条5密耳的走线连接到DSP。在快速开关期间,由于与走线相关的寄生电感,电源走线成为开路。这会在 DSP 引脚上产生一个较大的压降,其估算方法如下

其中L是寄生电感

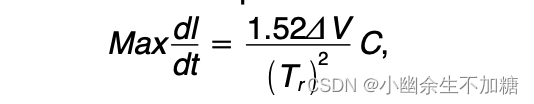

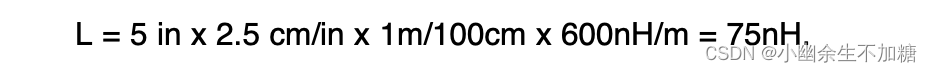

其中, V是开关电压,c 是负载电容,Tr 是上升时间。对于5英寸走线,Hyperlynx仿真器估计电感为600nH/m,电感L为:

假设Tr = 2nS,C-50pF(负载电容),6V = 3.3V或2.64V的80%,最大计算压降为:

本例表明,对于5英寸走线、2ns 信号、50pF 负载和3.3V

I0,最大电源压降为3.76Y。这种压降水平几乎肯定会导致随机系统故障。为了进行补偿,去括电容靠近DSP 放置,以提供开关期间所需的电荷。

从DSP系统中消除噪声的最佳方法是什么?

不同系统的噪声特性差异如此之大,以至于没有一种方法可以保证所有情况下的低噪声和低辐射。

3.1 一般经验法则解耦法

般来说,去耦电源噪声的理想方法是在DSP 的每个电源和接地引脚之间连接一个电容。通常,这在物理上是不可能的,因为DSP封装面积太小。因此,设计人员不得不做出妥协,减少去耦电容的数量,以适应DSP下方的一般区域,有关推荐的方法,请参考器件数据手册。但总的来说,这里是解耦的重要考虑因素。

只要空间允许,尽可能增加去想电容。

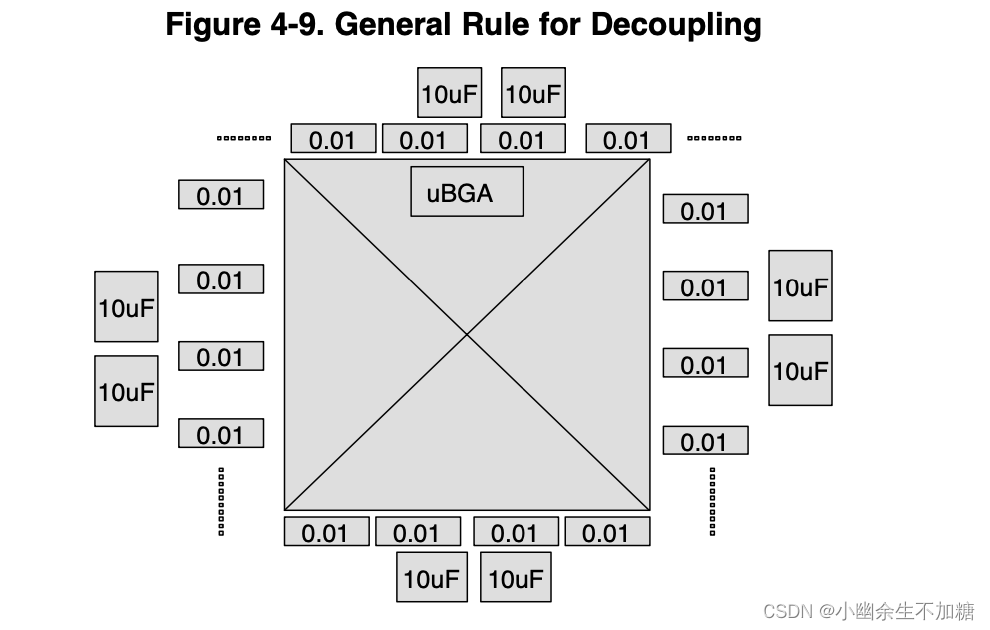

添加至少8 个大容量电容,4个用于内核,4个用于 I0电源。将每个大电容放置在DSP 的每个区域,区域定义为DSP 的一个边缘或一个角。大容量电容充当低频噪声滤波器和小去耦电容的电荷存储器件。使用四个较小的大容量电容器比使用一个大的分立元件更好,因为这样可以保证大容量电容器和去越电容器之间的充电路径更短,寄生电感路径更低。

请记住,所有电容都有等效串联电感(ESL)和等效串联电阻(ESR)。ESL和ESR 会降低滤波效果。因此,选择可以使用的最小表面贴装电容。

Figure 4-9 演示了一个去耦特定DSP 的好方案。请参考器件数据手册,了解更多详情。如图所示,0.01uF陶瓷电容用于去耦电容,10F 钮电容用作低频浅波元件。通常,设计人员必须返回并更改这些值,以针对其应用进行优化。一种好的方法是改变电容值,使10供电轨的电源纹波小于 50Y,内核供电轨的电源纹波小于 20Y,另一个好的规则是使用陶瓷电容进行去糕,使用钮电容进行低频滤波。这是因为钮电容的值高于陶资电容。这两种电容提供低 ESR和ESL,这是在宽电压和温度范围内工作的低噪声设计所需要的。

3.2 解耦分析方法

从DSP 系统去耦电源噪声的另一种方法是计算使电源纹波保持在一定限度内所需的总电容。类似于去糕的般规则,该方法提供了通常必须优化的起始值,DSP通常使用的大型球册阵列(BGA)封装就像 PCB 本身一样,从芯片到球有很长的走线。这些走线会产生千扰,容易受到串扰、电源电压下降和其它电气噪声的影响。不对称去想技术首先将DSP 分成4个区域,然后分别对每个区域进行去耦。在低速部分提供较少的去精电容导致噪声和电磁辐射的均匀降低。这种去耦技术的规则是:

核心电压去耦步骤:

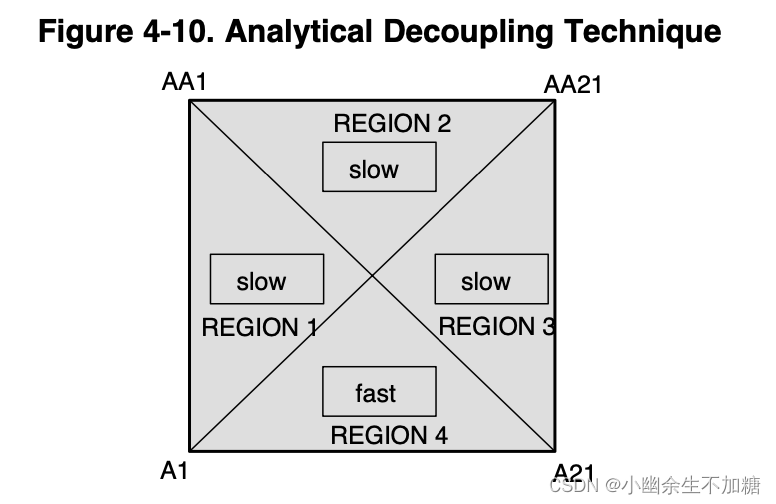

1.通过在DSP的4个角上画两条对角线,将DSP封装分成4个区域,如所示Figure 4-10。

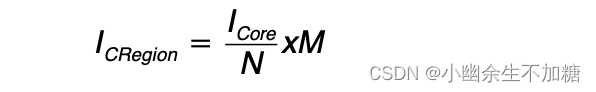

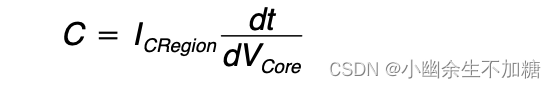

2.估算该区域内核电压的功耗I region,如下式所示:将最大器件电流ICore 除以内核电压引脚总数N,再乘以该区域内核电压引脚数M。

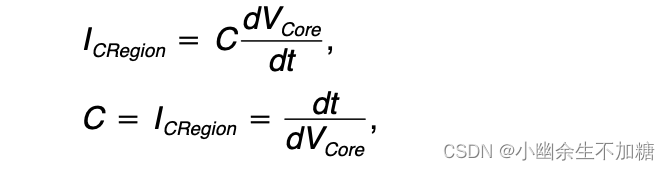

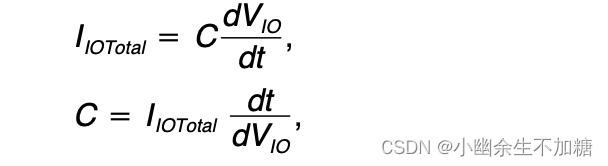

3.应用以下公式计算该区域的总去耦电容

其中,dt 是该区域最快的上升时间,dV 是内核电压允许的最大纹波,假设纹波为10 mv。

是内核电压允许的最大纹波,假设纹波为 10mv。

4.现在,将总去耦电容乘以 40,计算该区域的总体电容。Henry 0tt 推荐的体电容规则至少是去耦电容的10 倍。每个区域使用一个大容量电容,将大容量电容和去耦电容之间的寄生电感降至最低。

5.要计算去耦电容的数量,请查看PCB 面积,看看在电源引脚1.25 cm 范围内可以放置多少电容。然后,要计算去耦电容值,用总电容除以该区域允许的电容数量。最好选择自谐振频率等于特定区域最大频率的电容。例如,如果SDRAM端口运行在 100Mlz,则在该区域至少添加一个诺振频率为100MHz 的电容。每个区域内的其他电容器应该具有最高可能的谐振频率。这有助于在较宽的频率范围内减轻电磁干扰。

IO 电压去耦步骤:

1.通过在DSP的4个角上画两条对角线,将DSP封装分成4 个区域,如所示Figure 4-10。

2.统计 IO 电压的数量,以及每个区域的输入和输出。

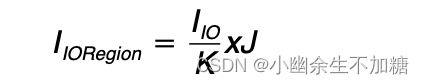

3.估算DSP 本身在区域IIORegion中的 I0 电流消耗,如下式所示:取最大器件电流规格 IIO 除以IO电压引脚总数K,再乘以一个区域内的 I0 电压引脚数J。

4.正如设计人员所知,总IO 电流不等于 DSP 本身的 IO 电流消耗。总IO电流的大部分取决于外部负载,例如阻性负载、容性负载或传输线负载。在这种设计中,让我们假设一种更差的情况,其中所有的 io 都是输出都装有传输线。这种情况下,每个输出电流等于输出电压除以传输线路的特性阻抗Zo。

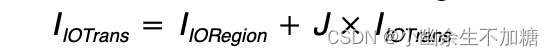

5.该区域的总IO电流为:

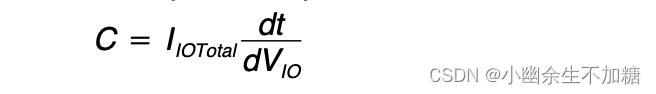

6.应用公式计算该区域总去耦电容:

其中,dt 是该区域最快的上升时间,d是I0 电压允许的最大纹波,假设纹波为50 mv。其中 dt 是该区域最快的上升时间,dV是 IO 电压允许的最大纹波,假设纹波为50mv。

7,现在,将总去耦电容乘以 40,计算该区域的总体电容。Henry 0tt 推荐的体电容规则至少是去想电容的10 倍。每个区域使用一个大容量电容,将大容量电容与去耦电容之间的寄生电感降至最低。

8.要计算去揭电突的数量,查着PC板面积,看看在引脚1.25 co范围内可以放置多少电容。然后,要计算去积电容值,用刚刚计算的总电容值除以该区域允许的电容数量。最好选择自请振频率等于特定区域最大频率的电容。例如,如果SDRAM端口以 100Hz 运行,则在该区域至少添加一个诺振频率为 100MHz 的电容。对于该区域内的其余电容,选择可能的最高谐振频率值。

这种解析解耦方法为设计人员提供了一个良好的起点。如前所述,设计人员需要优化去想电容,以确保电路板特性过程中的低噪声和低 EMI。以下示例显示了如何将此过程应用于典型设计。

3.3 分析案例

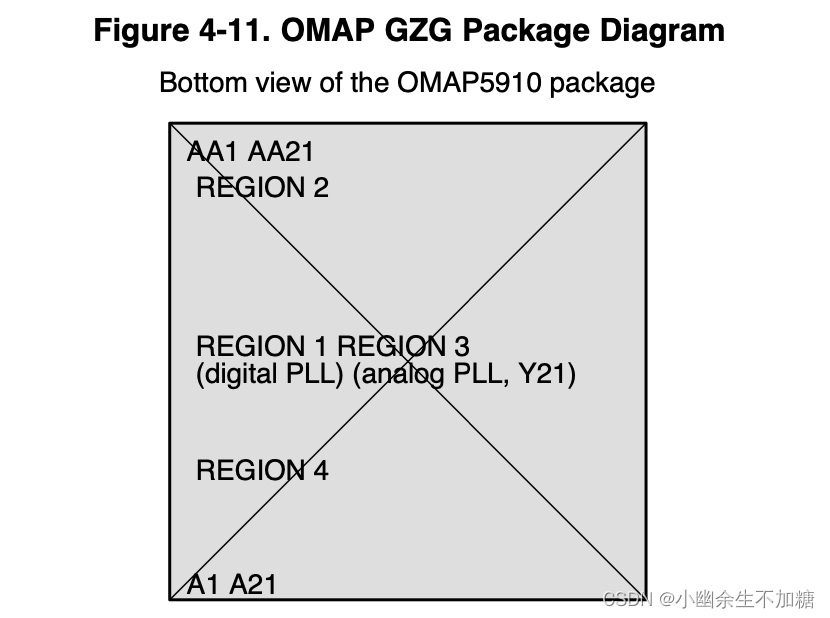

通过在器件上画两条对称线,将OMAP5910 289引脚GZG 封装分成四个区域。然后计算每个区域中核心电压引脚、I/0 电压引脚和信号的数量,不包括接地引脚。此外,要特别注意外部存储器接口 fast (PJIFD)、锁相环(PLL)和其他高速串行/并行端口等关键部分。假设所有 io 都是驱动 60 欧姆传输线的输出。

区域1:3 个内核电压引脚、8个1/0 电压引脚和54 个输入/输出引脚。

区域2:3 个内核电压引脚、4个1/0 电压引脚和59 个输入/输出引脚。

区域3:3个内核电压引脚、3个 I/0电压引脚和59 个输入/输出引脚。

区域 4:4个内核电压引脚、6个 I/0 电压引脚和55 个输入/输出引脚下一步是保守估计每个区域的开关电流要求。

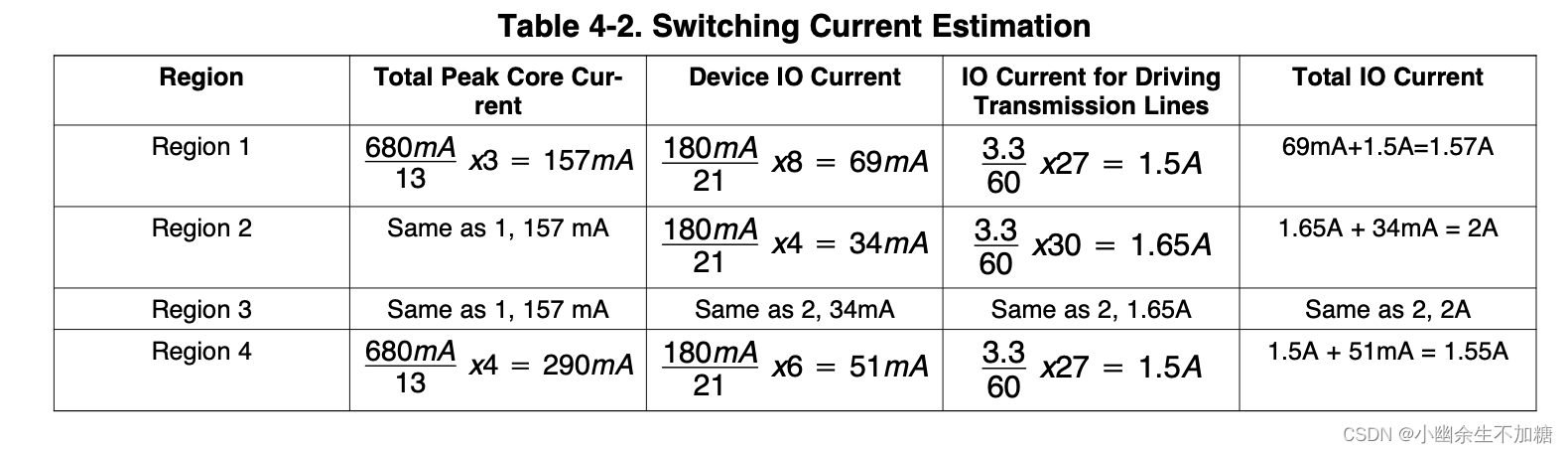

Table 4-2 显示了所有四个区域的开关电流计算。用于计算上电容的保守假设Table 4-1 是:最大核心电流=典型电流x2加上100%裕量= 170mA x2 x2 = 680mA。器件10电流=典型I0电流x 2加上100%裕量= 45mA x2x2=180mA。假设该区域一半的输入和输出同时切换驱动 60 欧姆的传输线。这是一个非常保守的假设,因为该地区的许多信号太慢,不能被视为传输线。

3.4 计算去耦电容值

由于内核和1/0电压在不同频率下工作,因此需要单独进行去祸计算。下面给出了为内核和1/0电源计算和选择去耦电容所需的步骤。

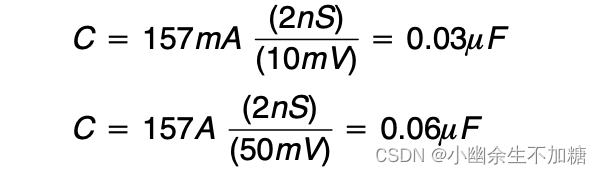

要计算去耦电容,将峰值电流、上升时间和最大纹波电压参数代入下式,求解 c,可以假设内核的最大纹波电压为 10mV,IO 的最大纹波电压为50mV,典型上升时间为 2nS。

使用下面公式计算IO电压去耦的总电容:

现在让我们计算每个区域所需的总电容区域1:总核心电容,

有三个内核电压引脚以 150Mllz (CPU频率)工作,8个I/0 电压引脚以 40Mlz(EMIFS 频率)工作。希望对多个电源引脚使用多个电容,但由于器件周围可用空间有限,因此存在物理限制。对于 0MAP5910GZG 封装,每个区域有足够的电路板空间放置大约4或5个电容。这种情况下,选择两个总电容约为0.03uF的电容,其中至少一个电容应具有约 150Mz 的自谐振频率,以便对区域1中的内核电压引脚去和。然后,选择总电容约为0.06F的三个电容,其中至少一个电容的自谐振频率约为75Mz,以去祸区域1中的1/0电压引脚。

总之,对于区域1中的核心电压,使用两个0.022uF(总计0.044uF)陶瓷电突,对于I/0电压,使用三个0.022uF(总计 0.066uF)陶瓷电容。

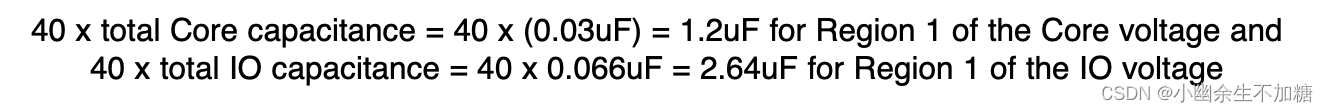

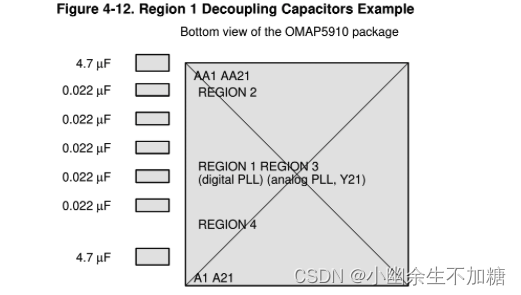

下一步是计算内核和10的大容量电容。大容量电容布局不如去耦电容布局重要。但是需要大容量电容器来过滤通常由开关电源产生的低频纹波,并对去耦电容器进行再充电。经验法则是选择总去翘电容至少十倍的大电容。让我们用40 倍来保守。对于核心电压,

如本文前面所述,最佳技术是在 OMAP 的4个区域添加4个大容量电容,可用的最小钮电容为4.7uF。在这种情况下,为区域1的 10和内核电压选择4.7F 钮电容。

总而言之,Figure 4-12 显示了OMAP5910 DSP夫超区1的完整原理图。如果愿意,设计人员可以对DSP的其它区域重复计算。

3.5 高频噪声隔离

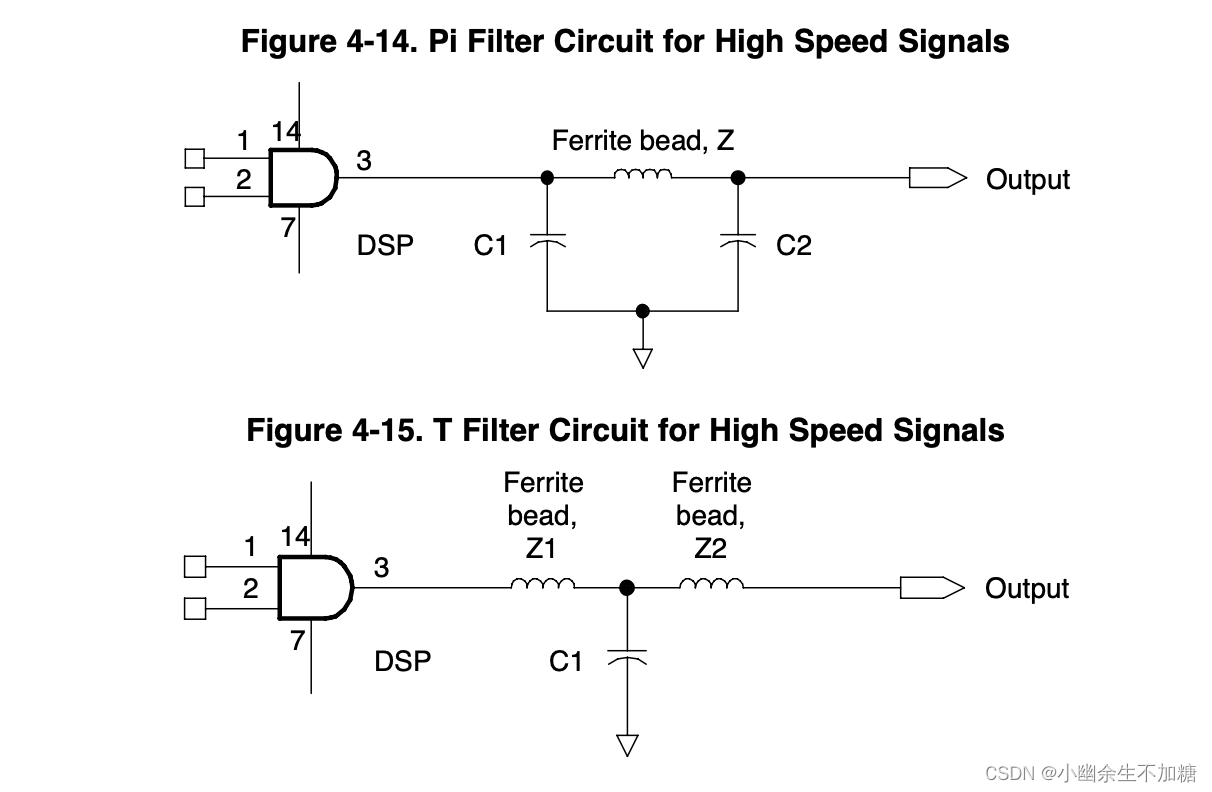

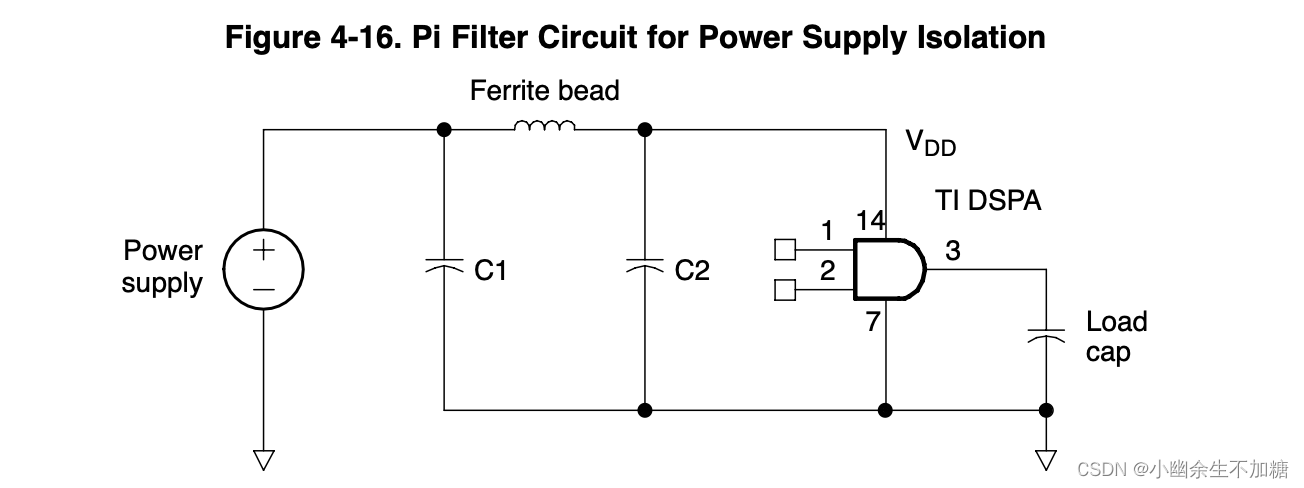

到目前为止所描述的去耦方法在DSP 本地过滤噪声。有些情况下,某些关键部分的整个电源层需要隔离。这可能是为了防止外部噪声进入这些部分,或者防止振荡器等高噪声电路辐射到电源层。电源层通常使用Pi或T涉波器进行隔离。Pi 滤波器由两个电容和一个铁氧休磁珠构成,而T滤波器需要一个电容和两个铁氧体磁珠。这些涉波器通常与进出系统或电源的信号串联使用,以降低辐射发射。必须精确计算滤波器的通带,以确保带宽足够宽,能够通过所需信号,而不会降低信号质量,尤其是上升和下降时间以及幅度等关键参数。

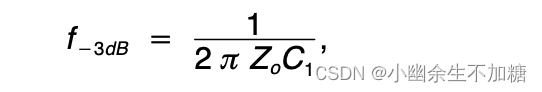

滤波器带宽计算如下:

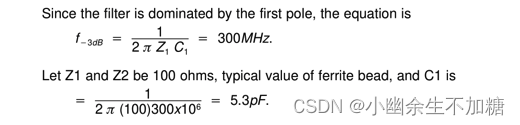

对于Pi 过滤器Figure 4-14从DSP输出开始,第一个并联分量是C1,第二个串联分量是Z,第三个并联分量是C2。因此,该浅波器的带宽由DSP输出阻抗、C1、铁氧体磁珠和C2形成的两个极点决定。滤波器的第个 -3dB转折频率为

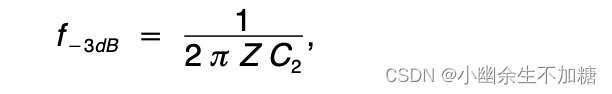

其中,Zo是DSP 的输出阻抗。滤波器的第二个-3dB 转折频率为:

其中乙是铁氧体磁珠的阻抗。

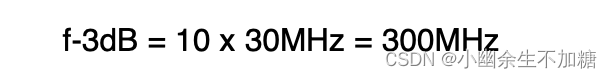

设计滤波器时,始终让C1等于C2,并且只计算第二个-3dB转折频率。这是因为DSP 的输出阻抗非常小,使得第一转折频率足够大,对信号带宽没有影响。我们到底为什么需要 C1? 答案是,当外部信号源耦合回DSP时,CL 成为一·个重要的元件。这种情况下,由C1 和铁氧体磁珠组成的第一极起主导作用,有助于消除F 噪声。设计这种涉波器的另一个经验法则是使滤波器的-3dB 转折频率至少为信号带宽的10倍。

Pi 滤波器设计示例:

让我们为图形控制器用来驱动显示器的红、绿、蓝(RGB)模拟信号输出设计一个Pi 滤波器。假设RGB 信号的带宽为30Mz,滤波器元件计算如下:

下一个大于5.3pF 的电容是 10pF,因此 C1和C2 电容都选择为 10pF。将这些组件尽可能靠近 RGB连接器这可以阻止耦合到信号走线的任何 F 能量向外辐射,同时防止噪声进入DSP 系统。

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】凌霞软件回馈社区,博客园 & 1Panel & Halo 联合会员上线

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】博客园社区专享云产品让利特惠,阿里云新客6.5折上折

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· CSnakes vs Python.NET:高效嵌入与灵活互通的跨语言方案对比

· 【.NET】调用本地 Deepseek 模型

· Plotly.NET 一个为 .NET 打造的强大开源交互式图表库

· 上周热点回顾(2.17-2.23)

· 如何使用 Uni-app 实现视频聊天(源码,支持安卓、iOS)