EMC学习笔记(二十三)降低EMI的PCB设计指南(三)

tips:资料主要来自网络,仅供学习使用。

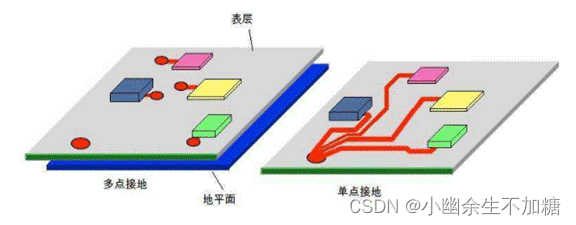

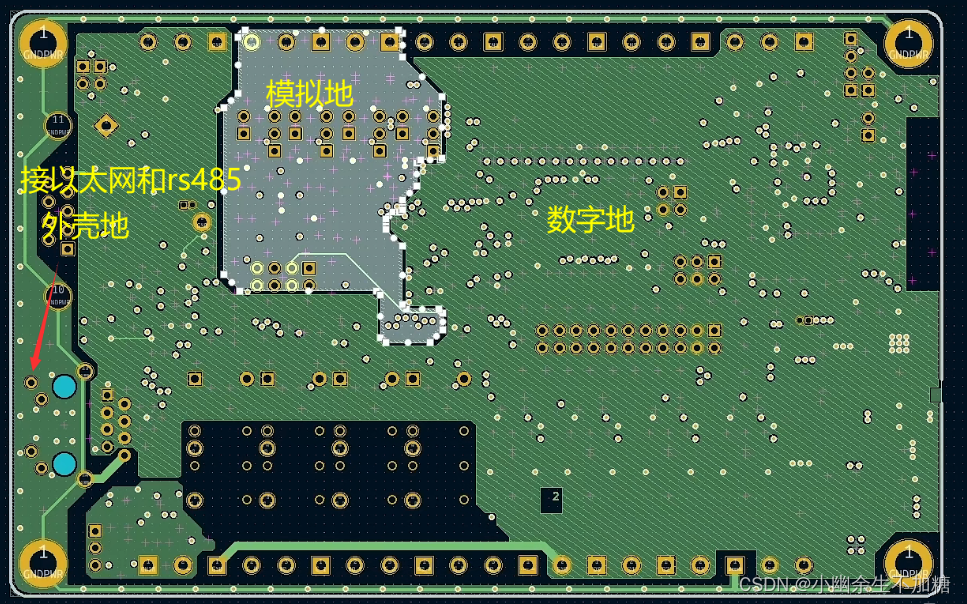

1.单点与多点分布

在一个真正的单点配电系统中,每个有源元件都有自己独立的电源和地,这些迹线将保持独立,直到它们在一个单一的参考点相遇。在多点系统中,连接是以菊花链的方式进行的,因此有多个0-V参考点。很明显,多点系统具有公共阻抗耦合的潜力。虽然实现一个单点系统可能是不可能的,但是对于产生射频的设备来说,单点和多点的组合可以减少噪声。最好的方案可能有一个单一的点,将稳压器接地,微机接地,电池负极,机箱或屏蔽(见图)。

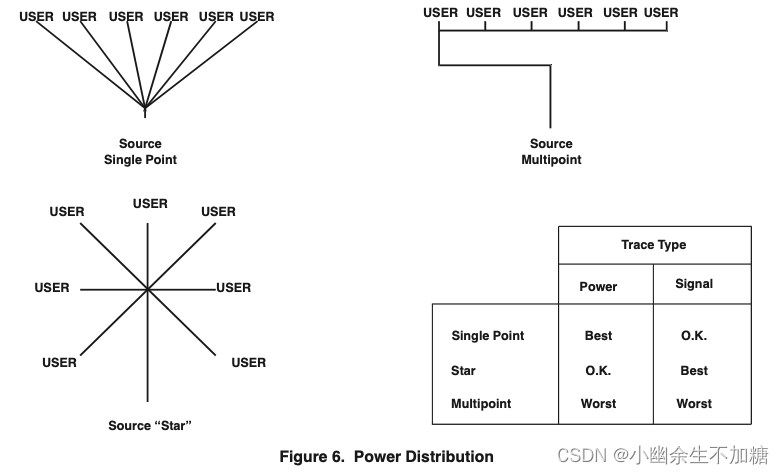

2.星型分布

星型分布很像单点。它看起来像所有的点参考相同的固定点,这是位于中心,由大约相同长度的痕迹。另外相同参考点可以经由大的单个迹线附接到其不位于中心的源。因此,单点的主要区别是:

星型分布的单一参考点可以是一条更长的轨迹,而不是一个点单独的迹线开始的点靠近板的中心,每个迹线都有自己的方向,其结果迹线长度等于所有其他迹线的长度。

星型分布最好应用于高速计算机板上的系统时钟之类的东西。信号从边缘连接器发出,并继续到电路板的中心,然后在那里分裂并前往需要它的每个地方。因为它实际上是从电路板的中心发出的,所以信号从电路板的一个区域到另一个区域的延迟是最小的。

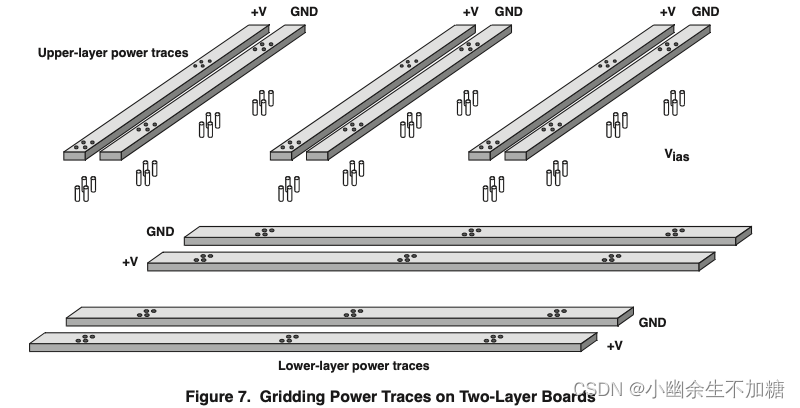

3.创建网格平面

网格化是双层板最关键的设计技术。很像一个电力公用电网,网格化是一个网络之间的正交连接的痕迹进行地面它有效地创建了一个接地平面,提供了与四层电路板相同的降噪效果。

有两个目的:

通过在每个信号迹线下提供接地回路来模拟四层板的接地平面;

降低微处理器和电源之间的阻抗;

网格化是通过扩展任何接地迹线和使用接地填充图案来创建跨PCB的接地连接网络来完成的。

例如PCB上的大多数走线都是垂直的,而大多数走线都是水平的(见图7)。这已经不利于返回直接在信号下运行。首先,扩展每个接地线以尽可能多地填满空PCB空间。然后,所有剩余的空间都被地面填满。在顶面迹线与底面迹线交叉的地方放置通孔。然后对地面填充模式执行相同操作。如果地面填充图案两端都与地面相连,则它们对网格的贡献会更大。仅连接在一个点上的接地填充图案几何结构只是接地屏蔽,但如果连接在两个或多个点上,它就成为导体,因此成为电网中的贡献者。

网格尽可能地在两层板上。寻找布局中的小变化将允许在网格中建立另一个连接的地方。

使用尽可能多的通孔,可以物理适合。

线条不必是正交的,也不必是相同宽度的。

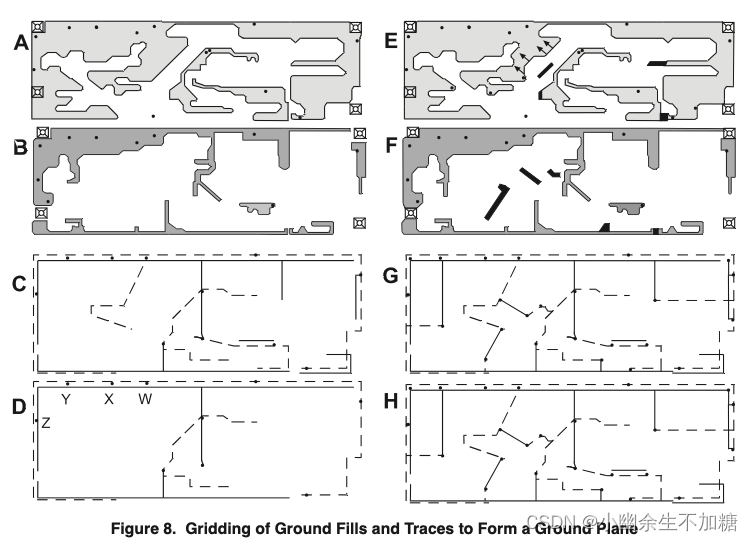

仅对地面进行网格化以实现接地平面的效果的示例如图所示。请注意,为了实现这一点所做的更改是很小的,这表明了一个小的改变可以有很大的改善。

在图中的示例中,A和B分别表示一个简单的双层板的顶边和底边。+V网络的走线和所有互连线已被删除,只留下地面填充和地线,以及前后之间的过孔。图8C是电路板接地布线的简单棒图。每个棒或腿代表接地导体的路径,就好像导体被缩小到最小宽度的迹线。顶部迹线由虚线表示,底部迹线由实线表示。在这张图中很容易看出,大多数的痕迹都是死胡同。大多数迹线仅在一端连接。在图8D中,大部分单端迹线已被移除。其结果是一个稀疏连接的图案,代表了整个电路板上的接地是如何布线的。不包括图8D中的点W、x、Y和Z,在布线上的任意两个点之间只有一条路径。

在图8E、8F、8G和8H中,设计被稍微修改,以实现网格化地面。在图8E和8F中,添加了一些以纯黑色显示的迹线,并稍微移动了一些几何图形(如箭头所示),从而创建了一个广泛的互连网络,从而创建了所需的网格。如

图8G中的接地棒图所示。关闭安装孔周围的间隙也有助于网络。不再是只在一端连接整个轨迹。 现在,它们在两端连接起来,形成一个更完整的导体。图8H显示了网格的密度,与图8D的开放性形成对比。另外,请注意,在图8H中,没有丢弃任何迹线,因为它们只在一端连接。只有一个迹线有此问题,并且它是已在其他三个位置连接的几何图形的一部分。这个相互连接的网络是网格化地面的目标。其结果几乎与实际的地平面一样有效。

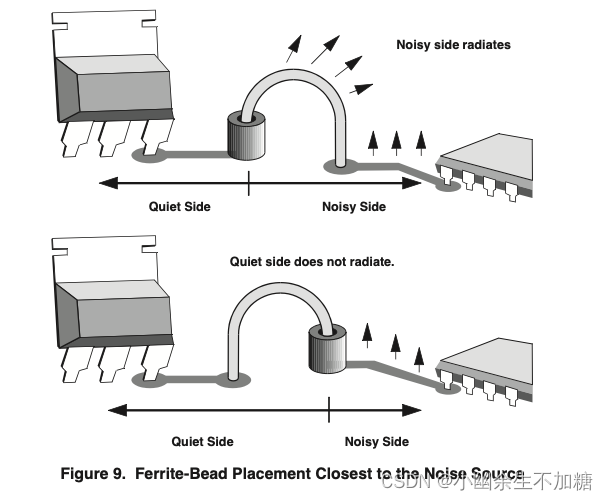

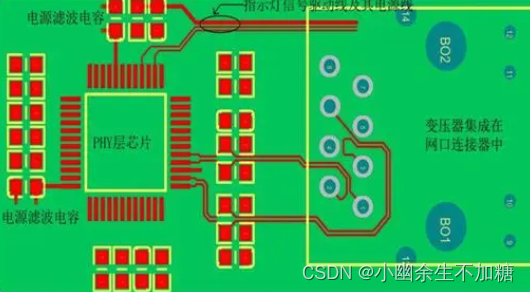

4.旁路和磁珠

在处理器上,+V和地之间的旁路是至关重要的,因为其目的是让电容提供用于开关设备的电流。如果在旁路回路中由于电感过大而无法获得电流,则物理定律认为电流应该达到最低阻抗,这是由连接电源的导线产生的。功率路由的分布电容成为较高频率的来源。这样,铁氧体磁珠就阻断了电源线的射频电流,迫使微处理器利用铁氧体磁珠内部的电流。

最重要的是要认识到,并且永远记住,电源布线的目的只是为了补充旁路电容器中的电荷,而旁路电容器应该提供振荡器频率或以上的所有电流。使用以下措施可以实现射频远离功率分布布线(见图)

使用α铁氧体磁珠或0.1μF、0.01μF电容)。在铁氧体磁珠外放一个1000 pF的电容器,创建一个pi滤波器。这个电容器的接地应该是微接地。然而,如果在这一点上有很多噪声,电容器可以将这些噪声耦合回+V线;

铁氧体磁珠只能在+V上使用,不能在地面上使用。如果使用通孔铁氧体磁珠,则安装时外露引线连接到+V;

对旁路回路中的迹线应用3:1的长宽比规则,以最小化高频路径中的阻抗。

使旁路循环的面积和长度尽可能小。当为振荡器或+V电源连接旁路电容器时,尽量延长微处理器接地,而不要进行跟踪;

尝试运行任何跟踪回(或下)循环的任何其他部分,以减少辐射面积时,从董事会的顶部看;

在四层板上使用铁氧体磁珠和相同的旁路值是可以接受的,也是有益的;

在四层板上可能不需要1000pF的电容,但在最初的设计中应该画出来,如果屏幕室测试表明它是不需要的,那么稍后就删除它;

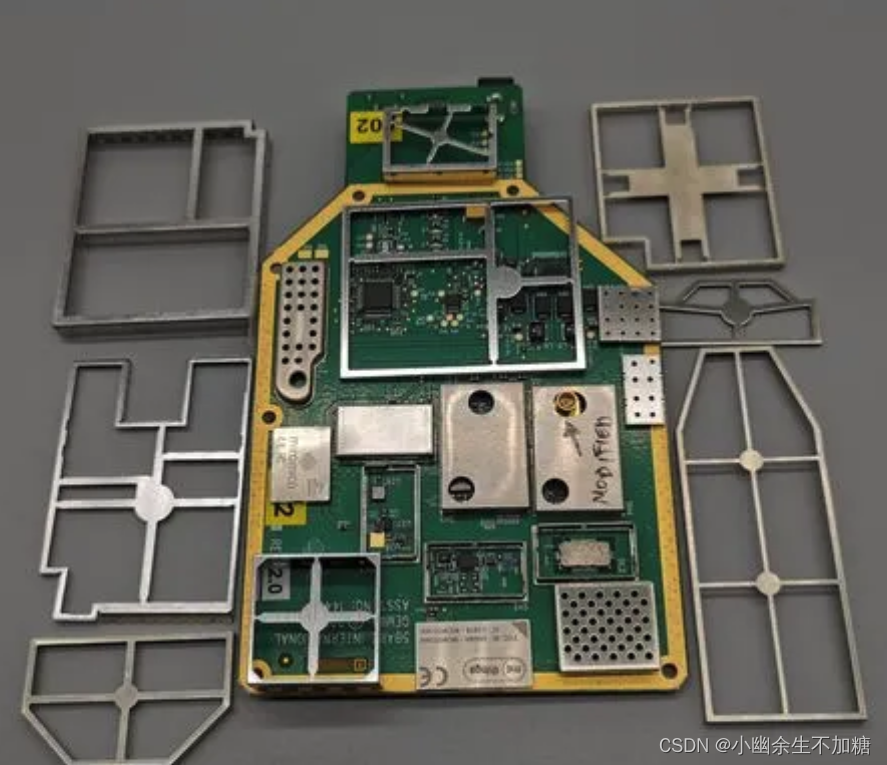

5.将噪声保持在芯片附近

以下内容适用于用于简单数字I/0的引脚,而不适用于用于内存扩展总线的引脚。这里的目标不是减少开关切换的噪声,而是当引脚是静态时,减弱时钟信号的噪声。

引脚上的噪声通过许多路径耦合到设备内部,可以随着引脚功能的变化而变化。例如,键盘扫描中的输入引脚具有来自衬底和电源轨的电容耦合噪声。而且,它可以是高阻抗,任何环境场有效地耦当按下按键时,引脚有一组新的噪声源,因为信号线的阻抗发生了变化。因此,很难有效地制台。定一个包含所有可能性的矩阵;因此,建议如下:

在每个输出引脚上串联一个50-100R电阻,在每个输入引脚上串联一个35 -50R电阻。如果系统设计需要更高的串联电阻,则使用该值。更高的电阻是更好的输出,但通常不会改善输入的特性。将电阻器尽可能靠近微处理器,如果可能的话,与微处理器接地重叠。

如果信号线所需的边沿速率不快于100 ns,则使用1000 pF电容器将微计算机上的任何引脚旁路到地。在输出和引脚,该系统用于输入和输出,地为电容器应微机地。电容器的另一端应连接到串联电阻的接收端,而不是微机端。将电容器放在电阻器内部会使微型计算机看到的负载在切换时看起来像短路,这是不可取的。 如果必须在增加电容器和放置串联电阻之间进行权衡,由于空间限制,只放置电阻器即可。

在引脚只用于输入,放置电容器内,在微机一侧,电阻器,以减少回路面积。然后,在引脚上的微型计算机中产生的高频通过电容比通过电阻看到更少的对地阻抗。

复位和中断是特殊的功能,因此必须注意不要减少功能。

不适用于任何上述补救措施振荡器引脚。如果振荡器组件之间的适当间距和保持其他不相关的组件和迹线,不应需要振荡器信号调理。未使用的引脚应配置为输入,并直接连接到微机接地。建议启用看门狗以纠正不太可能发生的事件,其中设备受到干扰,失去其程序计数器,并执行代码,使输入成为具有高电平的输出。

这些规则占用了空间并添加了器件,因此在生产中没有得到很好的接受。目标是在所有I/0引脚上实现所有规则但是如果这是不可能的,那么对最不可能引起噪音的候选人进行排序,删除这些规则的应用。

从最需要到最不需要滤波的优先级有:

离开外壳的信号;

信号离开PCB到外壳内的其他电路板;

信号停留在具有高阻抗负载的PCB上(即驱动另一个MOS输入或开路);

并行I/0端口的引脚设计用于支持高速数据传输,例如,在微型计算机和外部存储器之间,需要对剩余的I/0引脚进行滤波,因为它们的上升和下降时间更快。当设计完成并制造出第一个原型时,在屏幕室中用一到两个小时,一次移除一个滤波元件,以确定哪些是需要的,哪些是不需要的,以获得所需的EMI水平。

浙公网安备 33010602011771号

浙公网安备 33010602011771号