EMC学习笔记(二十五)降低EMI的PCB设计指南(五)

tips:资料主要来自网络,仅供学习使用。

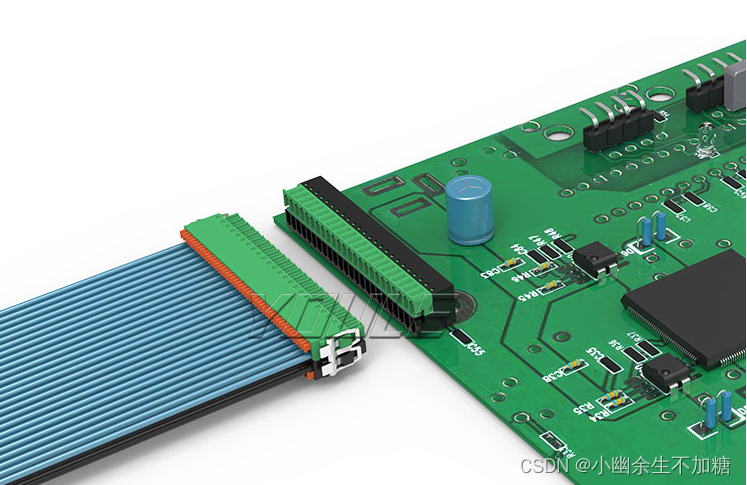

设计良好的两层板,和大多数四层板,有最小的辐射。系统级的问题是由于将PCB与任何板外支持功能、其他处理器或显示器和键盘PCB互连的电缆产生的辐射。

因为通常在板之间只有一个地线,所以一个感应线必须返回由其他线携带到第二PCB上的所有RF能量。如果有任何阴抗在单一的地线射频能量的一部分不返回到微机的PCB通过地线,而是通过一个辐射路径。

能量辐射出第二板并耦合回第一块板,"但是,在此过程中,该辐射也会在系统中的其他位置添加噪声,以及成为在屏幕室测量的直接辐射。关键的纠正措施是确保回路的传导路径具有非常低的射频阻抗。

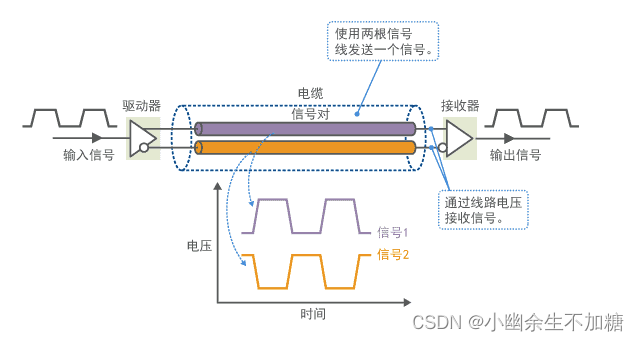

1 差模和共模噪声

共模噪声是电缆中的一个大问题,但故障不在于电缆,而在于电路板上的连接,信号和返回连接到电路板上,形成公共阻抗。共模噪声可以在源端通过减小公共节点的阻抗来校正,或者通过在整个电缆周围放置铁氧体磁珠来减小。

差模噪声(边缘过渡的有用噪声)应首先减少到最大(最慢)允许的上升和下降时间,并应只发生在所需的最低频率。辐射出的噪声是由于信号的环路及其回波引起的。通过尽可能多的返回,并通过扭曲每个信号和返回对,这个循环被最小化。后者在一定距离处引起场抵消,其方式与地面上的路由功率相同。

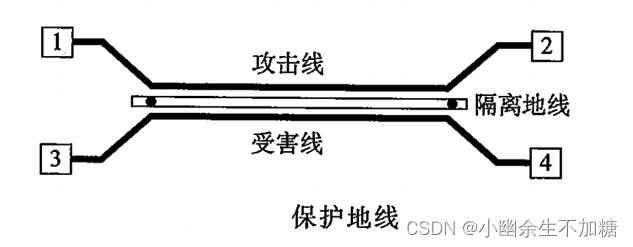

2 串扰

电缆中的串扰与PCB中的串扰相同。噪声从源耦合到安静的受害者信号。因此,运行时钟或其他高速纹合导线各自独立返回。串扰在2米长的电缆中是一个问题,在短至6英寸的电缆中也是一个问题。

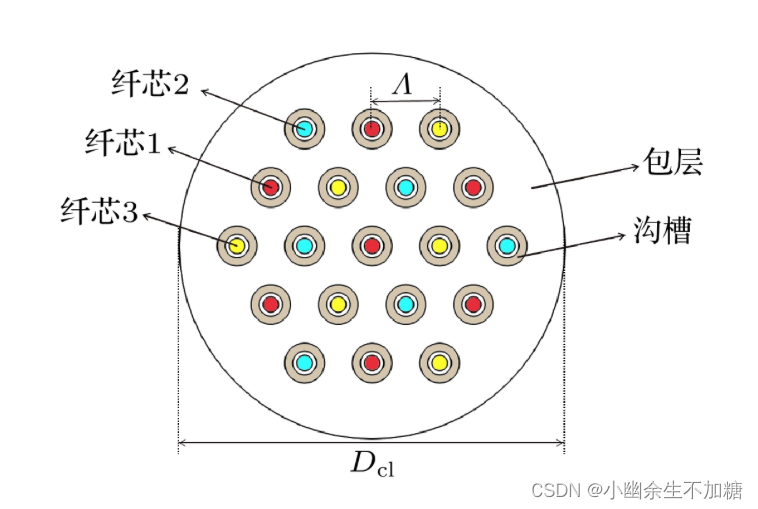

3 返回路径数量

在计算机行业中,电缆或线束中每九条信号线至少有一条接地线是常见的做法。随着更高的速度,这一比例正在向1:!5的方向发展。这些更高的速度不仅限于数据速率,还包括谐波含量。在设计信号线和回传线时,请使用以下准则:

最好的做法是为电缆中的每个信号设置一个接地回线,作为双绞线。

即使是在完全密封的金属盒中连接到前面板显示器的跨接电缆,也不要每九条信号线少于一条接地回路。

如果电缆超过一英尺长,它应该有一个接地返回线的四个信号线。

如果可能的话,应该有一个坚固的金属支架,用作机械支撑,焊接在两个板之间,作为安装支架和坚固的RF接地回路。

4 外部PCB -IO 布局建议

PCB应该有一个大的接地面积,连接到外壳的屏蔽层,作为进入或离开外壳的每一条线上的旁路电容器的接地。这些电容器提供了微机噪声的最终过滤,但也旨在过滤屏蔽盒外的电缆上拾取的任何噪声。

5 防止噪音和静电放电

电缆上的噪声和ESD事件将通过PCB上电缆上的旁路电容器并输出到屏蔽层(机箱)。因此,从电容器到屏蔽层的接地应该很宽(3:1),并且最好用两个或更多的螺丝固定在屏蔽层上。旁路电容值应小于1000 pF,所以有效的串联电阻(ESR)是在50-500兆赫范围内最低。轴向器件的引线长度将是ESR的一个因素,因此表面贴装元件是首选。

浙公网安备 33010602011771号

浙公网安备 33010602011771号