uvm设计分析——reg

项目中的reg_model一般只有一份,set到reg_sequence上,所以多个sequence并行启动结束的时候,reg model会成为一个共享资源。

uvm_reg_field中的volatile,主要来设置m_check的变量,

m_check,主要用在uvm_reg的mirror task,以及read task,(需要map中配置check_on_read)

uvm_reg_field中的desired,mirrored,m_parent,m_access变量都是local的,继承类中完全看不到,只能

通过function来得到数据。

m_access,指定field的access policy。

m_written,指定是否是只能被写入一次的。

reset可以被设置为多种类型的reset的值。

主要function configure。

uvm_reg中的主要变量有,m_locked,由顶层的reg_block调用

m_parent,指向的uvm_reg_block;

m_is_busy,当该reg正在执行frontdoor的读写操作时,该信号置 1,避免此时做predict。

m_backdoor,外部设置进去的backdoor的方法。

m_maps[uvm_reg_map],该reg挂载在的map的对象,在default_map,add_reg时,指定。

hdl_pool,以string为索引,uvm_queue为对象,string方便指定RTL,Gate等不同的hdl。

coverage收集信息,m_has_cover,m_cover_on。has_cover表示reg new的时候加入的coverage选项,

cover_on表示当前设置的coverage。主要区别在调用时候,需要的是哪一种的coverage。

reg new的时候,需要设置的是has_cover,new的时候,直接build_coverage。需要顶层调用include_coverage。

reg_block在new的时候,可以设置cover_on,通过set_coverage等function。sample的时候get_coverage。

reg的读写前后都有pre/post的hook task。

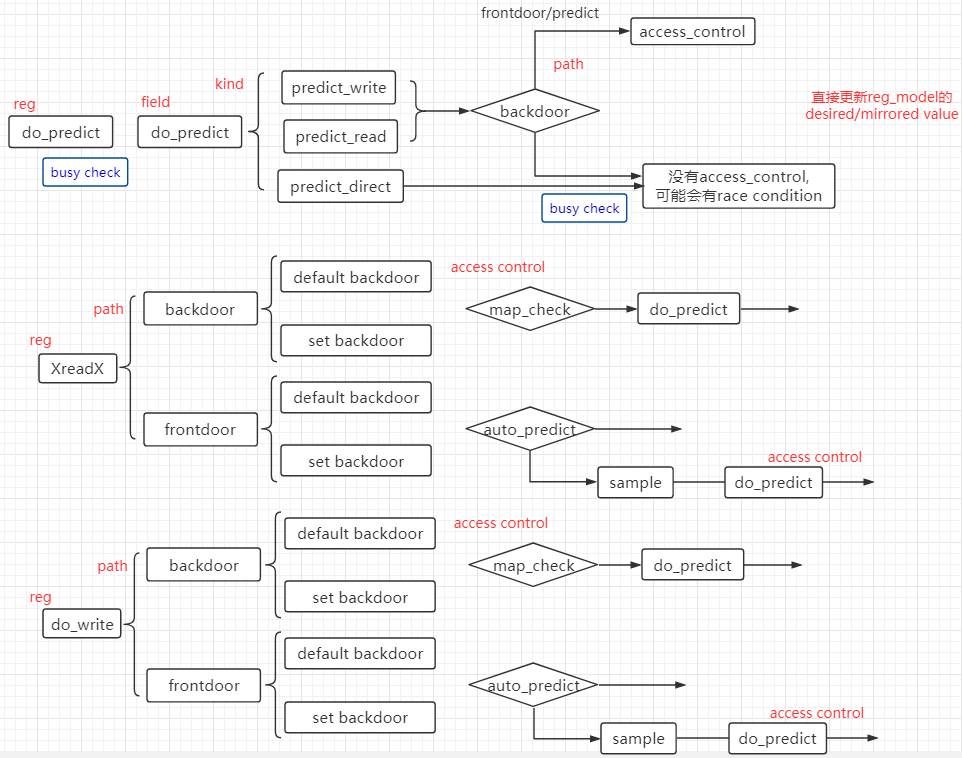

uvm_reg中最重要的三个task:

read,write,根据path的不同,操作总线或者更新reg_model;内部都是都access control的,只不过backdoor的在自己内部,其他的在predict中。

predict,只是更新reg_model,是一定不会操作总线的。对backdoor和kind为predict_direct的,没有access control。

predict的kind有四种,predict_write,predict_read,predict_direct,predict

mirror,read操作加一个check函数,所以也会调用predict函数,更新reg model。

path有两种,frontdoor和backdoor。

所有的frontdoor的操作,根据map_info中的fd信息,启动sequence或者调用map的读写操作。

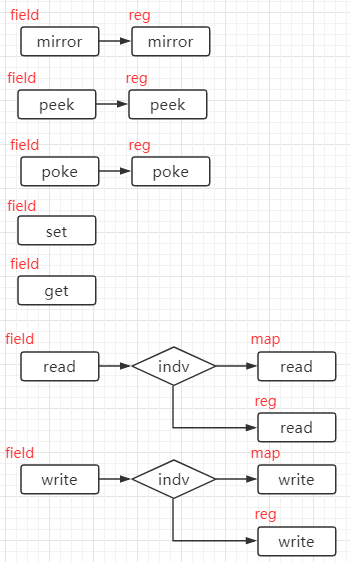

其他控制model值的task调用关系:

update的时候,write的值是根据regmodel目前的值,来写进去的,也就是set field的值,write函数其实只是写入改变了的field。

所有的field都没有更新时,是不会进行update操作的。

update直接更新reg model内的值,需要检测此时没有reg model的frontdoor操作等,即not_busy。

在reg_field中的task中,基本都调用uvm_reg的task,但是read、write根据是否支持individual可能会调用map中的task。

uvm_reg中还有一些hdl_path的function,add_hdl_path_slice,添加到field的path路径。这些路径,之后在map中会被集成起来。

形成一个full_name。

uvm_reg_frontdoor,从uvm_reg_sequence继承而来,本身是一个sequence。

uvm_reg_backdoor,从uvm_object继承而来,本身就是一个object,其中定义了read、write的原型函数。

uvm_reg_map,auto-predict的设置,影响所有的读写操作,自动更新mirror和desired value。

只影响frontdoor,backdoor都是直接调用do_predict函数的。

m_regs_info,所有add到该map中的寄存器的信息,包括access,offset,addr,

m_check_read,影响所有的read操作,mirror操作,mirror value和读到的值做比较。

m_adapter,m_sequencer,做frontdoor的read和write操作。

m_base_addr,该map的基地址。

m_regs_info,每个加到该map中的寄存器,所有的信息保存在该数据结构中,

在lock或者add_submap的时候,更新map_info中的addr,调用Function Xinit_address_mapX

定义自己的do_bus_write和do_bus_read,

uvm_reg_block,包含类,包含底层的uvm_reg_block,uvm_reg,

default_path,定义自己的hdl_path,

lock,表明当前的model是lock住的,调用function lock_model()

自己的coverage设置,new的时候设置到has_cover,get的时候,得到cover_on。

uvm_reg_sequence,只是实现了调用map中的读写操作,不支持burst_read,burst_write,

其中启动该sequence,需要reg_sequencer,连接一个driver。

或者在sequence中,直接调用已经存在的read,write task,这样配置的sequence,可以直接由此继承。

uvm_reg_item,uvm_sequence中的trnasaction类型,定义reg access的方式,包含一个uvm_object类型的extension,可以自定义。

在读写时,方式与adapter交互。

uvm_reg_adapter,继承自uvm_object,从其中设置一个uvm_reg_item,需要实现两个function,bus2reg和reg2bus。

其中的变量supports_byte_enable, 影响sequence的个数。provides_reponses,影响sequencer和driver之间的交互。

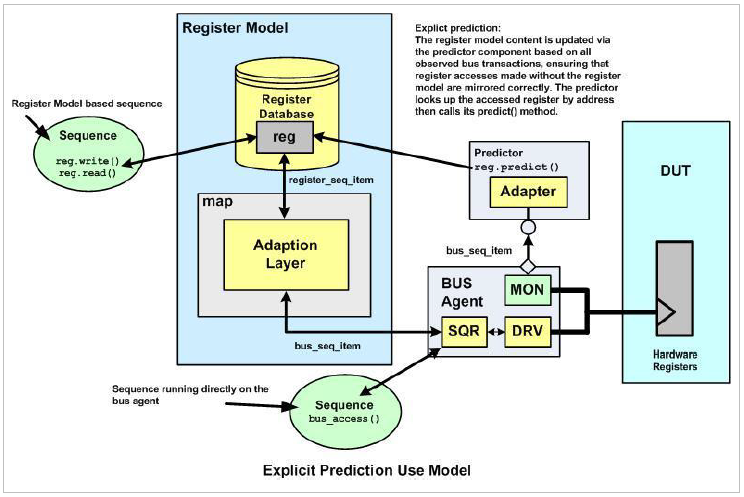

uvm_reg_predictor,当auto_predict关闭的时候,需要例化的component,连接到寄存器的monitor。

在write函数中显示调用do_predict函数,更新model中的mirror value,此时do_check函数,会根据read_on_check进行调用。

uvm自建的针对reg的sequence,针对普通的reg有:reg_access_seq,reg_bit_bash_seq,reg_hw_reset_seq。

uvm_reg model,主要实现了

1) 增加了对dut的reg进行访问的方式,可以直接通过reg model进行访问。传统的只能是通过sequence,启动在bus的sequencer上来实现。

2) 方便了对dut reg进行测试的方法,通过build-in sequence来实现。

3) 方便检测每次的bus读写的正确性,通过reg_predictor的方式来实现。

reg prediction的方式有三种,

1) auto_predict,直接通过设置map的auto_predict选项,通过reg model的sequence,reg model都被正确的赋值,

2) explict_predict,即设置map的auto_predict选项,有增加component,reg_predict。这样不论sequence是由reg model启动

还是bus agent启动,不论front door,还是back door,reg model的值都是正确的。

3) passive predict,只有一个reg predict,对back door访问不敏感。

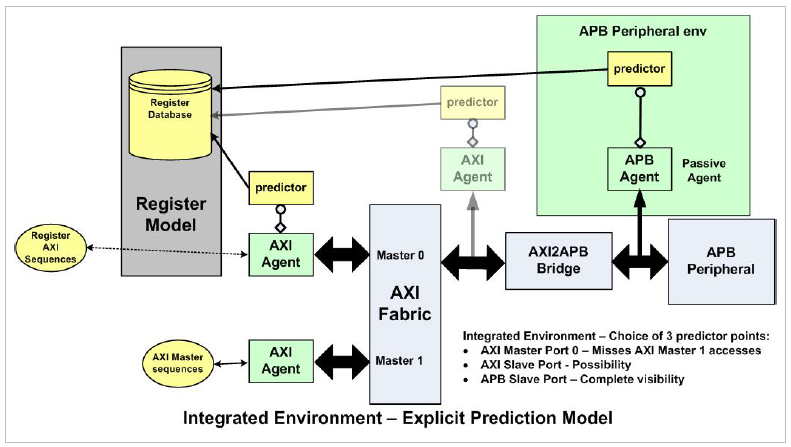

reg model的集成:

1) 每个subenv集成一个predictor,

2) 每个reg_predictor初始化内部的reg_model,reg_adaptor,analysis port

3) 每个subenv的sequence中,包括对用的reg_model的指针,

4) 顶层的reg_map,初始化agent和sequencer,

reg model的coverage设置,

1) include_coverage,是一个全局性的coverage开关的设置,

2) build_coverage,一般是在configure的时候,初始化model中的变量的函数。

3) has_coverage,在new covergroup的时候,进行选择,

4) set_coverage和get_coverage,是在sample的时候,进行选择。

sample方法,在reg的front door访问之后,自动调用。

sample_values方法,主要实现对field value的采样,需要自己调用。

reg_model中的值的check:

1) mirror的task,可以直接对一个reg_block或者reg进行检查。读DUT的值与当前的mirror值相同,则为uvm_is_ok

2) read_on_check的检查,对map进行设置,在读操作的过程中,检查desired的值与当前读到的值相同,则为uvm_is_ok。

reg_model的访问级别:

1) randomize与update,mirror,reset,都可以在reg_block的层级直接调用。

一般可以先对reg_block进行randomize,之后进行update,很多dut的读写操作之后,mirror进行检查。

浙公网安备 33010602011771号

浙公网安备 33010602011771号