cache基础

cache是系统中的一块快速SRAM,价格高,但是访问速度快,可以减少CPU到main memory的latency。

cache中的术语有:

1) Cache hits,表示可以在cache中,查找到相应地址的entry。

2) Cache Miss,表示在cache中,找不到相应地址的entry。

3) Snoop,cache不断监视transaction的地址线,来不间断的检查地址地址是否在cache中。

4) Snarf,从main memory中读出数据,同时更新cache中的旧值,称为Snarf。

5) Dirty Data,cache中的数据,是最新的,但是main memory中的数据还未更新,称cache中的数据为dirty。Stale Data类似。

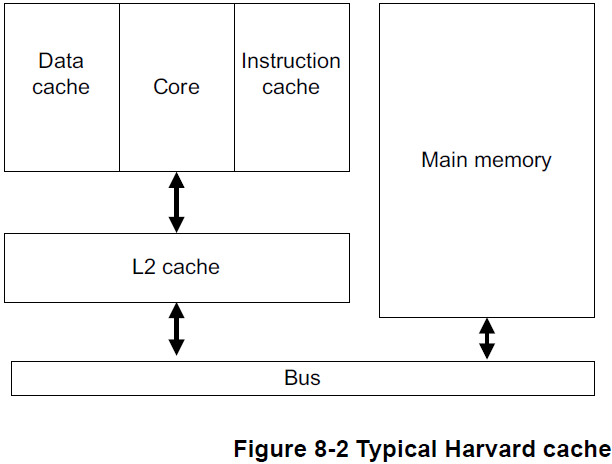

arm架构中的cache架构是harvard结构的,分为data cache和inst cache。

其中L1 cache,一般直接集成到core中,大小多是2-way,4-way,16KB和32KB,cache line一般是32byte或者64byte。

可以实现为VIPT或者PIPT。

L2 cache,可以集成到core中,也可以单独作为一个external block,大小多是8-way以上,256KB,512KB,1M等,cache line也是32byte,64byte。

一般实现为PIPT。

cache的架构,分为read architecture,write policy,allocation policy。

1) read分为,Look Aside和Look Through,

Look Aside,main memory和cache都在同一时间,看到同一bus上的trans。

优点:减少了cache miss下的 memory访问时间,

缺点:在一个core访问main memory时,另一个core不能访问cache。

Look Through,

不管是哪一种的read architecture,cache miss之后,从main memory中得到的value都会被Snarf到cache中。

2) write policy,

write-back时,将数据写到cache中,cache就像一个buffer,在evict一个新的cache entry时,才会将cache写会main memory。

存在cache和main memory的consistency问题。需要进行cache maintenance操作(如cache line置换,mmu page置换修改等),

主要分为cache invalid(舍弃cache中的值,将valid flag置零)和cache update操作(更新main memory的值为cache中的值)。

write-Through时,读写性能要低一些,但是main memory中都是最新的value。不存在cache和main memory的一致性问题。

3) cache miss之后,是否allocate新的entry:

read-allocated;读操作miss之后,先从main memory中读取数据给core,之后在进行cache line snarf。

write-allocated;在write miss之后,需要先进行burst read,进行cache line snarf,之后进行write back操作(一般与write back一起使用)。

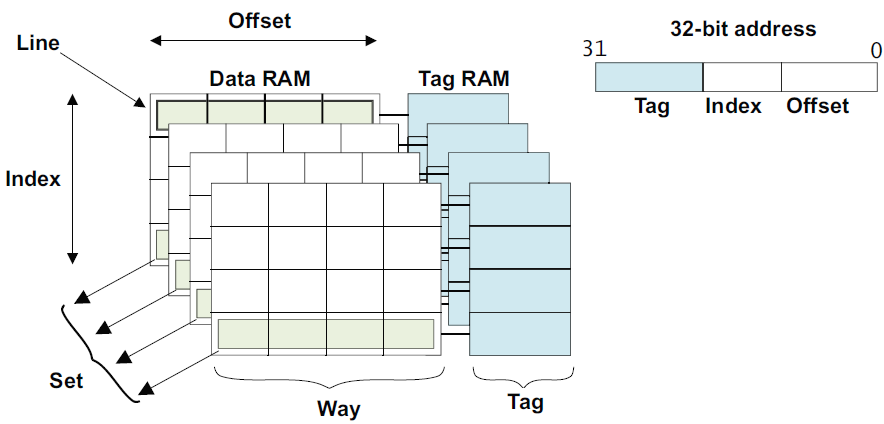

cache block会被分为三个functional blocks,Data RAM,TAG RAM,Cache Controller。每个cache 单元需要保存address,data,status等信息,所以cache真正的大小会比data ram大很多。

1) cache controller也会根据memory request是否是cacheable的来进行cache的寻址操作。

2) tag cache,主要存储VA,PA的地址索引。平时所指的cache size并不包含tag ram的大小。

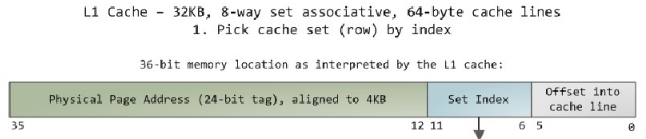

3) offset寻址具体的word,index寻址某一个way,也就是某一个cache line,tag主要做地址校对,最终选择tag匹配的那一个set。

在set-associate结构的cache中,main memory中所有index相同的地址,都只能放在对应的way中。

Cache的organization:

1) Cache Page,main memory中被等大小的分为的piece,称为cache pages。

cache page的大小,不但与总的cache size有关,与cache的organization也有关。

2) Cache line,cache page中更小的单元,cache缓存的最小单位。

cache的组织结构有三种,

1) 分为full-Associative,全相联映射。没有cache page的概念,每个cache line直接对应到随机的某个memory line中。

缺点是,TAG ram会比较大,索引会比较慢,一般应用在cache较小的地方,如tlb或者predict buffer中。

2) Direct-Map,直接映射,也称为1-way associative,main memory分为多个cache page,中的第n line,必须放在cache page的第n行。

复杂度不高,但是,性能很差,常常需要evict其他的cache line,不够灵活。

3) N-way Set-Associative,组映射,比如2-way,4-way等,还有一个Set的概念,表示cache page的行数。

每个组分为N份,N称为cache way。每个cache way内部的映射,就与direct mapping相同,

set到main memory的映射,随意,与full-associative相同。

所以一块main memory,首先随意映射一块地址到set中,然后每个set在平分为几个way,直接查找几个way即可。

way中的line 映射,是一一对应的,不能够随意破坏行的顺序。

2 way的映射图:

在使用N-Ways Set-Associative时,这是一种阵列的表现方式:

一个组里有N行,其实是N个set,但是set中的每一行与main memory分的cache page中的行数是一样的。

cache首先被分为多个Set,S等于1时,也就是1个Set,这时,等同于Direct-Associative。

N等于1时,也就是说1个Way,这时,等同于Full Mapped。

cache的大小等于cache_line_size * way_num * set_num

cache line的结构:

1) data段存放cache line中的数据,大小通常为32byte或64byte,一个bus的wrap操作。

2) status段,存放cache的状态,可以是MOESI等。

3) Tag段,存放部分物理地址信息,可能包含虚拟地址信息,(VA的Cache索引可以与VA的地址转换同时进行)

PA地址的cache索引,最低位是word的寻址,之后是way(cache line)的寻址,再之后才是tag的寻址;

cache hier的问题:在不同的微架构中,L1与L2的关系可以是inclusive的,也可以是exclusive的,

inclusive cache:相同的data可以存放在Both L1和L2中。

exclusive cache:相同的data只能放在L1或者L2中,不能同时存在。

目前一般使用inclusive cache类型,每次cache miss,可以从下一级的cache中寻找,load。而exclusive cache,每次cache miss,只能去main memory中load。

但是exclusive cache比较节省cache size。

浙公网安备 33010602011771号

浙公网安备 33010602011771号