PL301 matrix内部模块

ASIB中的valid信号,有两部分,一部分add产生的地址映射,到main中的default addr。(vect)

一部分由Dmu和Cdas组成,到main中的build。

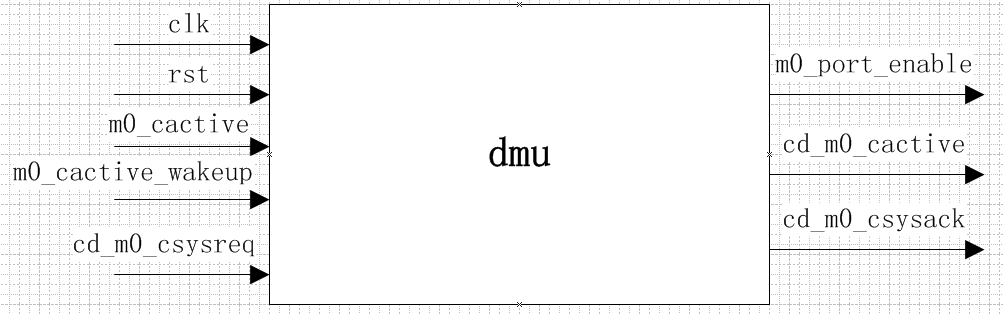

Dmu:interconnect中的power manage unit。

两个输入信号:m0_cactive:来自asib的valid信号和目前的tracker_busy信号,表示目前还有未传完的ourtstanding的transaction。

m0_cactive_wakeup:来自master口的新的transaction的valid信号。

在经过内部的FSM后,输出m0_port_enable信号,cd_m0_csysreq和cd_m0_csysack信号。

内部不会有相应的clock gate逻辑,只是提供握手信号和状态信号。

Asib中:add_decode模块,进行address的remap,包括(security/protect/cache信号的处理),

地址可以分段判断,每一段有自己的security和protect的设置,最终输出几位的valid信号。

传入asib内的其他模块和ib模块中,表示该次transaction有效。读写通道分别例化。每一个address region对应一个slave区域。

Asib中的maskcnt模块:在master端,表示为issue capacity,主要进行计数,产生tracker_busy信号。

读写通过最终的resp的返回来判断是否结束。tracker_busy信号只用在dmu中的wakeup输入端。

内部计数为read/write可接受的outstanding的个数,输出wr_cnt_empty信号来作为outstanding满之后的mask信号。

Asib中的cdas模块:根据连接的slave interface个数和acceptance capability,和相应的cdas策略,

实现对同一master口,发送transaction的控制,防止死锁,较多的策略有single slave和per ID per slave。

其中的asel来自add_decode的valid信号,位宽相同。读写该模块实现并不相同,读通道只输出一个ar_enable信号。

Asib中的register slice模块5个通道可以分别例化,都有四种模块可配置。位置可调整。

Master端的Ib模块中,有upsizer/downsizer模块,

slave端的ib模块中有async bridge和interface conversion bridge。针对cdc,会有5个通道的fifo进行cdc设计。

涉及到upsizer/downsizer时,会有read_address_format,write_address_format,write_control,write_merge_buffer,

write_response_block以及fifo_wr。

cd_main中包括:busmatrix的switch模块,default slave模块,dmu模块,以及master和slave的ib模块。

Switch中包括两部分:Build模块,实现master到slave的1-n转换,实现master发送trans的cdas模块。

Map模块,实现slave端的n-1转换,实现slave按qos或者lru算法的选择trans arb模块。

Build模块中有和master个数相同的blayer模块,每个内部例化rd/wr通道。通过build_rd/build_wr生成的enable信号,使能到各个slave的valid信号。

其中asel信号来自add_decode模块输出的每个slave的valid信号,三个enable信号在此基础上产生,使能到slave端口的valid信号。

Map模块内包括add_sel模块,ret_sel模块,wr_sel模块。

add_sel模块主要实现rd/wr address的arb选择(QOS,LRU),以及outstanding的mask操作。

Ret_sel模块根据id号,选择正确的B通道和R通道到build模块。

Wr_sel模块,实现wdata信号到slave的选择,直到address的arbitrated做好,否则stall wdata channel。

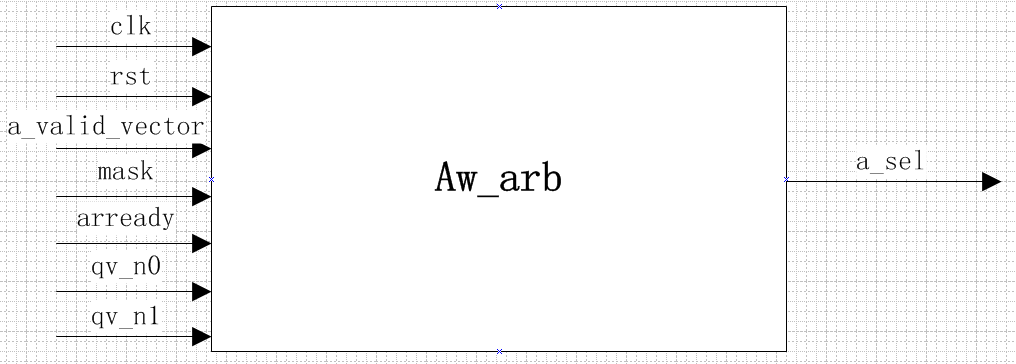

Add_sel模块内包含三个模块:ar_arb模块,aw_arb模块,maskcnt1模块。Maskcntl模块。

这里的maskcntl模块,输出mask_w/mask_r给arb模块,在outstanding的个数到之后,进行mask操作。

Arb模块,通过qos或者LRG算法,从选择从不同master过来的transaction。内部实现highest_qos和lrg_arb两个模块。

Mask信号从maskcntl模块来,a_valid_vector为信号add_decode输出的valid信号与master的valid信号的与结果。

浙公网安备 33010602011771号

浙公网安备 33010602011771号