clock

Prime Time中的clock分析包括:

1)Multiple clocks,clock from port/pin,virtual clock。

2)Clock network delay and skew,clock latency----delay of the clock network relative to the source。

clock skew-----variation of arrival time of clock at destination point。

3)Gated clock,perform both setup and hold check on the gating signal。

4)Generated clocks,such as clock divider or PLL。

5)Clock transition times,specify the transition times of clock signals。

create_clock -period 10 -waveform {2 4} [get_ports A]

clock的source可以是port A,net N或者FF的pin Q。不指定source时,表示virtual clock。

-name 对该clcok的命名,不添加时,由clock的source名代替。

-add 在同一source上定义两个clock,create_clock -period 20 -waveform {1 3} [get_ports A] -add。

-waveform [a1 a2]第一个值表示第一个上升沿,第一个值表示第一个下降沿。

-source 一般加get_pins/get_ports等,表示一个端口或门电路接口。

-master_clock 一般是一个clock name,来自create_clock或create_generate_clock等命令。

也可以是get_ports命令,可以和-source的变量一致。

get_clocks -filter "period <= 5.0" PHI*

-filter 进行条件过滤。

get_clocks *表示所有clock。

remove_clock [get_clocks CLKB*] 删除时钟定义。。

Specifying clock characteristic:

Latency包括clock source latency和clock network latency。中间点clock definition point。

uncertainty表示maximum difference在register的clock arrival signals。也叫做skew。

使用set_clock_latency -source对source latency进行model,对network latency的model分不同的阶段:

在post_layout之后,使用set_propagated_clock来进行model,在pre_layout,使用set_clock_latency来进行model。

set_clock_latency 1.5 -source -early [get_clocks CLK]

-rise/fall来指定latency在rising/falling edg。

-min/max指定一个range。

-late/early指定longest path as late path,shortest path as early path。

做setup check时,source clock做late version,destination clock做early version。

做hold check时,source clock做early version,destination clock做late version。

-source指定source latency,没有定义时表示network latency。

可以通过-dynamic 指定clock jitter的值

Intraclock Uncertainty:

在single clock上定义skew和jitter,需要指定一个clock,port,pin,

如果指定一个clock,表示所有这个clockdrive的sequential elements都会使用这个uncertainty,

如果指定一个port,pin,表示所有的fanout都会使用这个uncertainty。

针对setup和hold的check,uncertainty的值可以设置不同,-setup/-hold

setup check会被jitter和skew影响,hold只会被skew影响。

set_clock_uncertainty -setup 0.5 [get_clocks C2]

Interclock uncertainty:

-from表示start clock(launch reg),-to表示destination clock(capture reg)

setup check和hold check都会被jitter和skew影响。

set_clock_uncertainty -from C1 -to C2 -setup

set_clock_uncertainty -rise_from C1 -fall_to C2 0.5

-from和-to的属性会被严格执行,如果会出现-from建模capture reg的情况,需要在定义。

如果interclock uncertainty和intraclock uncertainty都被定义,inter的优先级较高。

set_clock_transition 0.64 -fall [get_clocks CLK1]

-fall/-rise,分别指定transition time。

-min/max,分别制定range。

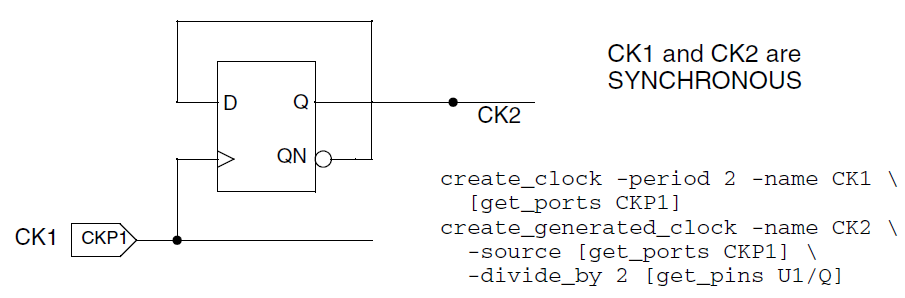

对于multiple clock的分析:

两个clock之间的关系可以是:synchronous,asynchronous,exclusive。

在没有其他设置时,如果存在一条path,launched by one clock,captured by other clock,PT会认为

这两个clock的关系是sync的,由create_clock定义的time zero为sync点,expands到两个clock时钟的

least common multiple,来进行同步和分析。

async clock,对于两个clock domain,clock edges可以发生在any time的时钟。

对于这样的async clock,launched by one clock,captured by other,PrimeTime不会检查timing path,

通过set_clock_groups -usync 命令设置之后,效果等同于设置false path。

Exclusive clock,没有interact的clock,only one clock is enabled at any given time。

set_clock_groups -logically_exclusive -group {CK1} -group {CK2}

当定义两个group时,表示两个group之间是exclusive的,在与第三个group之间是没有这个设置的。(CK1与CK2 exclusive)

set_clock_groups -logically_exclusive -group {CK1}

当只定义一个group时,表示该group与剩下的所有的clock都是这样的设置。(CK1与剩下的所有的clock都是exclusive的)

还有一种physically_exclusive的设置,主要用在PT SI分析crosstalk时。

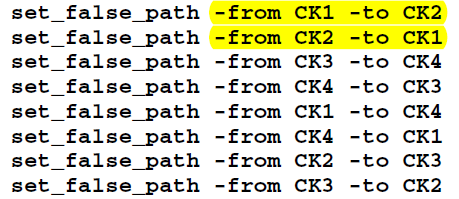

clock mux时的处理:

1)列出所有的false_path

2)使用set_case_analysis

![]()

3)使用disable_timing命令

![]()

4)set_clock_group命令

![]()

特例:

浙公网安备 33010602011771号

浙公网安备 33010602011771号