STA分析(三) cmos模型

CMOS集成电路的基本结构是以P型材料作为衬底(p-substrate),直接生成NMOS,

同时增加N肼(n-well),在其上制造PMOS。

增加两个bulk(P+,N+)防止非MOS管内的PN结反偏。

NMOS一般放在Pull-down结构中,PMOS一般放在Pull-up结构中。

NMOS与PMOS均采用增强型的类型,这样便于控制channel length。

Bulk端和Gate,Source,Drain通过metal层引出。

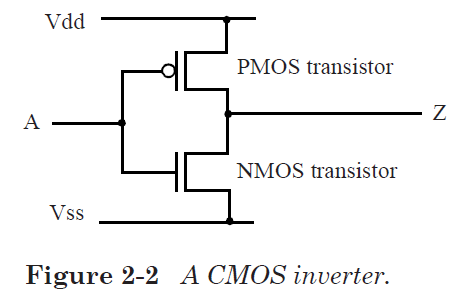

在基本的invert中,NMOS的Drain与PMOS的Source相连,NMOS的gate与PMOS的gate相连。NMOS在gate通入vdd时,Source与Drain相通,此时因为

NMOS处于Pull-down结构中,所以输出0,即反相器功能。而PMOS在gate通入vss时,才会导通。

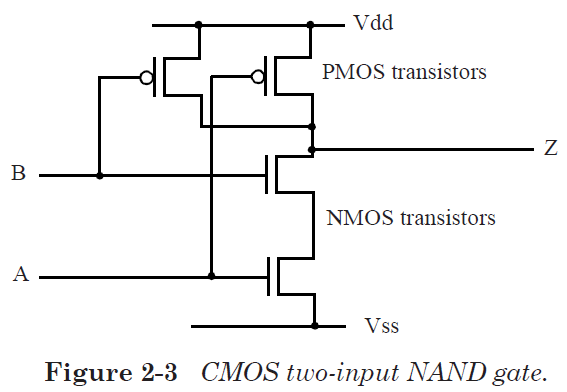

nand门,考虑低电平,即两个输入1时,才会输出零。所以NMOS串联,PMOS并联。

nor门,同样考虑低电平,只要有一个输入1时,就会输出零。所以NMOS并联,PMOS串联。

Standard Cells一般可以包括and,or,nand,nor,and-or-invert,or-and-invert,flip-flop。 xor(异或),xnor(异或非)

即功能时序都已定义好(functionality and timing are pre-characterized).

动态功耗发生在CMOS Cells的charging 和 discharging。静态功耗一般就是leakage的概念。

关于逻辑定义,一般以vdd和process为基础,来定义VIHmin和VILmax。vdd---VIHmin即为高电平,VILmax---0即为低电平。

CMOS Cells的建模:建模一般从RCL三个方面来说,一个cell的输出引脚的capacitance是三部分的和。cell的所有的input capacitance,wire segment

的capacitance,cell的output capacitance。 L一般指互联线之间的干扰。R一般是MOS管的等效电阻。

一般来说cell的设计,无论Pull-up还是Pull-down结构都具有相似的驱动能力(Drive Strength). Pull-up 或 Pull-down的resistance越

小,驱动能力越强,fanouts可以越多,capacitive load可以更大。

1)由RC时间常数决定的,一个cell的output,是指数型的增加或减少。

2)Propagation Delay,以invert为例来进行说明。输入到输出会有两个延时参数,output fall delay(Tf); output rise delay (Tr)

delay的测量通过,在lib文件中会来说明一个Threshold point。

input_threshold_pct_fall :50.0 output_threshold_pct_fall :50.0

input_threshold_pct_rise :50.0 output_threshold_pct_rise :50.0

3)slew rate:测量方式transition time。在lib文件中的说明。其中slew time就是30%---70%的时间。

slew_lower_threshold_pct_fall :30.0 slew_lower_threshold_pct_fall :30.0

slew_upper_threshold_pct_rise :70.0 slew_upper_threshold_pct_rise :70.0

4)Skew:数据或时钟两个信号之间的时序差。例如,Clock skew指时钟树中不同两个end point之间的时间差。包含在uncertainty中,

可以用set_clock_uncertainty来设置。

Clock latency指clock source到一个end point之间的时差。set_clock_latency来设置。

5)从source到destination总会有多个path,总会有一个max path,一个min path。timing check总会归结到这两条路径。

6)Operating Conditions:Process Voltage Temperature,PVT。Process越快,Delay越小。Voltage越大,Delay越小。如果不发

生Temperature inversion,Temperature越小,Delay越小。

三种典型的环境:WCS,TYP,BCS做后仿时,sdf文件会不同。

三种lib cells:LVT,Vt low, Switching Time Fast, Leakage High.

HVT,Vt high, Slow, Leakage Low. (应用最多)

浙公网安备 33010602011771号

浙公网安备 33010602011771号