《信息安全系统设计基础》家庭作业

《信息安全系统设计基础》家庭作业

4.49

在seq-full.hcl中,修改实现leave指令的控制逻辑块的HCL描述。

首先,leave等价的Y86代码序列为:

rrmovl %ebp,%esp

popl %ebp

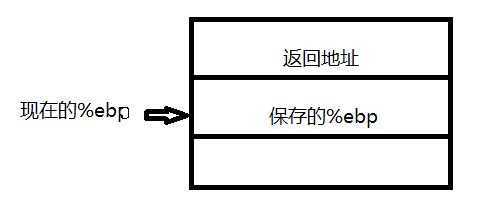

相应栈帧如图所示:

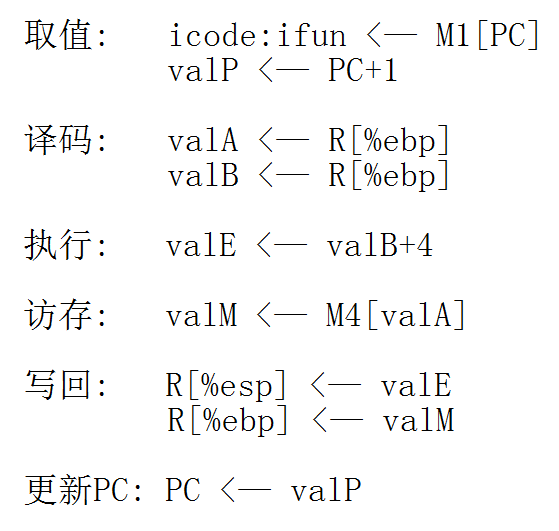

则实现这个指令所需要执行的计算为:

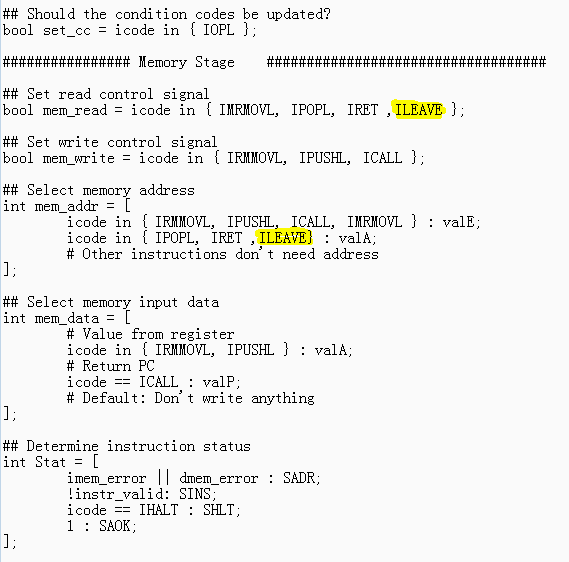

所以,在对seq-full.hcl的修改中,要将leave指令写入instr_valid,表明该指令为合法指令;在译码与写回阶段,对srcA添加leave指令对应于%ebp,对srcB添加leave指令对应于%ebp,dstE添加leave指令写回于%esp,dstM添加leave指令写回于%ebp;在执行阶段,需要对操作数A赋值为4,即对aluA添加leave指令对应+4,aluB添加leave指令对应valB(即%ebp);在访存阶段,只读控制信号men_read添加leave指令,地址men_addr添加leave指令对应于valA(即%ebp);在更新PC阶段无变化

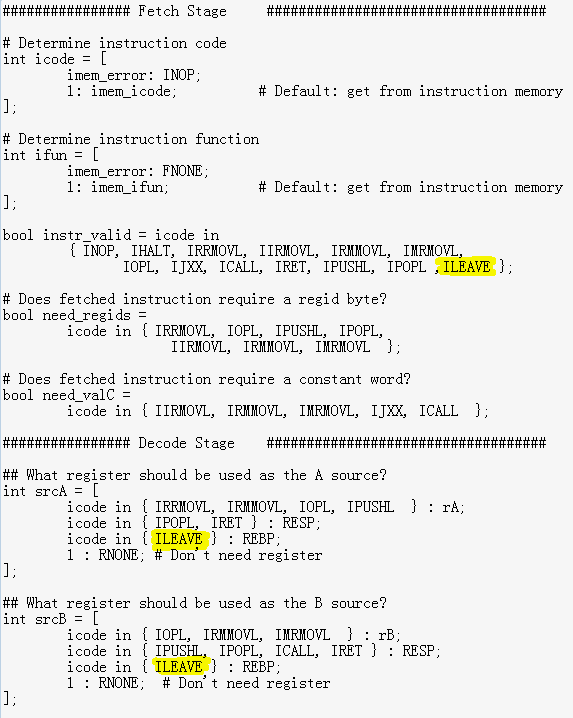

seq-full.hcl的修改后:

代码:

################ Fetch Stage ###################################

# Determine instruction code

int icode = [

imem_error: INOP;

1: imem_icode; # Default: get from instruction memory

];

# Determine instruction function

int ifun = [

imem_error: FNONE;

1: imem_ifun; # Default: get from instruction memory

];

bool instr_valid = icode in

{ INOP, IHALT, IRRMOVL, IIRMOVL, IRMMOVL, IMRMOVL,

IOPL, IJXX, ICALL, IRET, IPUSHL, IPOPL ,ILEAVE };

# Does fetched instruction require a regid byte?

bool need_regids =

icode in { IRRMOVL, IOPL, IPUSHL, IPOPL,

IIRMOVL, IRMMOVL, IMRMOVL };

# Does fetched instruction require a constant word?

bool need_valC =

icode in { IIRMOVL, IRMMOVL, IMRMOVL, IJXX, ICALL };

################ Decode Stage ###################################

## What register should be used as the A source?

int srcA = [

icode in { IRRMOVL, IRMMOVL, IOPL, IPUSHL } : rA;

icode in { IPOPL, IRET } : RESP;

icode in { ILEAVE } : REBP;

1 : RNONE; # Don't need register

];

## What register should be used as the B source?

int srcB = [

icode in { IOPL, IRMMOVL, IMRMOVL } : rB;

icode in { IPUSHL, IPOPL, ICALL, IRET } : RESP;

icode in { ILEAVE } : REBP;

1 : RNONE; # Don't need register

];

## What register should be used as the E destination?

int dstE = [

icode in { IRRMOVL } && Cnd : rB;

icode in { IIRMOVL, IOPL} : rB;

icode in { IPUSHL, IPOPL, ICALL, IRET ,ILEAVE} : RESP;

1 : RNONE; # Don't write any register

];

## What register should be used as the M destination?

int dstM = [

icode in { IMRMOVL, IPOPL } : rA;

icode in { ILEAVE } : REBP;

1 : RNONE; # Don't write any register

];

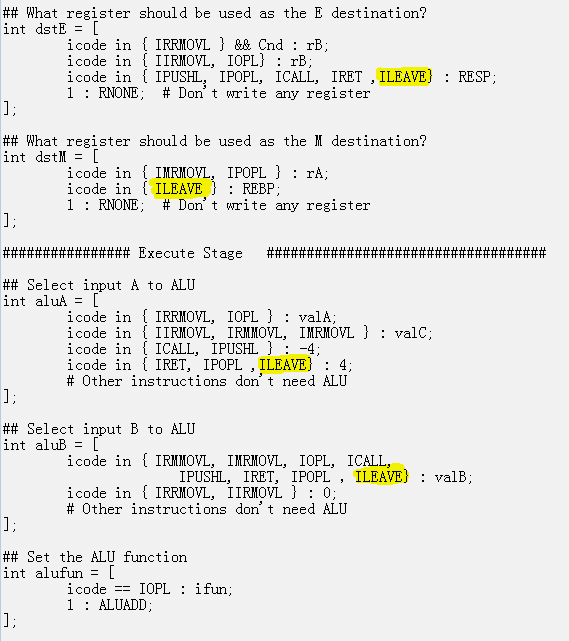

################ Execute Stage ###################################

## Select input A to ALU

int aluA = [

icode in { IRRMOVL, IOPL } : valA;

icode in { IIRMOVL, IRMMOVL, IMRMOVL } : valC;

icode in { ICALL, IPUSHL } : -4;

icode in { IRET, IPOPL ,ILEAVE} : 4;

# Other instructions don't need ALU

];

## Select input B to ALU

int aluB = [

icode in { IRMMOVL, IMRMOVL, IOPL, ICALL,

IPUSHL, IRET, IPOPL ,ILEAVE} : valB;

icode in { IRRMOVL, IIRMOVL } : 0;

# Other instructions don't need ALU

];

## Set the ALU function

int alufun = [

icode == IOPL : ifun;

1 : ALUADD;

];

## Should the condition codes be updated?

bool set_cc = icode in { IOPL };

################ Memory Stage ###################################

## Set read control signal

bool mem_read = icode in { IMRMOVL, IPOPL, IRET ,ILEAVE };

## Set write control signal

bool mem_write = icode in { IRMMOVL, IPUSHL, ICALL };

## Select memory address

int mem_addr = [

icode in { IRMMOVL, IPUSHL, ICALL, IMRMOVL } : valE;

icode in { IPOPL, IRET ,ILEAVE} : valA;

# Other instructions don't need address

];

## Select memory input data

int mem_data = [

# Value from register

icode in { IRMMOVL, IPUSHL } : valA;

# Return PC

icode == ICALL : valP;

# Default: Don't write anything

];

## Determine instruction status

int Stat = [

imem_error || dmem_error : SADR;

!instr_valid: SINS;

icode == IHALT : SHLT;

1 : SAOK;

];

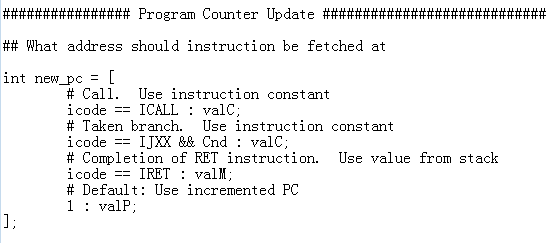

################ Program Counter Update ############################

## What address should instruction be fetched at

int new_pc = [

# Call. Use instruction constant

icode == ICALL : valC;

# Taken branch. Use instruction constant

icode == IJXX && Cnd : valC;

# Completion of RET instruction. Use value from stack

icode == IRET : valM;

# Default: Use incremented PC

1 : valP;

];

6.33

先计算出s、b、t,将地址解析成指引高速缓存的位置

6.34

组5意味着地址第4到第2位为“101”,观察4路组相联高速缓存索引5中 V 表示为“1”的行,里面的数据块即是可能命中的数据,8个存储器地址为 0x1314 0x1315 0x1316 0x1317 0x1794 0x1795 0x1796 0x1797