2017-2018-1 20155328 《信息安全系统设计基础》第九周学习总结

教材学习内容总结

-

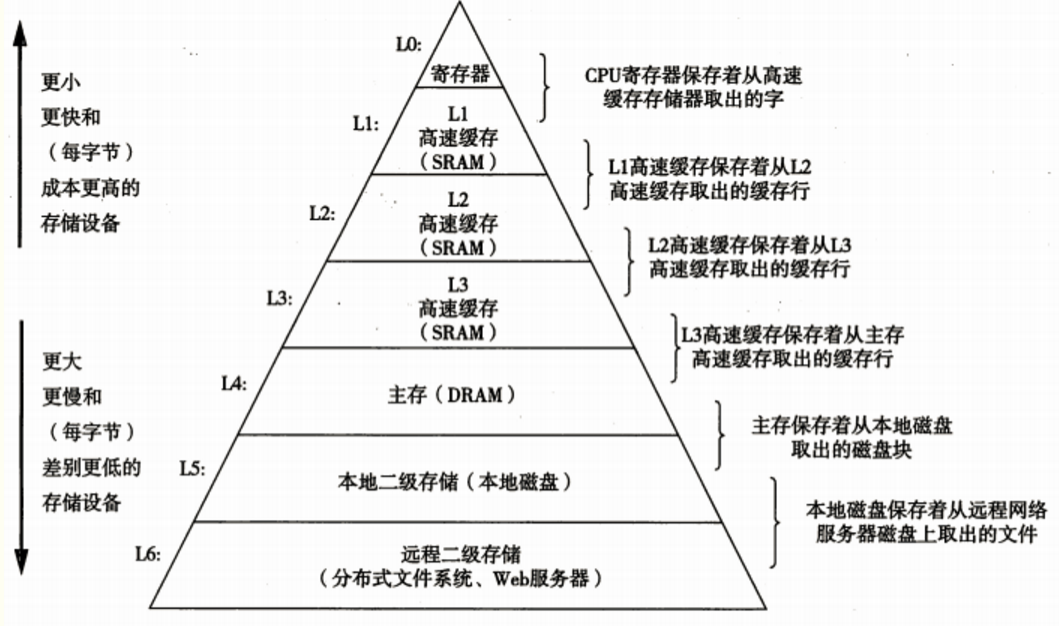

随机访问寄存器(RAM)分为静态随机访问寄存器(SRAM)和动态随机访问寄存器(DRAM)。静态RAM可以作为高速缓存寄存器,动态RAM可以用作主存以及图形系统的帧缓冲区。

-

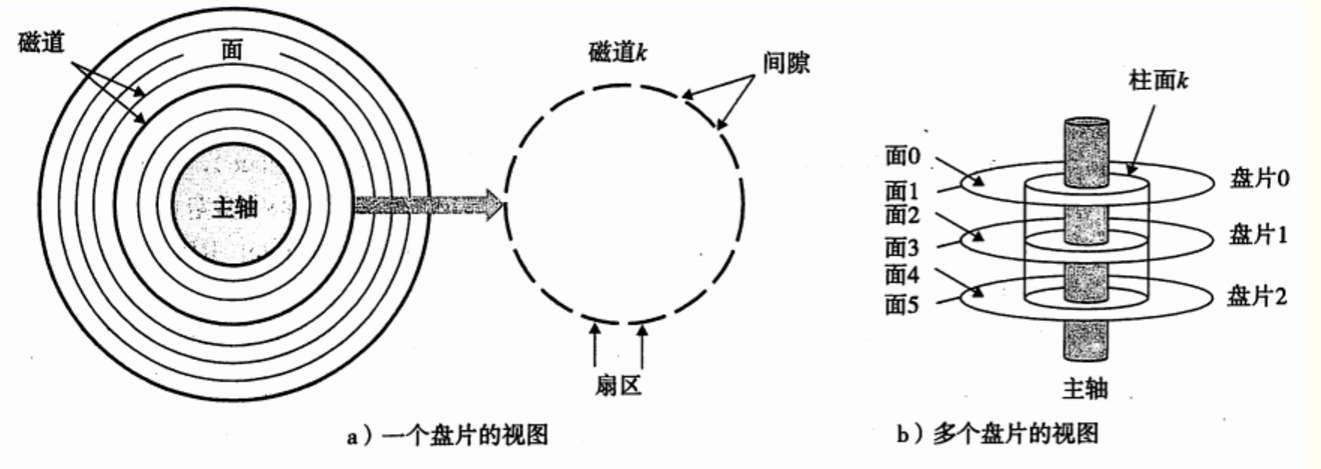

磁盘是用来保存大量数据的存储设备,能比基于RAM的存储器存更多的数据,但是读取数据的速度却远远低于基于RAM的存储器。是由盘片构成的。每个盘片上是由一组成为磁道的同心圆组成的。每个磁道被划分为一组扇区。扇区之间存在间隙。

-

一个计算机程序通常具有良好的局部性,也就是说,它们倾向于引用于其他最近引用过的数据项的数据项,或者最近引用过的数据项本身。局部性通常有两种不同的形式:时间局部性和空间局部性。

-

所有的现代计算机系统中都使用存储器结构层次来使得软件和硬件互相补充。一般而言,从高层往底层走,存储设备变得更慢、更便宜和更大。

-

早期计算机系统的存储结构只有三层:CPU寄存器、DRAM主存储器和磁盘存储。

-

储器系统的性能不是一个数字就能描述的。相反,它是一座时间和空间局部性的山,这座山的上升高度差别可以超过一个数量级。要是程序运行在山峰而不是低谷。

教材学习中的问题和解决过程

-

问题1:不太理解缓存命中的含义。

-

问题1解决方案:当程序需要第k+1层的某个数据对象d时,它首先在当前存储在第k层的一个块中查找d。如果d刚好缓存在第k层中,即为缓存命中。

-

问题2:传统DRAM的形象是怎样的?

-

问题2解决方案:w个DRAM单元(一个单元存储一个bit)形成一个supercell(如果DRAM芯片是一个矩阵,那么一个supercell就是一个矩阵元素)。d个supercell组成ab的矩阵形式,形成一个DRAM芯片,这样这块芯片有ab*w个bit(之所以d个supercell组成矩阵而不是线性数组的原因是为了降低芯片上地址引脚的数量。但是矩阵组织形式的缺点是要分2步发送地址:行+列,这增加了访问时间。多块DRAM芯片包装在存储器模块(memory module)中,这个memory module是柴刀主板的扩展槽上的。

-

问题3:如何访问主存?

-

问题3解决方案:数据流通过成为总线(bus)的共享电子电路在CPU和DRAM之间来来回回。

详细一点地说。

1)不同计算机系统对于总线有不同的设计,本书采用的是其中一种高级总线体系结构,具体结构见图6-6.因此,这里讲的CPU如何如何对main memory访问是基于这个总线体系结构的。

2)数据通过总线(此体系中有系统总线和存储器总线)在芯片之间(CPU--I/O桥--main memory)流动。

代码调试中的问题和解决过程

本周暂未遇到。

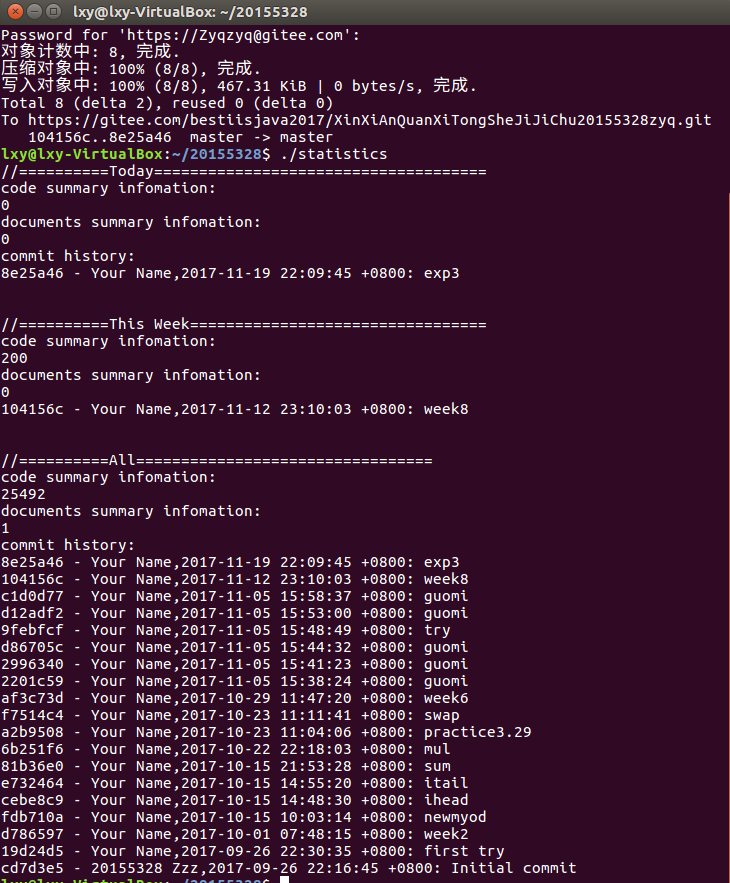

代码托管

上周考试错题总结

上周没有考试

结对及互评

点评模板:

- 博客中值得学习的或问题:

- xxx

- xxx

- ...

- 代码中值得学习的或问题:

- xxx

- xxx

- ...

- 其他

本周结对学习情况

- 结对学习内容

- 教材第六章

- ...

学习进度条

| 代码行数(新增/累积) | 博客量(新增/累积) | 学习时间(新增/累积) | 重要成长 | |

|---|---|---|---|---|

| 目标 | 5000行 | 30篇 | 400小时 | |

| 第一周 | 40/40 | 1/1 | 20/20 | |

| 第二周 | 40/40 | 1/2 | 18/38 | |

| 第四周 | 154/194 | 2/4 | 20/58 | |

| 第五周 | 48/242 | 2/6 | 20/78 | |

| 第六周 | 59/301 | 2/8 | 19/97 | |

| 第七周 | 354/655 | 2/9 | 18/115 | | |

| 第八周 | 455/1100 | 1/10 | 15/130 | |

| 第九周 | 200/1300 | 2/11 | 18/148 |

尝试一下记录「计划学习时间」和「实际学习时间」,到期末看看能不能改进自己的计划能力。这个工作学习中很重要,也很有用。

耗时估计的公式

:Y=X+X/N ,Y=X-X/N,训练次数多了,X、Y就接近了。

-

计划学习时间:20小时

-

实际学习时间:18小时

-

改进情况:

(有空多看看现代软件工程 课件

软件工程师能力自我评价表)