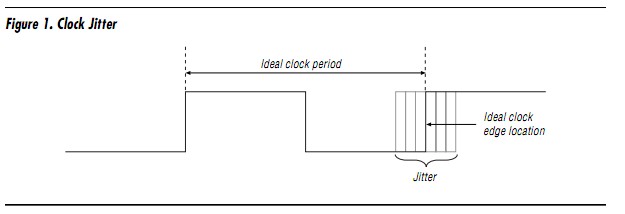

Clock Jitter

Clock jitter is the deviation from the ideal timing of clock transition events. Because such deviation can be detrimental to high-speed data transfer and can degrade performance, jitter must be kept to a minimum in a high-speed system.High-speed signaling is very sensitive to jitter. As signals toggle faster and faster, tighter restrictions fall on the signal transmitter and receiver. In many high-speed data applications, the clock edge must fall within a tight margin of time to capture data correctly. The more jitter in a system, the more often the clock edge will fall outside the margin. The frequency of clock edge deviations from the acceptable margin translates to the system’s bit error rate (BER). Figure 1 shows a schematic representation of clock jitter.

posted on 2010-08-29 22:22 Homography Matrix 阅读(1100) 评论(0) 收藏 举报

浙公网安备 33010602011771号

浙公网安备 33010602011771号