DDR3 DDR4 FPGA实现

基于7系列、virtex6等xilinx器件的MIG ip核设计DDR3/4读写控制器,以及基于arria 10器件的DDR4读写控制;DDR3/4的设计,设计的关键点是提高DDR3/4的访问效率,目前设计的性能可以达到DDR3/4理论带宽的80%左右;另一个设计关键点是可移植性高,以及用户接口简单,目前设计的控制器用户接口是4通道读写,类似于4对独立的FIFO访问,简单易用;

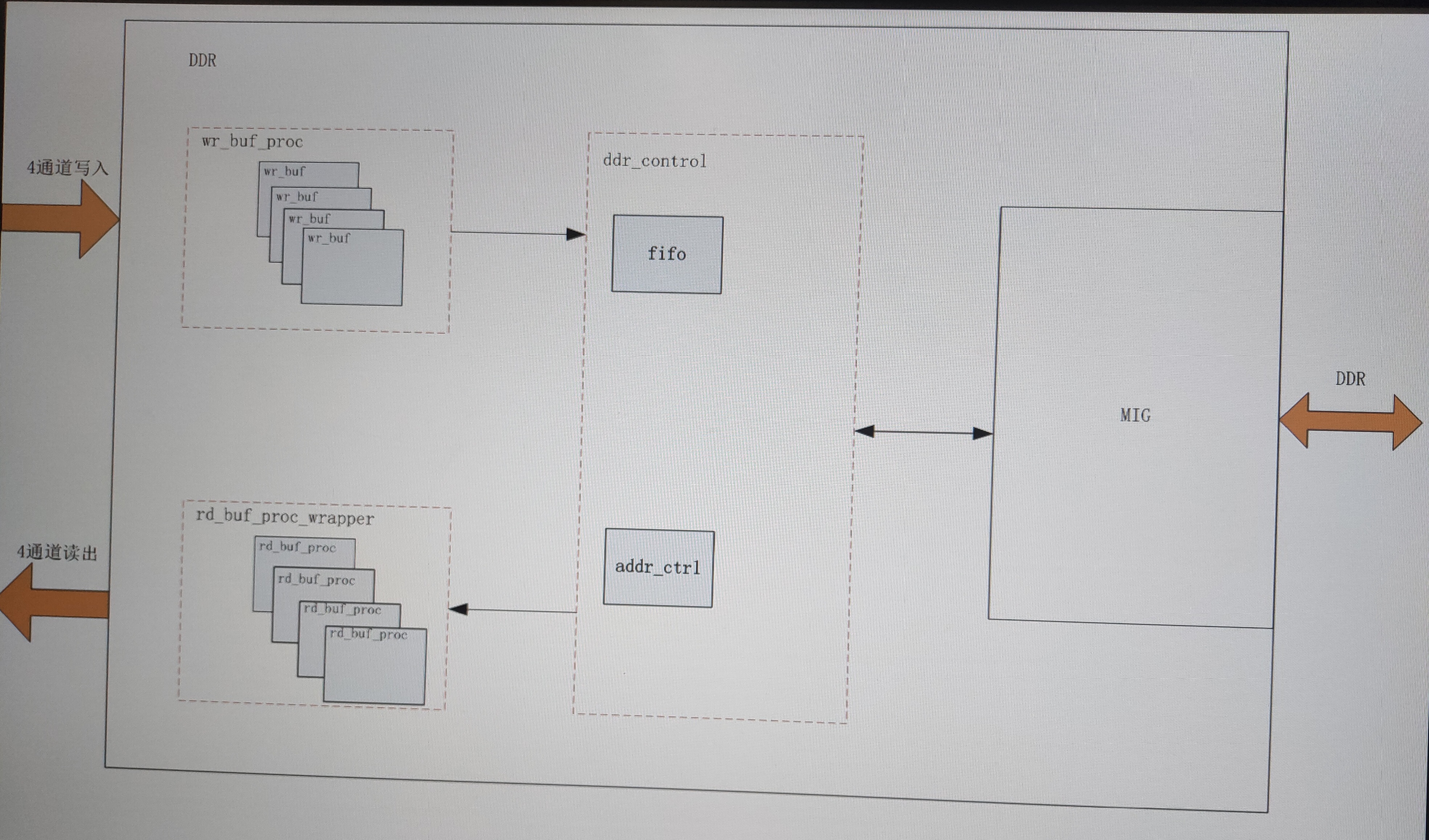

控制器框架图如下:

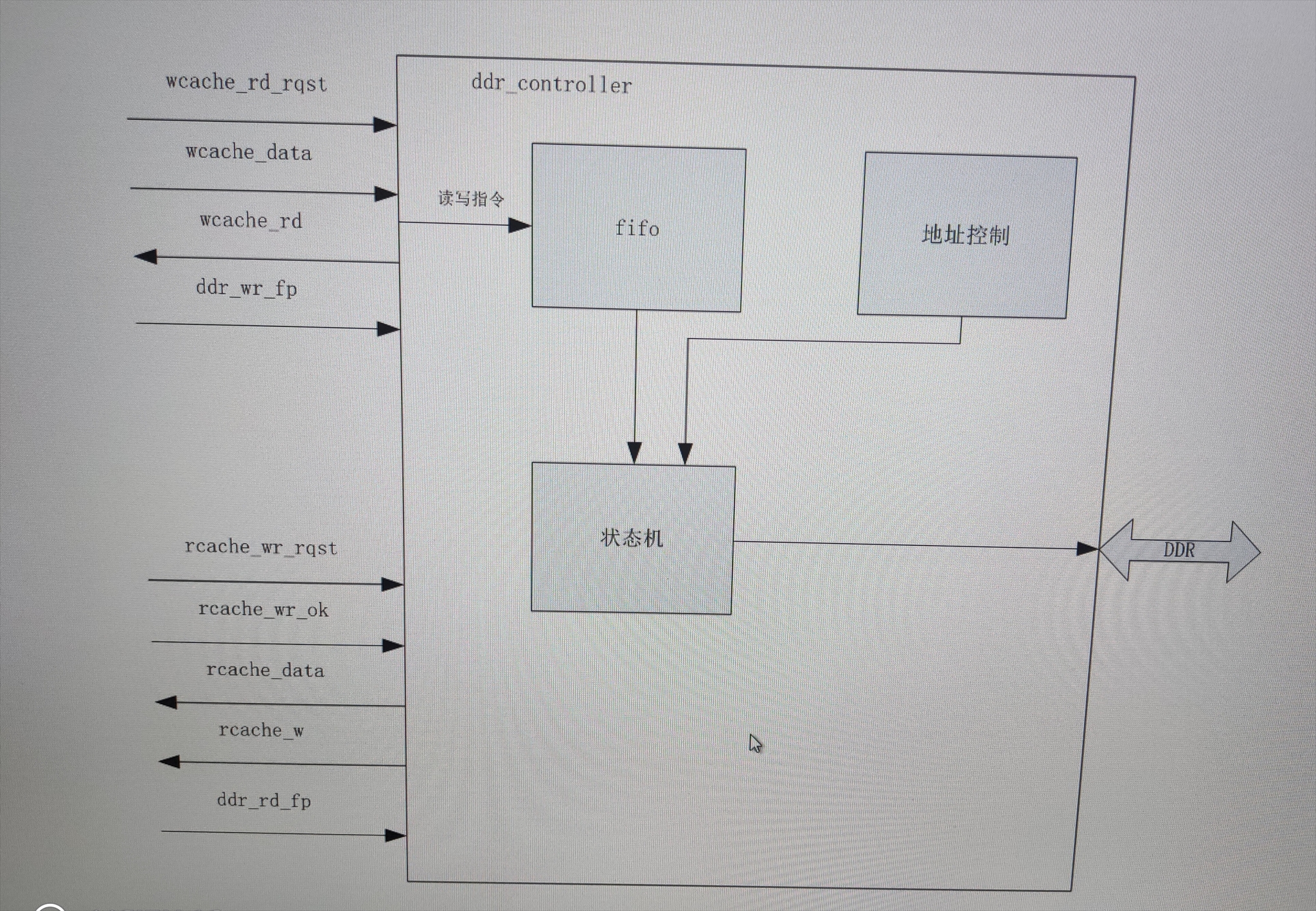

control模块实现框图:

用户接口:

如有DDR3/4相关方面的技术合作和交流,可联系我。

联系方式:495673622@qq.com